# S-8206Aシリーズ

# 1セル用バッテリー保護IC (セカンドプロテクト用)

www.ablic.com

© ABLIC Inc., 2015-2020 Rev.1.5 00

S-8206Aシリーズは、高精度電圧検出回路と遅延回路を内蔵したリチウムイオン / リチウムポリマー二次電池セカンドプロテクト用ICです。

### ■ 特長

· 高精度電圧検出回路

過充電検出電圧 3.500 V ~ 5.000 V (5 mVステップ) 精度±20 mV 過充電解除電圧 3.100 V ~ 4.950 V\*1 精度±50 mV

・検出遅延時間は内蔵回路のみで実現 (外付け容量は不要)

・出力論理 : アクティブ "H"、アクティブ "L"

・出力形態 : CMOS出力、Nchオープンドレイン出力

· 広動作温度範囲 : Ta = -40°C ~ +85°C

• 低消費電流

動作時 : 1.5  $\mu$ A typ., 3.0  $\mu$ A max. (Ta = +25°C)

・鉛フリー (Sn 100%)、ハロゲンフリー

\*1. 過充電解除電圧 = 過充電検出電圧 - 過充電ヒステリシス電圧 (過充電ヒステリシス電圧は、0.05 V ~ 0.4 Vの範囲内にて50 mVステップで選択可能)

#### ■ 用途

- ・リチウムイオン二次電池パック

- ・リチウムポリマー二次電池パック

## ■ パッケージ

- · SNT-6A

- · HSNT-6 (1212)

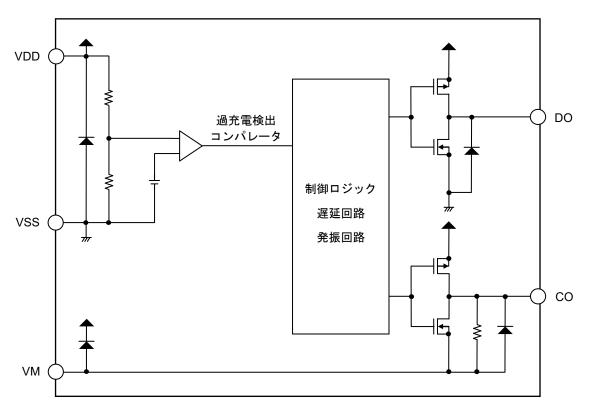

## ■ ブロック図

1. CMOS出力、アクティブ "H"

図1

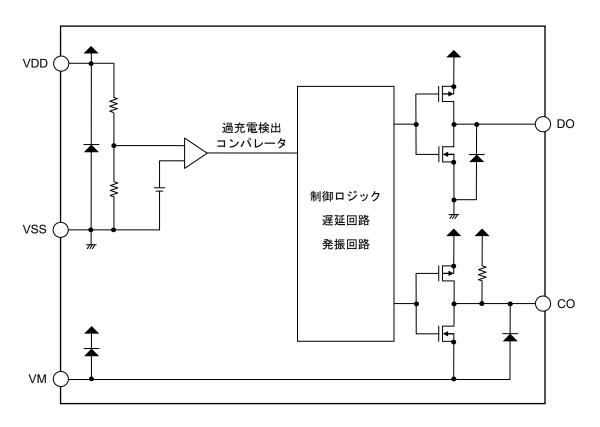

## 2. CMOS出力、アクティブ "L"

図2

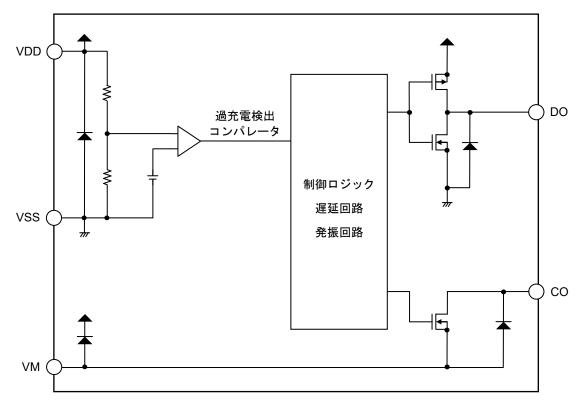

## 3. Nchオープンドレイン出力

図3

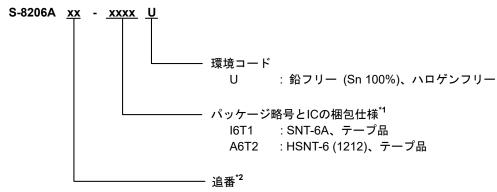

## ■ 品目コードの構成

## 1. 製品名

- AA~ZZまで順次設定

- \*1. テープ図面を参照してください。

- \*2. "3. 製品名リスト"を参照してください。

#### 2. パッケージ

#### 表1 パッケージ図面コード

| パッケージ名        | 外形寸法図面       | テープ図面        | リール図面        | ランド図面        |

|---------------|--------------|--------------|--------------|--------------|

| SNT-6A        | PG006-A-P-SD | PG006-A-C-SD | PG006-A-R-SD | PG006-A-L-SD |

| HSNT-6 (1212) | PM006-A-P-SD | PM006-A-C-SD | PM006-A-R-SD | PM006-A-L-SD |

#### 3. 製品名リスト

#### 3.1 SNT-6A

#### 表2

| 製品名             | 過充電検出電圧<br>[Vcu] | 過充電解除電圧<br>[V <sub>CL</sub> ] | 過充電検出遅延時間*1<br>[tcu] | 出力論理*²    | 出力形態 <sup>*3</sup> |

|-----------------|------------------|-------------------------------|----------------------|-----------|--------------------|

| S-8206AAA-I6T1U | 4.500 V          | 4.150 V                       | 2 s                  | アクティブ "H" | CMOS出力             |

| S-8206AAB-I6T1U | 4.550 V          | 4.200 V                       | 2 s                  | アクティブ "H" | CMOS出力             |

| S-8206AAC-I6T1U | 4.150 V          | 4.000 V                       | 2 s                  | アクティブ "L" | CMOS出力             |

| S-8206AAD-I6T1U | 4.250 V          | 4.100 V                       | 2 s                  | アクティブ "L" | CMOS出力             |

| S-8206AAE-I6T1U | 4.150 V          | 4.000 V                       | 2 s                  | アクティブ "H" | Nchオープンドレイン出力      |

| S-8206AAF-I6T1U | 4.250 V          | 4.100 V                       | 2 s                  | アクティブ "H" | Nchオープンドレイン出力      |

| S-8206AAG-I6T1U | 4.450 V          | 4.150 V                       | 2 s                  | アクティブ "H" | CMOS出力             |

| S-8206AAH-I6T1U | 4.400 V          | 4.100 V                       | 2 s                  | アクティブ "H" | CMOS出力             |

| S-8206AAI-I6T1U | 4.350 V          | 4.050 V                       | 2 s                  | アクティブ "H" | CMOS出力             |

| S-8206AAJ-I6T1U | 4.570 V          | 4.220 V                       | 2 s                  | アクティブ "H" | CMOS出力             |

| S-8206AAL-I6T1U | 4.600 V          | 4.250 V                       | 2 s                  | アクティブ "H" | CMOS出力             |

| S-8206AAR-I6T1U | 4.130 V          | 4.080 V                       | 2 s                  | アクティブ "L" | CMOS出力             |

\*1. 過充電検出遅延時間:1s,2s,4s \*2. 出力論理:"H"、アクティブ"L"

\*3. 出力形態: CMOS出力、Nchオープンドレイン出力

**備考** 上記以外の製品をご希望のときは、販売窓口までお問い合わせください。

#### 3. 2 HSNT-6 (1212)

#### 表3

| 製品名             | 過充電検出電圧<br>[Vcu] | 過充電解除電圧<br>[V <sub>CL</sub> ] | 過充電検出遅延時間*1<br>[tcu] | 出力論理*2    | 出力形態* <sup>3</sup> |

|-----------------|------------------|-------------------------------|----------------------|-----------|--------------------|

| S-8206AAA-A6T2U | 4.500 V          | 4.150 V                       | 2 s                  | アクティブ "H" | CMOS出力             |

| S-8206AAB-A6T2U | 4.550 V          | 4.200 V                       | 2 s                  | アクティブ "H" | CMOS出力             |

\*1. 過充電検出遅延時間:1s,2s,4s \*2. 出力論理:"H"、アクティブ"L"

\*3. 出力形態: CMOS出力、Nchオープンドレイン出力

備考 上記以外の製品をご希望のときは、販売窓口までお問い合わせください。

## ■ ピン配置図

#### 1. SNT-6A

図4

|      |      | 24.             |

|------|------|-----------------|

| 端子番号 | 端子記号 | 端子内容            |

| 1    | NC*1 | 無接続             |

| 2    | СО   | 充電制御用FETゲート接続端子 |

| 3    | DO   | テスト信号入力端子       |

| 4    | VSS  | 負電源入力端子         |

| 5    | VDD  | 正電源入力端子         |

| 6    | VM   | CO端子側負極電源端子     |

表4

\*1. NCは電気的にオープンを示します。 そのため、VDD端子またはVSS端子に接続しても問題ありません。

## 2. HSNT-6 (1212)

Top view

1 6 2 5 3 4

Bottom view

表5

| 端子番号 | 端子記 <del>号</del> | 端子内容            |

|------|------------------|-----------------|

| 1    | NC*2             | 無接続             |

| 2    | СО               | 充電制御用FETゲート接続端子 |

| 3    | DO               | テスト信号入力端子       |

| 4    | VSS              | 負電源入力端子         |

| 5    | VDD              | 正電源入力端子         |

| 6    | VM               | CO端子側負極電源端子     |

図5

- \*1. 網掛け部分の裏面放熱板は、基板に接続し電位をオープンまたはVDDとしてください。ただし、電極としての機能には使用しないでください。

- \*2. NCは電気的にオープンを示します。 そのため、VDD端子またはVSS端子に接続しても問題ありません。

## ■ 絶対最大定格

表6

(特記なき場合: Ta = +25°C)

| 項目           |               | 記号               | 適用端子 | 絶対最大定格                           | 単位 |

|--------------|---------------|------------------|------|----------------------------------|----|

| VDD端子 – VSS端 | 子間入力電圧        | V <sub>DS</sub>  | VDD  | $V_{SS} - 0.3 \sim V_{SS} + 6$   | V  |

| VM入力端子電圧     |               | V <sub>VM</sub>  | VM   | $V_{DD} - 28 \sim V_{DD} + 0.3$  | V  |

| DO入力端子電圧     | DO入力端子電圧      |                  | DO   | $V_{SS} - 0.3 \sim V_{DD} + 0.3$ | V  |

| CO出力端子電圧     | CMOS出力        | V <sub>CO</sub>  | СО   | $V_{VM} - 0.3 \sim V_{DD} + 0.3$ | V  |

| しし山力端丁电圧     | Nchオープンドレイン出力 | VCO              | CO   | $V_{VM} - 0.3 \sim V_{VM} + 28$  | V  |

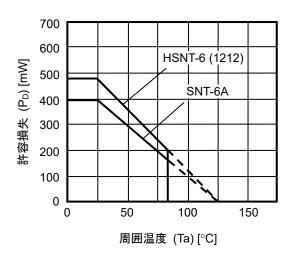

| 】<br>許容損失    | SNT-6A        |                  | _    | 400*1                            | mW |

| 计合供人         | HSNT-6 (1212) | P <sub>D</sub>   | _    | 480* <sup>1</sup>                | mW |

| 動作周囲温度       |               | Topr             | _    | <b>−40 ~ +85</b>                 | °C |

| 保存温度         |               | T <sub>stg</sub> | _    | <b>−55 ~ +125</b>                | °C |

## \*1. 基板実装時

[実装基板]

(1) 基板サイズ : 114.3 mm×76.2 mm×t1.6 mm(2) 名称 : JEDEC STANDARD51-7

注意 絶対最大定格とは、どのような条件下でも越えてはならない定格値です。万一この定格値を越えると、製品の劣化などの物理的な損傷を与える可能性があります。

図6 パッケージ許容損失 (基板実装時)

## ■ 電気的特性

1.  $Ta = +25^{\circ}C$

表7

(特記なき場合: Ta = +25°C)

|                   |                   |                                                |                             |      | (1寸10/4) (2/2017)       | . тч | 1200)    |

|-------------------|-------------------|------------------------------------------------|-----------------------------|------|-------------------------|------|----------|

| 項目                | 記号                | 条件                                             | Min.                        | Тур. | Max.                    | 単位   | 測定<br>回路 |

| 検出電圧              |                   |                                                |                             |      |                         |      |          |

| <b>37.</b> 本面於山南丘 | V                 | _                                              | V <sub>CU</sub> - 0.020     | Vcu  | V <sub>CU</sub> + 0.020 | V    | 1        |

| 過充電検出電圧           | Vcu               | $Ta = -10^{\circ}C \sim +60^{\circ}C^{*1}$     | $V_{\text{CU}}-0.025$       | Vcu  | V <sub>CU</sub> + 0.025 | V    | 1        |

| 過充電解除電圧           | VcL               | -                                              | V <sub>CL</sub> – 0.050     | VcL  | V <sub>CL</sub> + 0.050 | V    | 1        |

| 入力電圧              | •                 |                                                |                             | •    |                         |      |          |

| VDD端子 – VSS端子間    | VDSOP             |                                                | 1.5                         |      | 6.0                     | V    |          |

| 動作電圧              | <b>V</b> D50P     | _                                              | 1.5                         |      | 0.0                     | v    |          |

| 入力電流              |                   |                                                |                             |      |                         |      |          |

| 動作時消費電流           | IOPE              | $V_{DD} = 3.4 \text{ V}, V_{VM} = 0 \text{ V}$ | ı                           | 1.5  | 3.0                     | μΑ   | 2        |

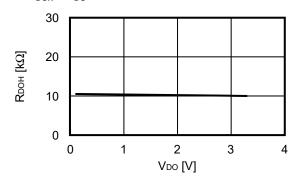

| 出力抵抗              |                   |                                                |                             |      |                         |      |          |

| CO端子抵抗 "H" 1      | R <sub>COH1</sub> | CMOS出力                                         | 5                           | 10   | 20                      | kΩ   | 3        |

| CO端子抵抗 "L" 1      | R <sub>COL1</sub> | _                                              | 5                           | 10   | 20                      | kΩ   | 3        |

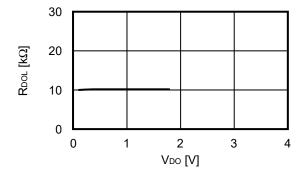

| DO端子抵抗 "H"        | Rоон              | _                                              | 5                           | 10   | 20                      | kΩ   | 3        |

| DO端子抵抗 "L"        | RDOL              | _                                              | 5                           | 10   | 20                      | kΩ   | 3        |

| CO端子抵抗 "H" 2      | R <sub>COH2</sub> | CMOS出力、アクティブ "L"                               | 1                           | 4    | _                       | МΩ   | 3        |

| CO端子抵抗 "L" 2      | R <sub>COL2</sub> | CMOS出力、アクティブ "H"                               | 1                           | 4    | _                       | МΩ   | 3        |

| 出力電流              |                   |                                                |                             |      |                         |      |          |

| 端子リーク電流 "L"       | Icoll             | Ncnオープンドレイン出力                                  |                             | _    | 0.1                     | μΑ   | 3        |

| 遅延時間              |                   |                                                |                             |      |                         |      |          |

| 過充電検出遅延時間         | tcu               | _                                              | $t_{\text{CU}}\!	imes\!0.7$ | tcu  | t <sub>CU</sub> × 1.3   | _    | 4        |

|                   |                   |                                                |                             |      |                         |      |          |

<sup>\*1.</sup> 高温および低温での選別はしておりませんので、この温度範囲での規格は設計保証とします。

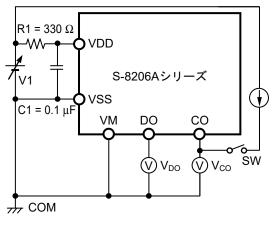

#### ■ 測定回路

- 注意 1. 特に記述していない場合のCO端子の出力電圧 ( $V_{co}$ ) の "H", "L" の判定は、 $N_{ch}$  FETのしきい値電圧 (1.0 V) とします。このとき、 $CO端子はV_{VM}$ 基準で判定してください。

- 2. Nchオープンドレイン出力はSWをON、CMOS出力はOFFに設定してください。

#### 1. 過充電検出電圧、過充電解除電圧

(測定回路1)

#### 1.1 アクティブ "H"

V1 = 3.4 Vに設定した状態からV1を徐々に上げ、 $V_{CO}$  = "L"  $\rightarrow$  "H" となるV1の電圧を過充電検出電圧 ( $V_{CL}$ ) とします。その後、V1を徐々に下げ、 $V_{CO}$  = "H"  $\rightarrow$  "L" となるV1の電圧を過充電解除電圧 ( $V_{CL}$ ) とします。 $V_{CL}$  と $V_{CL}$ との差を過充電ヒステリシス電圧 ( $V_{HC}$ ) とします。

#### 1.2 アクティブ "L"

V1 = 3.4 Vに設定した状態からV1を徐々に上げ、 $V_{CO}$  = "H"  $\rightarrow$  "L" となるV1の電圧を過充電検出電圧 ( $V_{CL}$ ) とします。その後、V1を徐々に下げ、 $V_{CO}$  = "L"  $\rightarrow$  "H" となるV1の電圧を過充電解除電圧 ( $V_{CL}$ ) とします。 $V_{CL}$  と $V_{CL}$ との差を過充電ヒステリシス電圧 ( $V_{HC}$ ) とします。

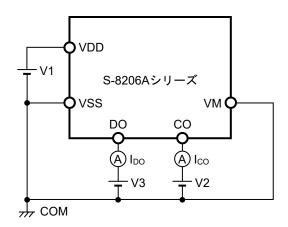

#### 2. 動作時消費電流

(測定回路2)

V1 = 3.4 Vに設定した状態において、VDD端子に流れる電流(IDD)を動作時消費電流(IOPE)とします。

#### 3. CO端子抵抗 "H" 1 (CMOS出力)

(測定回路3)

#### 3.1 アクティブ "H"

V1 = 5.1 V,  $V2 = 4.7 \text{ VIC設定した状態において、VDD端子 - CO端子間抵抗をCO端子抵抗 "H" 1 (RCOH1) とします。$

#### 3.2 アクティブ "L"

V1 = 3.4 V,  $V2 = 3.0 \text{ VIC設定した状態において、VDD端子 - CO端子間抵抗をCO端子抵抗 "H" 1 (RCOH1) とします。$

#### 4. CO端子抵抗 "L" 1

(測定回路3)

#### 4.1 アクティブ "H"

V1 = 3.4 V, V2 = 0.4 Vに設定した状態において、VM端子 – CO端子間抵抗をCO端子抵抗 "L" 1 (R<sub>COL1</sub>) とします。

#### 4.2 アクティブ "L"

V1 = 5.1 V, V2 = 0.4 Vに設定した状態において、VM端子 – CO端子間抵抗をCO端子抵抗 "L" 1 (RcoL1) とします。

#### 5. DO端子抵抗 "H"

(測定回路3)

V1 = 3.4 V, V3 = 3.0 Vに設定した状態において、VDD端子 – DO端子間抵抗をDO端子抵抗 "H" (RDOH) とします。

#### 6. DO端子抵抗 "L"

(測定回路3)

V1 = 1.8 V, V3 = 0.4 Vに設定した状態において、VSS端子 – DO端子間抵抗をDO端子抵抗 "L" (RDOL) とします。

7. CO端子抵抗 "H" 2 (CMOS出力、アクティブ "L") (測定回路3)

V1 = 5.1 V, V2 = 0 Vに設定した状態において、VDD端子 – CO端子間抵抗をCO端子抵抗 "H" 2 (RcoH2) とします。

8. CO端子抵抗 "L" 2 (CMOS出力、アクティブ "H") (測定回路3)

V1 = 5.1 V, V2 = 5.1 Vに設定した状態において、VM端子 - CO端子間抵抗をCO端子抵抗 "L" 2 (Rcol2) とします。

## 9. CO端子リーク電流 "L" (Nchオープンドレイン出力) (測定回路3)

9.1 アクティブ "H"

V1 = 5.1 V, V2 = 28 Vに設定した状態において、CO端子に流れる電流 (Ico) をCO端子リーク電流 "L" (Icoll) とします。

9.2 アクティブ "L"

V1 = 3.4 V, V2 = 28 Vに設定した状態において、CO端子に流れる電流 (Ico) をCO端子リーク電流 "L" (Icoll) とします。

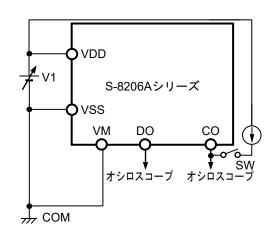

#### 10. 過充電検出遅延時間

(測定回路4)

10.1 アクティブ "H"

V1 = 3.4 Vに設定した状態からV1を上昇させ、V1が $V_{CU}$ を上回ってから $V_{CO}$  = "H" となるまでの時間を過充電検出遅延時間 ( $t_{CU}$ ) とします。

10.2 アクティブ "L"

V1 = 3.4 Vに設定した状態からV1を上昇させ、V1が $V_{CU}$ を上回ってから $V_{CO}$  = "L" となるまでの時間を過充電検出遅延時間 ( $t_{CU}$ ) とします。

図7 測定回路1

図8 測定回路2

図9 測定回路3

図10 測定回路4

## ■ 動作説明

備者 "■ バッテリー保護ICの接続例" を参照してください。

#### 1. 過充電検出状態

S-8206Aシリーズは、VDD端子 – VSS端子間に接続された電池電圧を監視し、過充電を検出します。通常状態の電池電圧が充電中に過充電検出電圧 (Vcu) を越え、その状態を過充電検出遅延時間 (tcu) 以上保持した場合、CO端子から過充電検出信号を出力します。この状態を過充電状態と言います。CO端子にFETを接続することにより、充電制御およびセカンドプロテクトが可能です。

#### 2. テストモード

S-8206Aシリーズは、DO端子を外部から強制的にVss電位にすることでtcuを短縮できます。DO端子を外部から強制的にVss電位にした場合、tcuが約1/64になります。

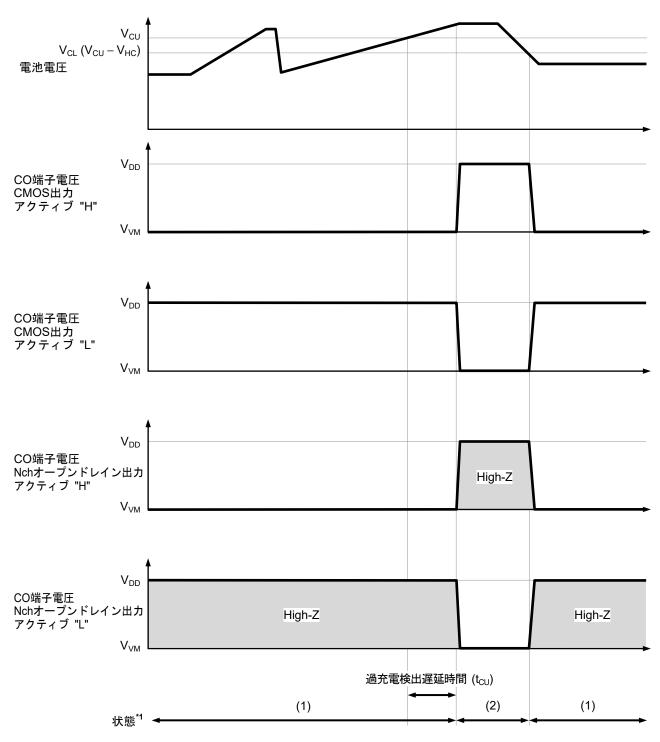

## ■ タイミングチャート

## 1. 過充電検出

\*1. (1): 通常状態 (2): 過充電状態

図11

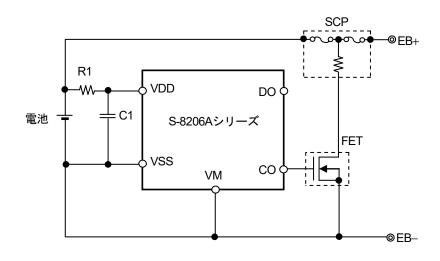

## ■ バッテリー保護ICの接続例

CMOS出力、アクティブ "H" の製品を使用した場合の接続例を**図12**に示します。

図12

表8 外付け部品定数

| 記号  | 部品             | 目的               | Min.     | Тур.   | Max.   | 備考 |

|-----|----------------|------------------|----------|--------|--------|----|

| FET | Nch<br>MOS FET | 充電制御             | _        | -      | -      | _  |

| R1  | 抵抗             | ESD対策、<br>電源変動対策 | 150 Ω    | 330 Ω  | 1 kΩ   | -  |

| C1  | 容量             | 電源変動対策           | 0.068 μF | 0.1 μF | 1.0 μF | _  |

#### 注意 1. 定数は予告なく変更することがあります。

2. 接続例以外の回路においては、動作確認されていません。また、接続例および定数は、動作を保証するものではありません。実際のアプリケーションで十分な評価の上、定数を設定してください。

#### 【SCPに関するお問い合わせ先】

デクセリアルズ株式会社 グローバルマーケティング本部 〒141-0032 東京都品川区大崎 1-11-2 ゲートシティ大崎イーストタワー8 階 TEL 03-5435-3946 お問い合わせ http://www.dexerials.jp/

## ■ 注意事項

- ・IC内での損失がパッケージの許容損失を越えないように、入出力電圧、負荷電流の使用条件に注意してください。

- ・本ICは静電気に対する保護回路が内蔵されていますが、保護回路の性能を越える過大静電気がICに印加されないようにしてください。

- ・弊社ICを使用して製品を作る場合には、その製品での当ICの使い方や製品の仕様また、出荷先の国などによって当ICを含めた製品が特許に抵触した場合、その責任は負いかねます。

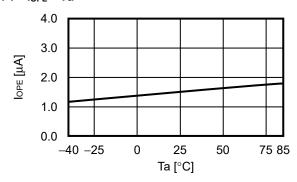

# ■ 諸特性データ (Typicalデータ)

## 1. 消費電流

1. 1 I<sub>OPE</sub> – Ta

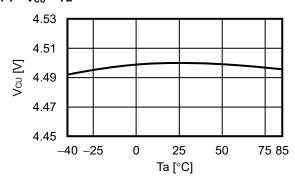

## 2. 検出電圧

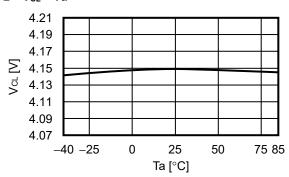

2. 1 V<sub>CU</sub> – Ta

2. 2 V<sub>CL</sub> – Ta

## 3. 遅延時間

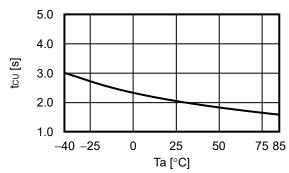

3. 1  $t_{CU} - Ta$

## 4. 出力抵抗

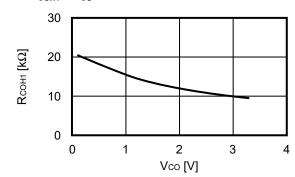

## 4. 1 RCOH1 - VCO

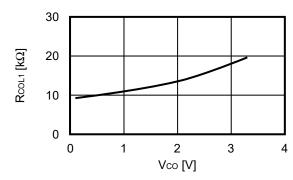

## 4. 2 Rcol1 - Vco

#### 4. 3 R<sub>DOH</sub> - V<sub>DO</sub>

## $4.~4~~R_{DOL}-V_{DO}$

## ■ マーキング仕様

## 1. SNT-6A

Top view

(1)~(3) : 製品略号 (製品名と製品略号の対照表を参照)

(4)~(6) : ロットナンバー

#### 製品名と製品略号の対照表

| 製品名             | 1   | 製品略号 | -   |

|-----------------|-----|------|-----|

| <b>妥</b> 帕石     | (1) | (2)  | (3) |

| S-8206AAA-I6T1U | J   | N    | Α   |

| S-8206AAB-I6T1U | J   | N    | В   |

| S-8206AAC-I6T1U | J   | N    | С   |

| S-8206AAD-I6T1U | J   | N    | D   |

| S-8206AAE-I6T1U | J   | N    | Е   |

| S-8206AAF-I6T1U | J   | N    | F   |

| S-8206AAG-I6T1U | J   | N    | G   |

| S-8206AAH-I6T1U | J   | N    | Н   |

| S-8206AAI-I6T1U | J   | N    | - 1 |

| S-8206AAJ-I6T1U | J   | N    | J   |

| S-8206AAL-I6T1U | J   | Ν    | L   |

| S-8206AAR-I6T1U | J   | N    | R   |

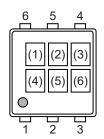

#### 2. HSNT-6 (1212)

Top view

(1)~(3) : 製品略号 (製品名と製品略号の対照表を参照)

(4), (5) : ロットナンバー

#### 製品名と製品略号の対照表

|                 |     | 製品略号    |     |

|-----------------|-----|---------|-----|

| 製品名             | :   | 表 四 町 ケ |     |

| ※ 四位            | (1) | (2)     | (3) |

| S-8206AAA-A6T2U | J   | N       | Α   |

| S-8206AAB-A6T2U | J   | N       | В   |

# No. PG006-A-P-SD-2.1

| TITLE      | SNT-6A-A-PKG Dimensions |  |

|------------|-------------------------|--|

| No.        | PG006-A-P-SD-2.1        |  |

| ANGLE      | $\bigoplus$             |  |

| UNIT       | mm                      |  |

|            |                         |  |

|            |                         |  |

|            |                         |  |

| ABLIC Inc. |                         |  |

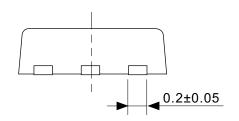

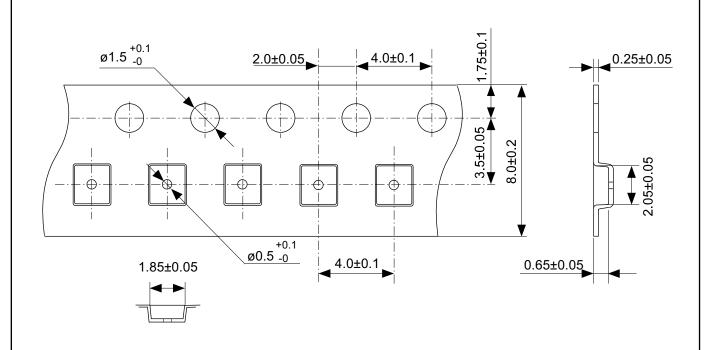

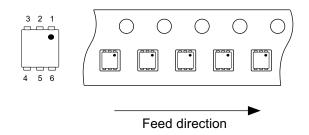

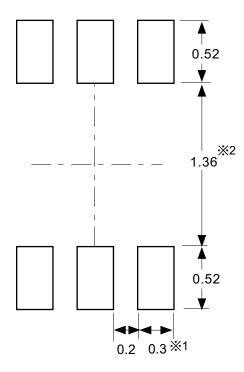

## No. PG006-A-C-SD-2.0

| TITLE      | SNT-6A-A-Carrier Tape |  |

|------------|-----------------------|--|

| No.        | PG006-A-C-SD-2.0      |  |

| ANGLE      |                       |  |

| UNIT       | mm                    |  |

|            |                       |  |

|            |                       |  |

|            |                       |  |

| ABLIC Inc. |                       |  |

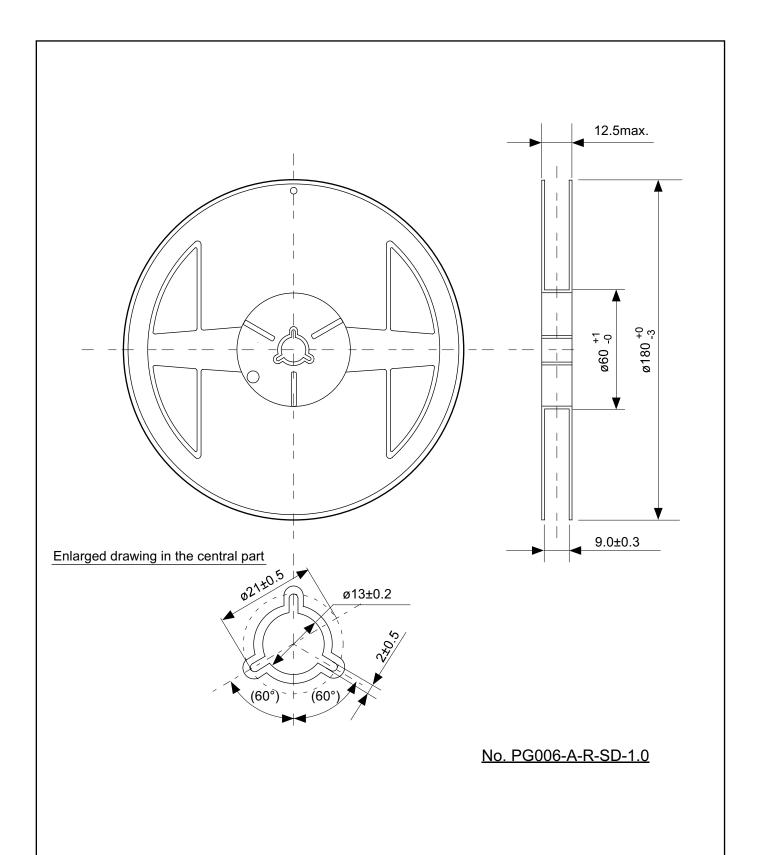

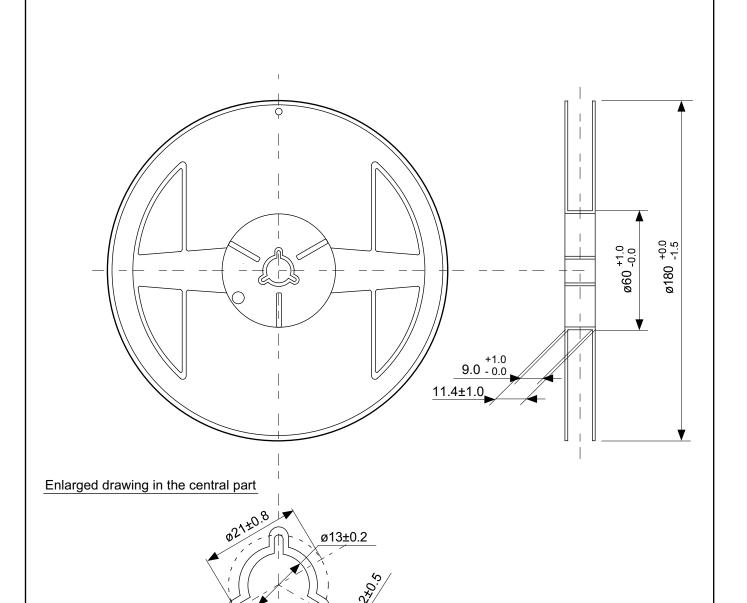

| TITLE      | SNT-6A-A-Reel    |      |       |

|------------|------------------|------|-------|

| No.        | PG006-A-R-SD-1.0 |      |       |

| ANGLE      |                  | QTY. | 5,000 |

| UNIT       | mm               |      |       |

|            |                  |      |       |

|            |                  |      |       |

|            |                  |      |       |

| ABLIC Inc. |                  |      |       |

%1. ランドパターンの幅に注意してください (0.25 mm min. / 0.30 mm typ.)。 %2. パッケージ中央にランドパターンを広げないでください (1.30 mm ~ 1.40 mm)。

- 注意 1. パッケージのモールド樹脂下にシルク印刷やハンダ印刷などしないでください。

- 2. パッケージ下の配線上のソルダーレジストなどの厚みをランドパターン表面から0.03 mm 以下にしてください。

- 3. マスク開口サイズと開口位置はランドパターンと合わせてください。

- 4. 詳細は "SNTパッケージ活用の手引き"を参照してください。

- ※1. Pay attention to the land pattern width (0.25 mm min. / 0.30 mm typ.).

- ※2. Do not widen the land pattern to the center of the package (1.30 mm ~ 1.40 mm).

- Caution 1. Do not do silkscreen printing and solder printing under the mold resin of the package.

- 2. The thickness of the solder resist on the wire pattern under the package should be 0.03 mm or less from the land pattern surface.

- 3. Match the mask aperture size and aperture position with the land pattern.

- 4. Refer to "SNT Package User's Guide" for details.

- ※1. 请注意焊盘模式的宽度 (0.25 mm min. / 0.30 mm typ.)。

- ※2. 请勿向封装中间扩展焊盘模式 (1.30 mm ~ 1.40 mm)。

- 注意 1. 请勿在树脂型封装的下面印刷丝网、焊锡。

- 2. 在封装下、布线上的阻焊膜厚度 (从焊盘模式表面起) 请控制在 0.03 mm 以下。

- 3. 钢网的开口尺寸和开口位置请与焊盘模式对齐。

- 4. 详细内容请参阅 "SNT 封装的应用指南"。

No. PG006-A-L-SD-4.1

| TITLE     | SNT-6A-A<br>-Land Recommendation |  |

|-----------|----------------------------------|--|

| No.       | PG006-A-L-SD-4.1                 |  |

| ANGLE     |                                  |  |

| UNIT      | mm                               |  |

|           |                                  |  |

|           |                                  |  |

|           |                                  |  |

| ARLIC Inc |                                  |  |

ABLIC Inc.

The heat sink of back side has different electric potential depending on the product.

Confirm specifications of each product.

Do not use it as the function of electrode.

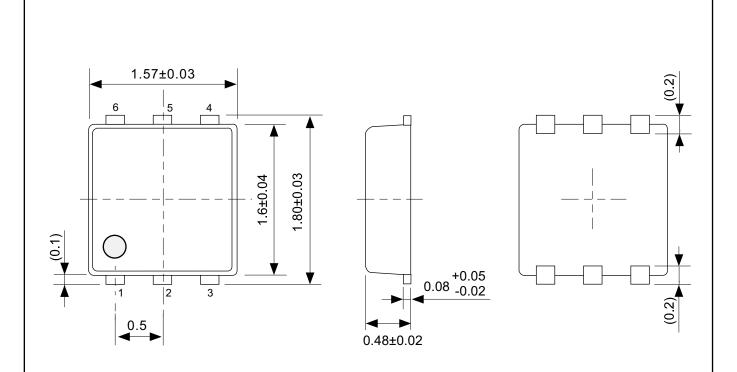

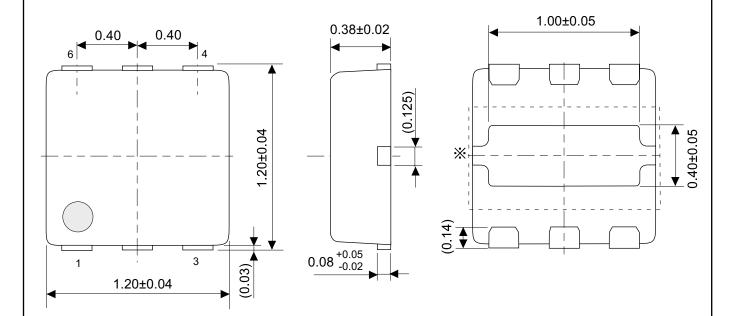

## No. PM006-A-P-SD-1.1

| TITLE        | HSNT-6-B-PKG Dimensions |

|--------------|-------------------------|

| No.          | PM006-A-P-SD-1.1        |

| ANGLE        | <b>\$</b>               |

| UNIT         | mm                      |

|              |                         |

|              |                         |

|              |                         |

| ABLIC Inc.   |                         |

| 7.22.0 1110. |                         |

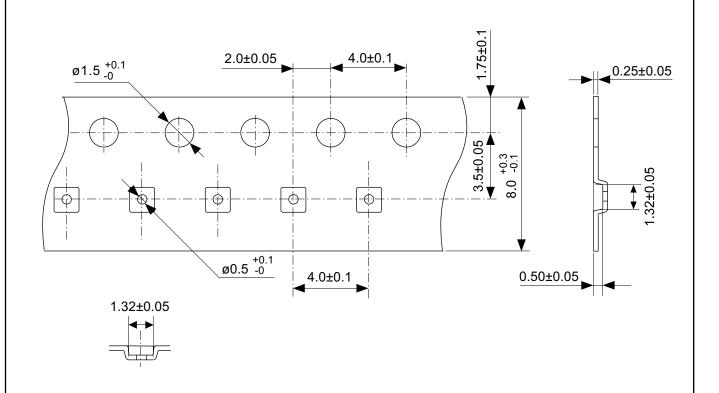

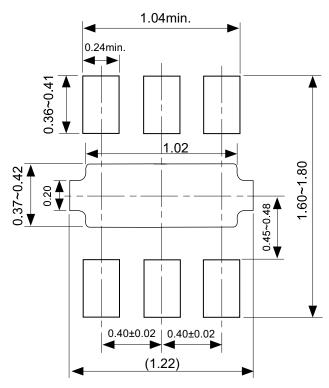

# No. PM006-A-C-SD-2.0

| TITLE      | HSNT-6-B-Carrier Tape |  |

|------------|-----------------------|--|

| No.        | PM006-A-C-SD-2.0      |  |

| ANGLE      |                       |  |

| UNIT       | mm                    |  |

|            |                       |  |

|            |                       |  |

|            |                       |  |

| ABLIC Inc. |                       |  |

# No. PM006-A-R-SD-1.0

| TITLE      | HSNT             | -6-B-Re | el    |

|------------|------------------|---------|-------|

| No.        | PM006-A-R-SD-1.0 |         |       |

| ANGLE      |                  | QTY.    | 5,000 |

| UNIT       | mm               |         |       |

|            |                  |         |       |

|            |                  |         |       |

|            |                  |         |       |

| ABLIC Inc. |                  |         |       |

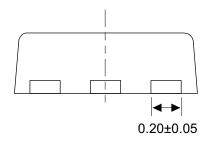

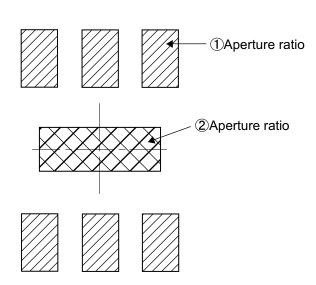

## **Land Pattern**

Caution It is recommended to solder the heat sink to a board in order to ensure the heat radiation.

注意 放熱性を確保する為に、PKGの裏面放熱板(ヒートシンク)を基板に 半田付けする事を推奨いたします。

## Metal Mask Pattern

- Caution ① Mask aperture ratio of the lead mounting part is 100%.

- 2 Mask aperture ratio of the heat sink mounting part is 40%.

- 3 Mask thickness: t0.10mm to 0.12 mm

- 注意 ①リード実装部のマスク開口率は100%です。

- ②放熱板実装のマスク開口率は40%です。

- ③マスク厚み: t0.10mm~0.12 mm

| TITLE | HSNT-6-B<br>-Land Recommendation |

|-------|----------------------------------|

| No.   | PM006-A-L-SD-2.0                 |

| ANGLE |                                  |

| UNIT  | mm                               |

|       |                                  |

|       |                                  |

|       |                                  |

ABLIC Inc.

No. PM006-A-L-SD-2.0

## 免責事項 (取り扱い上の注意)

- 1. 本資料に記載のすべての情報 (製品データ、仕様、図、表、プログラム、アルゴリズム、応用回路例等) は本資料発行時点のものであり、予告なく変更することがあります。

- 2. 本資料に記載の回路例および使用方法は参考情報であり、量産設計を保証するものではありません。本資料に記載の 情報を使用したことによる、本資料に記載の製品 (以下、本製品といいます) に起因しない損害や第三者の知的財産 権等の権利に対する侵害に関し、弊社はその責任を負いません。

- 3. 本資料の記載に誤りがあり、それに起因する損害が生じた場合において、弊社はその責任を負いません。

- 4. 本資料に記載の範囲内の条件、特に絶対最大定格、動作電圧範囲、電気的特性等に注意して製品を使用してください。 本資料に記載の範囲外の条件での使用による故障や事故等に関する損害等について、弊社はその責任を負いません。

- 5. 本製品の使用にあたっては、用途および使用する地域、国に対応する法規制、および用途への適合性、安全性等を確認、試験してください。

- 6. 本製品を輸出する場合は、外国為替および外国貿易法、その他輸出関連法令を遵守し、関連する必要な手続きを行ってください。

- 7. 本製品を大量破壊兵器の開発や軍事利用の目的で使用および、提供 (輸出) することは固くお断りします。核兵器、生物兵器、化学兵器およびミサイルの開発、製造、使用もしくは貯蔵、またはその他の軍事用途を目的とする者へ提供 (輸出) した場合、弊社はその責任を負いません。

- 8. 本製品は、生命・身体に影響を与えるおそれのある機器または装置の部品および財産に損害を及ぼすおそれのある機器または装置の部品(医療機器、防災機器、防犯機器、燃焼制御機器、インフラ制御機器、車両機器、交通機器、車載機器、航空機器、宇宙機器、および原子力機器等)として設計されたものではありません。上記の機器および装置には使用しないでください。ただし、弊社が車載用等の用途を事前に明示している場合を除きます。上記機器または装置の部品として本製品を使用された場合または弊社が事前明示した用途以外に本製品を使用された場合、これらにより発生した損害等について、弊社はその責任を負いません。

- 9. 半導体製品はある確率で故障、誤動作する場合があります。本製品の故障や誤動作が生じた場合でも人身事故、火災、 社会的損害等発生しないように、お客様の責任において冗長設計、延焼対策、誤動作防止等の安全設計をしてくださ い。また、システム全体で十分に評価し、お客様の責任において適用可否を判断してください。

- 10. 本製品は、耐放射線設計しておりません。お客様の用途に応じて、お客様の製品設計において放射線対策を行ってください。

- 11. 本製品は、通常使用における健康への影響はありませんが、化学物質、重金属を含有しているため、口中には入れないようにしてください。また、ウエハ、チップの破断面は鋭利な場合がありますので、素手で接触の際は怪我等に注意してください。

- 12. 本製品を廃棄する場合には、使用する地域、国に対応する法令を遵守し、適切に処理してください。

- 13. 本資料は、弊社の著作権、ノウハウに係わる内容も含まれております。本資料中の記載内容について、弊社または第三者の知的財産権、その他の権利の実施、使用を許諾または保証するものではありません。本資料の一部または全部を弊社の許可なく転載、複製し、第三者に開示することは固くお断りします。

- 14. 本資料の内容の詳細その他ご不明な点については、販売窓口までお問い合わせください。

- 15. この免責事項は、日本語を正本として示します。英語や中国語で翻訳したものがあっても、日本語の正本が優越します。

2.4-2019.07