## **CMOS IC Application Note**

# S-19989/19999 Series EXTERNAL PARTS SELECTION

Rev.1.1\_00

© ABLIC Inc., 2024

This application note is a method of external parts selection and recommended board layouts for the S-19989/19999 Series. Refer to the datasheet for details and specs.

## **Contents**

| 1. | Selecting Major External Parts |                               |    |  |

|----|--------------------------------|-------------------------------|----|--|

| 2. | Sele                           | cting Optional External Parts | 4  |  |

|    | 2. 1                           | Guideline for selecting parts | 4  |  |

| 3. | Boar                           | d Layout Precautions          | 14 |  |

|    | 3. 1                           | Application circuit diagram   | 14 |  |

|    | 3. 2                           | External components list      | 15 |  |

|    | 3. 3                           | PCB layout                    | 16 |  |

|    | 3. 4                           | Board layout precautions      | 16 |  |

| 4. | Prec                           | autions                       | 19 |  |

| 5. | 5. Related Sources             |                               |    |  |

## 1. Selecting Major External Parts

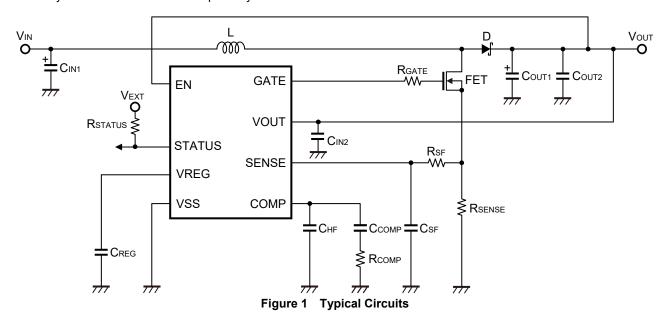

Major circuits are shown in **Figure 1**, operating conditions in **Table 1** and external part constants in **Table 2**. The output voltage (V<sub>OUT\_REG</sub>) inside the IC, which allows you to set 6.80 V or 8.50 V optionally.

Table 1 Design Example

| Design Parameter                 | Value                            |  |

|----------------------------------|----------------------------------|--|

| Input voltage (V <sub>IN</sub> ) | 6 V                              |  |

| Output voltage (Vout)            | 6.80 V or 8.50 V (Set in the IC) |  |

| Load current (ILOAD)             | 2 A                              |  |

| Oscillation frequency (fosc)     | 2.2 MHz                          |  |

Table 2 Constants for External Components

|                   |              | i able 2 | Constants for External Components |                       |

|-------------------|--------------|----------|-----------------------------------|-----------------------|

| Symbol            | Value        | Quantity | Part Number                       | Manufacture           |

| L                 | 0.47 μΗ      | 1        | SPM5030VT-R47M-D                  | TDK Corporation       |

| FET               | _            | 1        | IPC50N04S5L-5R5                   | Infineon Technologies |

| D                 | _            | 1        | PMEG045V100EPD                    | Nexperia B.V.         |

| C <sub>IN1</sub>  | 33 μF        | 2        | GYC1H330MCQ1GS                    | NICHICON CORPORATION  |

| C <sub>IN2</sub>  | 0.1 μF       | 1        | CGA4J2X8R1H104K                   | TDK Corporation       |

| C <sub>OUT1</sub> | 100 μF       | 3        | GYC1H101MCQ1GS                    | NICHICON CORPORATION  |

| C <sub>OUT2</sub> | 10 μF        | 1        | CGA5L1X7R1H106K                   | TDK Corporation       |

| RGATE             | 10 Ω         | 1        | MCR3 series (1608)                | ROHM CO., LTD.        |

| RSENSE            | 4 m $\Omega$ | 1        | TLR2BPDTD4L00F75                  | KOA CORPORATION       |

| RsF               | 22 Ω         | 1        | MCR3 series (1608)                | ROHM CO., LTD.        |

| RSTATUS           | 100 kΩ       | 1        | MCR3 series (1608)                | ROHM CO., LTD.        |

| CsF               | 10 nF        | 1        | CGA3E2X8R1H103K                   | TDK Corporation       |

| Creg              | 1 μF         | 1        | CGA5L3X8R1H105K                   | TDK Corporation       |

| RCOMP             | 12 kΩ        | 1        | MCR3 series (1608)                | ROHM CO., LTD.        |

| Ссомр             | 4.7 nF       | 1        | CGA3E2X8R1H472K                   | TDK Corporation       |

| Снғ               | 220 pF       | 1        | CGA3E2NP01H221J                   | TDK Corporation       |

Caution The above connection diagram and the constant do not guarantee proper operation. Perform thorough evaluation including the temperature characteristics with an actual application to set the constants.

## 2. Selecting Optional External Parts

This section provides detailed information about parts and a guideline on selecting parts for use with the step-up controller in continuous conduction mode (CCM).

#### 2. 1 Guideline for selecting parts

## 2. 1. 1 Definition of design parameters

Design parameters required in calculations used for selecting parts are defined below.

V<sub>IN\_MIN</sub>: Minimum input voltage [V]

V<sub>IN\_MAX</sub>: Maximum input voltage [V]

I<sub>IN\_MIN</sub>: Minimum average input current [A]

I<sub>IN\_MAX</sub>: Maximum average input current [A]

Vout: Output voltage [V]

IOUT\_MIN:Minimum load current [A]IOUT\_MAX:Maximum load current [A]η:Conversion efficiencyfosc:Oscillation frequency [Hz]

#### 2. 1. 2 Calculating minimum and maximum duty cycle

Use the following equations to calculate minimum duty cycle ( $D_{MIN}$ ) and maximum duty cycle ( $D_{MAX}$ ) including power loss for the step-up converter.

$$D_{MIN} = \frac{V_{OUT} + V_F - V_{IN\_MAX}}{V_{OUT} + V_F - \left(R_{ON} + R_{SENSE}\right) \times I_{IN\_MIN}}$$

$$D_{MAX} = \frac{V_{OUT} + V_F - V_{IN\_MIN}}{V_{OUT} + V_F - (Ron + Rsense) \times I_{IN\_MAX}}$$

V<sub>F</sub> is diode forward voltage, R<sub>ON</sub> is MOS FET on-resistance and R<sub>SENSE</sub> is a sense resistor for detecting inductor current

As can be seen from the following efficiency equation, I<sub>IN MIN</sub> and I<sub>IN MAX</sub> are expressed as follows.

$$I_{\text{IN\_MIN}} = \frac{V_{\text{OUT}} \times I_{\text{OUT\_MIN}}}{V_{\text{IN MAX}} \times \eta}$$

$$I_{IN\_MAX} = \frac{V_{OUT} \times I_{OUT\_MIN}}{V_{IN\_MAX} \times \eta}$$

The duty cycle range must conform to two parameters: minimum duty cycle ( $t_{ON\_MIN} \times f_{OSC}$ ) and maximum duty cycle (MaxDuty) specified by electrical characteristics.

$D_{MIN} > t_{ON\_MIN} \times f_{OSC}$ : Lower limit  $D_{MAX} < MaxDuty$ : Upper limit

If the upper duty cycle limit (D<sub>MAX</sub> < MaxDuty) is not met, boost operation becomes impossible.

If the lower duty cycle limit ( $D_{MIN} > t_{ON\_MIN} \times f_{OSC}$ ) is not met, pulse skip operation (PFM control) is always performed. PFM control is a function to prevent efficiency loss at light loads. Use PWM control to ensure regulation performance at normal and heavy loads. It is recommended to set a duty cycle tailored to the requirements.

4

## 2. 1. 3 Selecting an inductor

#### (1) Calculating inductor value

Operate in current continuous mode to suppress inductor current ripple and output voltage ripple. To do so, calculate to find the inductance value where the inductor current ripple ratio (r) is 0.2 to 0.6 to the maximum average inductor current (I<sub>L MAX</sub>).

Set inductor current ripple ratio (r) higher than the above (> 1) and operate in discontinuous conduction mode (DCM) to enable selecting a smaller inductor value and reduce the cost.

This will result in better transient characteristics, but the peak value of the inductor current will be larger, which is expected to increase electromagnetic interference (EMI).

I<sub>L MAX</sub> can be obtained as follows.

$$I_{L\_MAX} = I_{IN\_MAX} = \frac{I_{OUT\_MAX}}{1 - D_{MAX}}$$

The input current and inductor current are equal. The inductor current ripple  $(\Delta I_L)$  can be obtained from the following equation.

$$\Delta I_L = r \times I_{L\_MAX}$$

Thus, the minimum inductor value can be calculated as shown below.

$$L_{MIN} = \frac{V_{IN\_MIN} \times D_{MAX}}{\Delta I_{L} \times f_{OSC}}$$

Set a standard inductance value (L) to take variations into account.

## (2) Inductor peak current

Inductor peak current should never reach the saturation current rating of the inductor. The maximum inductor peak current ( $I_{LPEAK\ MAX}$ ) can be calculated from the maximum inductor current ripple value ( $\Delta I_{LPP\ MAX}$ ) as follows.

$$\begin{split} I_{\text{LPEAK\_MAX}} &= I_{\text{L\_MAX}} + \frac{\Delta I_{\text{LPP\_MAX}}}{2} = \frac{I_{\text{OUT\_MAX}}}{1 - D_{\text{MAX}}} + \frac{V_{\text{IN\_MIN}} \times D_{\text{MAX}}}{2 \times L \times fosc} \\ \Delta I_{\text{LPP\_MAX}} &= \frac{V_{\text{IN\_MIN}}}{L} \times \frac{D_{\text{MAX}}}{fosc} \end{split}$$

## (3) Inductor RMS current

Inductor RMS current, like inductor peak current, must always meet the RMS current rating. The maximum inductor RMS current (I<sub>LRMS\_MAX</sub>) can be obtained from the following equation.

$$I_{LRMS\_MAX} = \sqrt{I_{L\_MAX}^2 + \frac{\Delta I_{LPP\_MAX}^2}{12}} = \sqrt{\left(\frac{I_{OUT\_MAX}}{1 - D_{MAX}}\right)^2 + \frac{1}{12} \times \left(\frac{V_{IN\_MIN} \times D_{MAX}}{L \times f_{OSC}}\right)^2}$$

#### 2. 1. 4 Selecting a sense resistor (R<sub>SENSE</sub>)

The sense resistor (R<sub>SENSE</sub>) is connected between the SENSE pin and GND of the IC and detects inductor current information as ramp voltage. This ramp voltage is used for overcurrent protection (OCP) and peak current mode control.

The overcurrent protection settings are shown below, but make sure that the stability conditions for peak current mode are also met.

#### (1) Overcurrent protection settings

The S-19989/19999 Series integrates a pulse-by-pulse overcurrent protection function. When the peak inductor current flows through  $R_{SENSE}$  and the SENSE pin voltage ( $V_{SENSE}$ ) exceeds the threshold ( $V_{LIM}$ ), the MOS FET turns off. In the next switching cycle, the MOS FET goes on. However, if  $V_{SENSE} > V_{LIM}$ , the MOS FET turns off again and continues the same operation in subsequent cycles. The IC returns to normal operation when  $V_{SENSE} < V_{LIM}$ .

The overcurrent and short-circuit protection (Hiccup control) of the S-19989/19999 Series provides no means to limit the current from input to output should a short circuit occur at the output of the converter. Use fuses or limit the current of the main power supply if protection against short circuits is required.

The recommended overcurrent detection value is the maximum inductor peak current (I<sub>LPEAK\_MAX</sub>) plus 20%. Use the following equation to calculate R<sub>SENSE</sub> at this time.

$$R_{SENSE} = \frac{V_{LIM}}{1.2 \times I_{LPEAK\ MAX}}$$

#### (2) Peak current mode stability conditions

The current control loop becomes unstable in peak current mode control and may cause sub-harmonic oscillations. For this reason, regulation will maintain operation of the voltage loop without oscillations. However, the pulses from the PWM alternate between long and short and increase output ripple voltage. This state occurs only when the converter operates in continuous mode at a duty cycle of 50% or more.

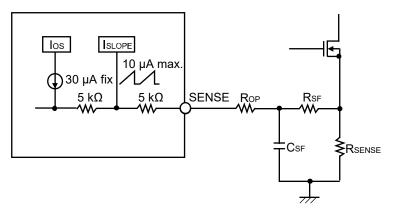

The S-19989/19999 Series integrates a slope compensation function as a countermeasure to subharmonic oscillations. Inside the IC, a sawtooth slope compensation ramp current ( $I_{SLOPE} = 10 \, \mu A \, max.$ ) flows through a 5 k $\Omega$  resistor to generate a slope compensation ramp voltage ( $S_E$ ). The SENSE pin outputs the sawtooth current and offset current ( $I_{OS} = 30 \, \mu A \, fixed$ ).

Figure 2 SENSE Pin Area Simplified Diagram

$S_E = 10 \mu A \times 5 k\Omega \times f_{OSC}$

The theoretical condition for preventing subharmonic oscillations is  $S_E > 0.5 \times S_F$ .  $S_F$  is the ramp voltage generated by inductor current and  $R_{SENSE}$ . The  $R_{SENSE}$  condition is indicated by the following equation.

$$\begin{split} S_F &= \frac{V_{OUT} + V_F - V_{IN\_MIN}}{L} \times R_{SENSE} \\ R_{SENSE} &< \frac{100 \text{ mV} \times f_{OSC} \times L}{V_{OUT} + V_F - V_{IN\_MIN}} \end{split}$$

If there is a risk of subharmonic oscillations even when the above setting conditions are satisfied, add a resistor (R<sub>OP</sub>) between the SENSE pin and R<sub>SENSE</sub> to increase the slope of slope compensation. At this time,  $S_E$  = 10  $\mu$ A × (5  $k\Omega$  + R<sub>OP</sub>) × f<sub>OSC</sub> and R<sub>SENSE</sub> is obtained by the following equation.

$$R_{SENSE} < \frac{20~\mu\text{A} \times (5~k\Omega + R_{OP}) \times f_{OSC} \times L}{V_{OUT} + V_F - V_{IN\_MIN}}$$

Since 40  $\mu$ A max. (sawtooth current + offset current)  $\times$  RoP offset voltage are generated and becomes  $V_{LIM} \rightarrow V_{LIM}$  – 40  $\mu$ A  $\times$  RoP, make sure the overvoltage current protection threshold does not decrease. Note that if the slope compensation slope is made too large, the inductor current information becomes relatively small. Therefore, this control resembles voltage mode control, and may lower the quality of the input response.

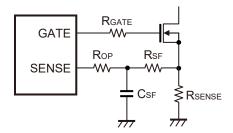

Figure 3 RC Filter

## (3) SENSE signal filtering

When the MOS FET is turned on and off, the resonance of the parasitic inductor, MOS FET output capacitance and diode junction capacitance caused by PC board wiring leads to overshoot / undershoot and ringing exceeding several 10 MHz in the switching waveform.

If these are propagated to the SENSE pin, the inductor current information is incorrectly detected making regulation operation unstable.

In the S-19989/19999 Series, a blanking time (equivalent to  $t_{ON\_MIN}$ ) is set immediately after turning on the MOS FET to mask this noise. If the ringing exceeds the blanking time, add the RC filters (R<sub>SF</sub> and C<sub>SF</sub>) shown in **Figure 3** between the R<sub>SENSE</sub> and the SENSE pin to reduce ringing.

Check the cycle of the ringing waveform and set the time constant of the RC filter to about 10 times the ringing cycle. Setting a high  $R_{SF}$  will impact the detection value of overcurrent protection so a value of 50  $\Omega$  or less is recommended.

Refer also to "(6) Ringing countermeasures in switching waveforms" in "2. 1. 10 Selecting a MOS FET", for information on how to reduce ringing waveforms in switching waveforms.

#### 2. 1. 5 Selecting a diode

To increase efficiency, adding a Schottky diode with low forward voltage and small reverse leakage current is recommended.

## (1) Rated voltage and current

The diode is reverse biased while the MOS FET is on. Provide a proper margin between the maximum peak reverse voltage rating of the diode and regulator output voltage (V<sub>OUT</sub>).

The diode conducts while the MOS FET is off, supplying energy stored in the inductor to the output capacitor. Therefore, over one switching cycle, the maximum average diode current ( $I_{D\_MAX}$ ) is equal to maximum load current ( $I_{OUT\_MAX}$ ).

$$I_{D MAX} = I_{OUT MAX}$$

Set the maximum forward average diode current (I<sub>F MAX</sub>) to be larger than the maximum load current (I<sub>OUT MAX</sub>).

## (2) Power consumption and temperature

Diode power consumption is  $P_D = V_F \times I_D$ . Ensure that the junction temperature Tj [°C] does not exceed the maximum junction temperature rating of the diode even at maximum ambient temperature.

$$T_i = Ta + \theta_{JA} \times P_D$$

Ta is ambient temperature [ $^{\circ}$ C] and  $\theta_{JA}$  is the thermal resistance of the diode [ $^{\circ}$ C/W].

## 2. 1. 6 Selecting an output capacitor

The rated voltage of the capacitor must be higher than maximum output voltage. Specifically, when MLCC capacitors are used, the capacitance may vary depending on temperature and applied DC voltage, so a sufficient margin should be considered when making a selection.

Output capacitors that meet the desired output voltage ripple ( $\Delta V_{OUT}$ ) and output RMS ripple current should be selected.

### (1) Calculating output voltage ripple

Output voltage ripple is the sum of voltage fluctuations caused by capacitor ( $C_{OUT}$ ) charging and discharging and the ripple current in the equivalent series resistance ( $R_{ESR}$ ) of the capacitor, as shown in the equation below.

$$\Delta V_{\text{OUT}} = \left(\frac{\text{Iout\_max} \times D_{\text{MAX}}}{C_{\text{OUT}} \times f_{\text{OSC}}}\right) + R_{\text{ESR}} \times \left(\frac{\text{Iout\_max}}{1 - D_{\text{MAX}}} + \frac{V_{\text{IN\_MIN}} \times D_{\text{MAX}}}{2 \times L \times f_{\text{OSC}}}\right)$$

There is actually a phase difference between the two ripples, but this is simplified in the equation.

## (2) Calculating RMS ripple

The RMS ripple current (ICOUTRMS) of the output capacitor can be calculated as shown in the following equation.

$$I_{COUTRMS} = \sqrt{\left(1 + D_{MAX}\right) \times \left\{\frac{D_{MAX}}{\left(1 - D_{MAX}\right)^2} \times I_{OUT\_MAX}^{\ 2} + \frac{\Delta I_L}{12}\right\}}$$

Select a C<sub>OUT</sub> value so that the RMS ripple current satisfies the rating. If it does not, add capacitors in parallel. ESR reduction can also be expected.

## \_\_\_\_

## 2. 1. 7 Phase compensation element selection

A phase compensation element is required to add phase compensation to the error amplifier in order to achieve high power supply stability.

The system control is a closed loop, which controls the switching operation through the adjustment of an appropriate duty cycle. This makes it possible to achieve the required output voltage and output load.

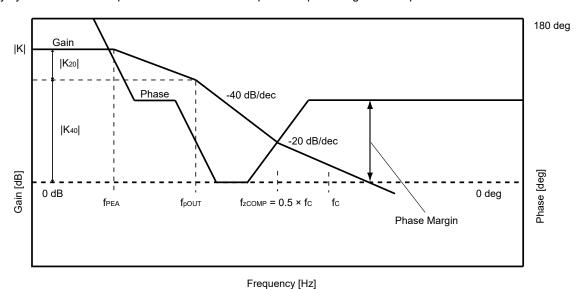

Figure 4 Bode plot of the S-19989/19999 Series

The transfer function from this closed loop can be used to express the parameters shown in **Figure 4** as shown in the formula below.

$$\begin{split} |\mathsf{K}| &= 20 \times log_{10} \, \left( \frac{R_{\mathsf{OUT}} \times (1 - D_{\mathsf{MIN}})}{2 \times R_{\mathsf{SENSE}}} \times \mathsf{gm} \times R_{\mathsf{EA}} \times \frac{R_{\mathsf{FB2}}}{R_{\mathsf{FB1}} + R_{\mathsf{FB2}}} \right) \\ f_{\mathsf{PEA}} &= \frac{f_{\mathsf{pOUT}}}{10^{\frac{|\mathsf{K}| - 40 \times log_{10}(f_{\mathsf{C}} / f_{\mathsf{poUT}})}{20}}} \\ f_{\mathsf{pOUT}} &= \frac{2}{2 \, \pi \times R_{\mathsf{OUT}} \times C_{\mathsf{OUT}}} \\ f_{\mathsf{ZESR}} &= \frac{1}{2 \, \pi \times R_{\mathsf{ESR}} \times C_{\mathsf{OUT}}} \\ f_{\mathsf{ZRHP}} &= \frac{R_{\mathsf{OUT}}}{2 \, \pi \times L} \times (1 - D_{\mathsf{MIN}})^2 \end{split}$$

**Remark** Output load resistance: Rout = Vout / lout  $[\Omega]$

Cout equivalent series resistance: Resr  $[\Omega]$ Error amplifier transconductance: gm [S]Error amplifier output resistance: Res  $\approx 10 \ [\text{M}\Omega]$

Also, RFB varies depending on Vout, so please refer to the values in **Table 3**.

Table 3

Vout

Design Parameter

6.80 V

8.50 V

RFB1

450 kΩ

580 kΩ

RFB2

60 kΩ

60 kΩ

If the phase margin < 0 deg at the frequency at which the closed loop gain is 0 dB (crossover frequency (fc)), oscillation will occur. Set the phase margin and gain margin as shown below to prevent this oscillation from occurring.

Phase Margin ≈ 45 deg to 60 deg Gain Margin ≥ 10 dB

This setting is achieved by appropriately configuring the phase compensation element. Therefore, it is necessary to place zeros at the appropriate frequencies in order to restore the phase.

Instability (subharmonic oscillation) at duty cycle settings of 50% of higher is not referenced because this IC is equipped with slope compensation.

In addition, the crossover frequency (f<sub>C</sub>) should also be set to whichever of the following is smallest in order to eliminate any effects of phase delay at the double pole and right half plane zero which are at half of the normal switching frequency (f<sub>OSC</sub>/2).

However, if  $f_{ZESR}$  or  $f_{ZRHP}$  are at similar frequency digits to  $f_C$ , it is recommended that  $f_C$  be set to 1/10th of those frequencies.

$$f_C < \frac{1}{10} \times f_{zESR} [Hz]$$

$$f_C < \frac{1}{10} \times f_{zRHP} [Hz]$$

**Remark** For  $R_{COMP}$  and  $C_{COMP}$  listed in **Table 2** and  $R_1$  and  $C_9$  listed in **Table 5**,  $f_C$  is set lower than the above to approximately 5 kHz to eliminate the effect of the right half plane zero.

To set f<sub>C</sub> even higher, follow the above equations.

## (1) Phase compensation capacity calculation

The phase compensation capacity can be found from the DC gain and fPEA as shown below.

$$C_{COMP} = \frac{1}{2\pi \times R_{EA} \times f_{PEA}}$$

## (2) Phase compensation resistance calculation

$$R_{COMP} = \frac{1}{2\pi \times C_{COMP} \times 0.5 \times f_{C}}$$

The error amplifier zero  $f_{zCOMP}$  is placed and phase compensation is carried out. The  $f_{zCOMP}$  position should be set to approximately  $0.5 \times f_C \le f_{zCOMP} < f_C$ . In **Figure 4** this is set to  $f_{zCOMP} = 0.5 \times f_C$ .

## (3) High frequency noise blocking capacitor (CHF) calculation

Connect a capacitor calculated using the following formula to the COMP pin in order to prevent malfunctions resulting from switching noise.

$$C_{HF} < \frac{1}{2 \pi \times R_{COMP} \times 10 \times f_C}$$

Also take the following into consideration when carrying out actual power supply design.

- Verify the phase margin and gain margin using a network analyzer.

- If the phase margin is insufficient, increase RCOMP.

- If it is still insufficient, reset the fc to a lower value.

#### 2. 1. 8 Selecting input capacitors

When AC current is supplied to an inductor, input capacitors are required to reduce input voltage ripple.

In current continuous mode, only input voltage ripple need to be considered since the input current caused by the steady-state boost operation is continuous and the selection conditions are not as strict as for C<sub>OUT</sub>. However, large input and load variations in current discontinuous mode, may require an additional capacitor with larger capacitance to buffer the input voltage.

#### (1) IC bypass capacitor

It is recommended to connect a ceramic capacitor with low ESR of about 0.1  $\mu$ F to 1  $\mu$ F near the V<sub>IN</sub> – VSS pin of the IC to lower input impedance in order to prevent malfunctions caused by noise and other factors.

#### (2) Input capacitor for step-up converter

As an inductor is connected in series with the input of a step-up converter, the input current waveform becomes a continuous triangular waveform when the MOS FET is turned on and off. This current generates input voltage ripple  $(\Delta V_{IN})$  in  $C_{IN}$ , which can be roughly estimated by the following equation.

$$\Delta V_{\text{IN}} = \Delta I_{\text{L}} \times \left( R_{\text{ESR}} + \frac{1}{8 \times f_{\text{OSC}} \times C_{\text{IN}}} \right)$$

$R_{ESR}$  is the equivalent series resistance of  $C_{IN}$ . To reduce voltage ripple and ensure stable operation during input and load transients, connect a low ESR ceramic capacitor (33  $\mu F$  to 100  $\mu F$ ) or a conductive polymer hybrid aluminum electrolytic capacitor to  $C_{IN}$ .

Also verify that the capacitor meets its rated ripple with respect to withstand voltage, operating temperature, and input current root mean square value (I<sub>INRMS</sub>) as calculated by the equation below.

$$I_{\text{INRMS}} = \frac{1}{2\sqrt{3}} \times \Delta I_{\text{L}}$$

## 2. 1. 9 Selecting VREG pin capacitors

$V_{REG}$  is the internal power supply voltage of an IC output by the VREG pin and used to operate some internal IC circuits. Also, when the MOS FET is turned on, a current for charging the GATE momentarily flows from  $V_{REG}$ . Connect a low ESR ceramic capacitor near the VREG – VSS pin to prevent VREG from dropping during this brief ON period. A capacitance value of 1  $\mu$ F is recommended.

Do not connect any external parts or loads other than a ceramic capacitor to the VREG pin.

#### 2. 1. 10 Selecting a MOS FET

MOS FET is the main switching element in step-up converters. Rated voltage and current needs to be considered in their selection.

Power loss is mainly caused by conduction loss, switching loss and gate drive loss.

## (1) Rated voltage and current

During the MOS FET off period, the drain-source voltage is equal to  $V_{OUT} + V_F$ . If ringing occurs at the switching node, a margin must be provided with respect to the rated voltage.

Also, maximum input current (I<sub>IN\_MAX</sub>) should not exceed the MOS FET drain current rating.

## (2) Conduction loss (PCOND)

P<sub>COND</sub> is power lost in the on-resistor when the MOS FET is on.

The maximum RMS current (I<sub>SWRMS MAX</sub>) at this time can be calculated as follows.

$$I_{SWRMS\_MAX} = \sqrt{D_{MAX}} \times \sqrt{\left(\frac{I_{OUT\_MAX}}{1 - D_{MAX}}\right)^2 + \frac{\Delta I_L^2}{12}}$$

Thus, MOS FET conduction loss (PCOND) can be obtained by the following equation.

$$P_{COND} = R_{ON} \times D_{MAX} \times \left\{ \left( \frac{I_{OUT\_MAX}}{1 - D_{MAX}} \right)^2 + \frac{\Delta I_L^2}{12} \right\}$$

## (3) Switching loss (Psw)

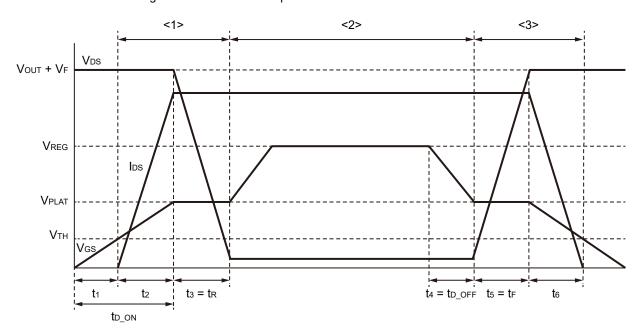

Psw is the loss generated by the flow of current and voltage between drain and source when a MOS FET is turned on and off.

$$P_{SW} = \frac{V_{OUT} + V_F}{2} \times I_{L\_MAX} \times f_{OSC} \times (t_{TR\_ON} + t_{TR\_OFF})$$

$$t_{TR\_ON} = t_{D\_ON} - R_G \times C_{ISS} \times In \left( \frac{V_{REG}}{V_{REG} - V_{TH}} \right) + t_R$$

$$t_{TR\_OFF} = R_G \times C_{ISS} \times In \left( \frac{V_{PLAT}}{V_{TH}} \right) + t_F$$

The following parameters are listed in the MOS FET data sheet.

$\begin{array}{ll} C_{ISS} \colon & \text{Input capacitance} \\ V_{TH} \colon & \text{Threshold voltage} \\ V_{PLAT} \colon & \text{Plateau voltage} \\ t_{D \ ON} \colon & \text{Turn On delay time} \end{array}$

$t_R$ : Rise time  $t_F$ : Fall time

t<sub>D OFF</sub>: Turn Off delay time

Rg: Internal MOS FET gate resistor + gate drive circuit on-resistor + option resistor (RGATE) between MOS

FET gate and drive circuit output

<1> Turn on period: Psw occurrence

<2> MOS FET on period: Pcond occurrence

<3> Turn off period: Psw occurrence

Figure 5 MOS FET On and Off Voltage and Current Transitions

## (4) Gate drive loss (PGATE)

P<sub>GATE</sub> is the loss caused by charging and discharging input capacitance in driving the MOS FET gate.

$P_{GATE} = C_{ISS} \times V_{REG}^2 \times f_{OSC}$

## (5) Total MOS FET loss (PTOTAL) and junction temperature

As indicated in (2) to (4), total MOS FET power loss is P<sub>TOTAL</sub> = P<sub>COND</sub> + P<sub>SW</sub> + P<sub>GATE</sub>.

Make sure that junction temperature  $T_j$  [°C] does not exceed the maximum MOS FET junction temperature rating even at maximum ambient temperature.

$T_j = Ta + R_{\theta jA} \times P_{TOTAL}$

$R_{\theta j A}$  is the thermal resistance between the IC chip junction and the ambient environment.

#### (6) Ringing countermeasures in switching waveforms

Connecting a gate resistor ( $R_{GATE}$ ) of several 10 ohms to reduce ringing in switching waveforms is also effective, but note that there is a trade-off with efficiency due to resistor losses.

## 3. Board Layout Precautions

PCB layout and component placement are essential in ensuring stable operation of the switching regulator and to achieve good regulation performance, conversion efficiency, and noise reduction. We will explain points to note in PCB layout using our PCB as an example.

## 3. 1 Application circuit diagram

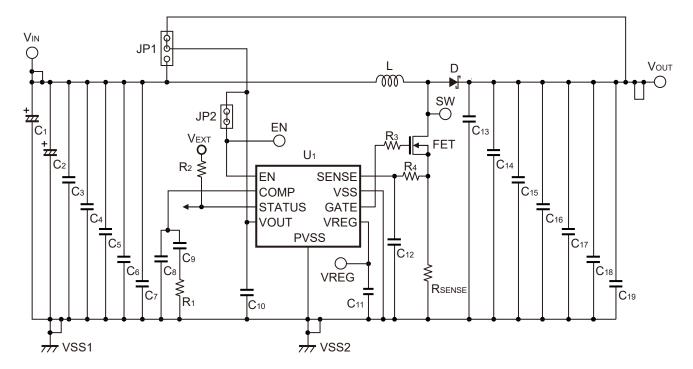

Figure 6 shows the circuit diagram of a step-up application created by ABLIC Inc.

Connect the  $V_{\text{OUT}}$  and VOUT pin via JP1 to create a bootstrap configuration. Connect the EN pin to the  $V_{\text{OUT}}$  via JP2, or leave JP2 open to apply voltage externally.

Figure 6

Table 4 Design Example

| Design Parameter                 | Value                            |  |

|----------------------------------|----------------------------------|--|

| Input voltage (V <sub>IN</sub> ) | 6 V                              |  |

| Output voltage (Vout)            | 6.80 V or 8.50 V (Set in the IC) |  |

| Load current (ILOAD)             | 2 A                              |  |

| Oscillation frequency (fosc)     | 2.2 MHz                          |  |

14 ABLIC Inc.

## 3. 2 External components list

Table 5 shows external components used in the connection examples: Figure 6.

Table 5 External Components

| Symbol             | Value         | Part Number          | Manufacture           |

|--------------------|---------------|----------------------|-----------------------|

| U <sub>1</sub>     | _             | S-19989/19999 Series | ABLIC Inc.            |

| C <sub>1</sub>     | 33 μF         | GYC1H330MCQ1GS       | NICHICON CORPORATION  |

| $C_2$              | 33 μF         | GYC1H330MCQ1GS       | NICHICON CORPORATION  |

| C <sub>3</sub>     | User settings | _                    | _                     |

| C <sub>4</sub>     | User settings | _                    | _                     |

| C <sub>5</sub>     | User settings | _                    | _                     |

| C <sub>6</sub>     | User settings | _                    | _                     |

| C <sub>7</sub>     | User settings | _                    | _                     |

| C <sub>8</sub>     | 220 pF        | CGA3E2NP01H221J      | TDK Corporation       |

| C <sub>9</sub>     | 4.7 nF        | CGA3E2X8R1H472K      | TDK Corporation       |

| C <sub>10</sub>    | 0.1 μF        | CGA4J2X8R1H104K      | TDK Corporation       |

| C <sub>11</sub>    | 1 μF          | CGA5L3X8R1H105K      | TDK Corporation       |

| C <sub>12</sub>    | 10 nF         | CGA3E2X8R1H103K      | TDK Corporation       |

| C <sub>13</sub>    | User settings | _                    | _                     |

| C <sub>14</sub>    | 10 μF         | CGA5L1X7R1H106K      | TDK Corporation       |

| C <sub>15</sub>    | User settings | _                    | _                     |

| C <sub>16</sub>    | 10 μF         | CGA5L1X7R1H106K      | TDK Corporation       |

| C <sub>17</sub>    | 100 μF        | GYC1H101MCQ1GS       | NICHICON CORPORATION  |

| C <sub>18</sub>    | 100 μF        | GYC1H101MCQ1GS       | NICHICON CORPORATION  |

| C <sub>19</sub>    | 100 μF        | GYC1H101MCQ1GS       | NICHICON CORPORATION  |

| C <sub>20</sub>    | User settings | _                    | _                     |

| R <sub>1</sub>     | 12 kΩ         | MCR3 series (1608)   | ROHM CO., LTD.        |

| R <sub>2</sub>     | 100 kΩ        | MCR3 series (1608)   | ROHM CO., LTD.        |

| R <sub>3</sub>     | 10 Ω          | MCR3 series (1608)   | ROHM CO., LTD.        |

| R <sub>4</sub>     | 22 Ω          | MCR3 series (1608)   | ROHM CO., LTD.        |

| R <sub>5</sub>     | User settings | _                    | _                     |

| R <sub>SENSE</sub> | 4 mΩ          | TLR2BPDTD4L00F75     | KOA CORPORATION       |

| JP1                | _             | _                    | _                     |

| JP2                |               |                      |                       |

| L                  | 0.47 μΗ       | SPM5030VT-R47M-D     | TDK Corporation       |

| FET                | _             | IPC50N04S5L-5R5      | Infineon Technologies |

| D                  | _             | PMEG045V100EPD       | Nexperia B.V.         |

Caution 1. The above constants may be changed without notice.

2. The above constants do not guarantee proper operation. Perform thorough evaluation using the actual application to set the constants.

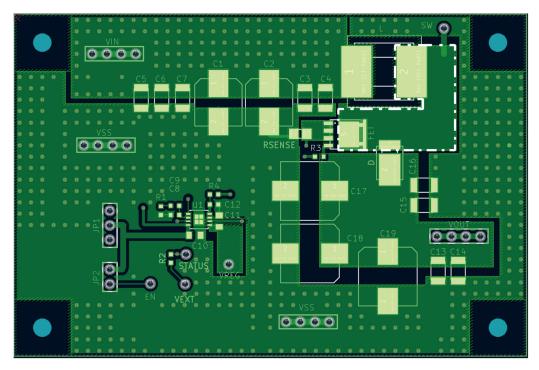

## 3. 3 PCB layout

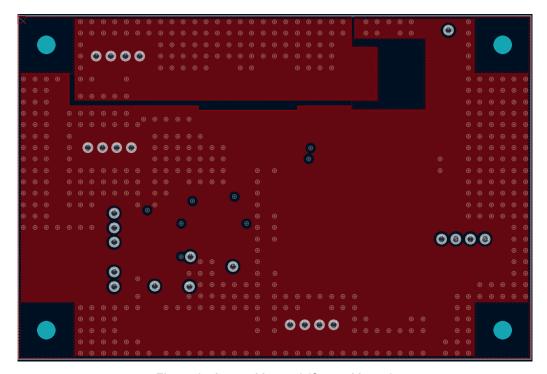

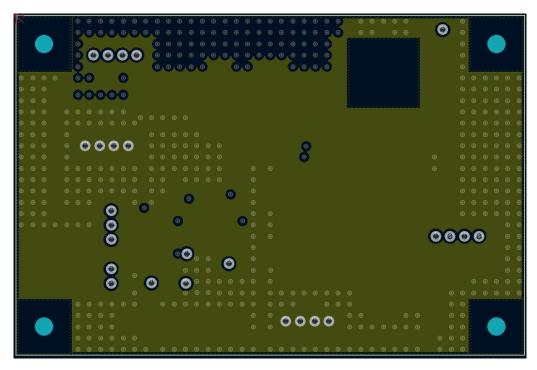

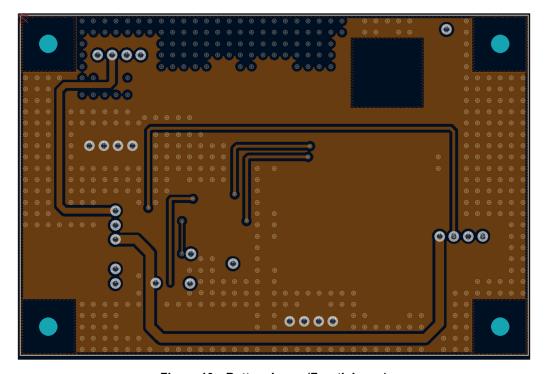

The board we have created for the application circuit diagram in **Figure 6** has four layers, which are shown in **Figure 7** to **Figure 10**.

Top layer: A layout containing most parts and wiring

Internal layer 1: A layer that reinforces VIN and VSS wiring

• Internal layer 2: A layer that reinforces VSS

• Bottom layer: Wiring that is difficult to route in the top layer and does not require significant attention and reinforces VSS

"3. 4 Board layout precautions" describe the precautions to take in performing these layouts.

## 3. 4 Board layout precautions

- Place C<sub>IN</sub> (C<sub>10</sub>) as close to the VOUT pin and the VSS pin as possible. Prioritize the layout of C<sub>IN</sub>.

- Place C<sub>REG</sub> (C<sub>11</sub>) as close to the VREG pin and the VSS pin as possible.

- GATE pin patterns should not create wiring below the IC.

- To provide proper ventilation, connect the rear heat dissipation pad to the VSS pattern and place thermal vias.

- Make the switching loop composed of  $C_{OUT}$  ( $C_{13}$  to  $C_{19}$ )  $\rightarrow$  D  $\rightarrow$  FET  $\rightarrow$  R<sub>SENSE</sub>  $\rightarrow$   $C_{OUT}$  ( $C_{13}$  to  $C_{19}$ ) as small as possible. This measure effectively reduces inductive high-frequency noise.

- The SW wiring area (Dashed line area in "Figre 7 Top Layer (First Layer)") should be as small as possible to reduce high-frequency radiation noise.

- All copper foil on the back of the inductor (L) should be removed to avoid losses due to eddy currents.

- A ringing signal is superimposed on the SENSE signal during switching. If the ringing is large enough to cause malfunction, attenuate it using an RC filter (R<sub>4</sub>, C<sub>12</sub>). Place the RC filter as close to the IC as possible.

- Place Rsense close to the FET source.

- If SW waveform ringing is large, place ceramic capacitors (C<sub>15</sub>, C<sub>16</sub>) near the D cathode and between it and VSS to reduce the ringing.

- If the SW waveform ringing propagates to V<sub>OUT</sub> and causes unstable operation, place ceramic capacitors (C<sub>13</sub>, C<sub>14</sub>) near the VOUT pin and between it and VSS.

- To reduce ringing in the SW waveform, inserting a resistor (R<sub>3</sub>) in the FET gate line is effective, but is a trade-off with efficiency.

Figure 7 Top Layer (First Layer)

Figure 8 Internal Layer 1 (Second Layer)

Figure 9 Internal Layer 2 (Third Layer)

Figure 10 Bottom Layer (Fourth Layer)

Caution The above pattern diagram does not guarantee successful operation. Perform thorough evaluation using the actual application to determine the pattern.

18 ABLIC Inc.

## 4. Precautions

- The usages described in this application note are typical examples using ICs of ABLIC Inc. Perform thorough evaluation before use.

- Do not apply an electrostatic discharge to this IC that exceeds the performance ratings of the built-in electrostatic protection circuit.

- ABLIC Inc. claims no responsibility for any disputes arising out of or in connection with any infringement by products including this IC of patents owned by a third party.

## 5. Related Sources

Refer to the following datasheet for details of the S-19989/19999 Series.

S-19989 Series Datasheet S-19999 Series Datasheet

The information described in this application note and the datasheet is subject to change without notice. Contact our sales representatives for details.

Regarding the newest version of the datasheet, select product category and product name on our website, and download the PDF file.

www.ablic.com ABLIC Inc. website

## **Disclaimers (Handling Precautions)**

- 1. All the information described herein (product data, specifications, figures, tables, programs, algorithms and application circuit examples, etc.) is current as of publishing date of this document and is subject to change without notice.

- 2. The circuit examples and the usages described herein are for reference only, and do not guarantee the success of any specific mass-production design.

- ABLIC Inc. is not liable for any losses, damages, claims or demands caused by the reasons other than the products described herein (hereinafter "the products") or infringement of third-party intellectual property right and any other right due to the use of the information described herein.

- 3. ABLIC Inc. is not liable for any losses, damages, claims or demands caused by the incorrect information described herein.

- 4. Be careful to use the products within their ranges described herein. Pay special attention for use to the absolute maximum ratings, operation voltage range and electrical characteristics, etc.

- ABLIC Inc. is not liable for any losses, damages, claims or demands caused by failures and / or accidents, etc. due to the use of the products outside their specified ranges.

- 5. Before using the products, confirm their applications, and the laws and regulations of the region or country where they are used and verify suitability, safety and other factors for the intended use.

- 6. When exporting the products, comply with the Foreign Exchange and Foreign Trade Act and all other export-related laws, and follow the required procedures.

- 7. The products are strictly prohibited from using, providing or exporting for the purposes of the development of weapons of mass destruction or military use. ABLIC Inc. is not liable for any losses, damages, claims or demands caused by any provision or export to the person or entity who intends to develop, manufacture, use or store nuclear, biological or chemical weapons or missiles, or use any other military purposes.

- 8. The products are not designed to be used as part of any device or equipment that may affect the human body, human life, or assets (such as medical equipment, disaster prevention systems, security systems, combustion control systems, infrastructure control systems, vehicle equipment, traffic systems, in-vehicle equipment, aviation equipment, aerospace equipment, and nuclear-related equipment), excluding when specified for in-vehicle use or other uses by ABLIC, Inc. Do not apply the products to the above listed devices and equipments.

- ABLIC Inc. is not liable for any losses, damages, claims or demands caused by unauthorized or unspecified use of the products.

- 9. In general, semiconductor products may fail or malfunction with some probability. The user of the products should therefore take responsibility to give thorough consideration to safety design including redundancy, fire spread prevention measures, and malfunction prevention to prevent accidents causing injury or death, fires and social damage, etc. that may ensue from the products' failure or malfunction.

- The entire system in which the products are used must be sufficiently evaluated and judged whether the products are allowed to apply for the system on customer's own responsibility.

- 10. The products are not designed to be radiation-proof. The necessary radiation measures should be taken in the product design by the customer depending on the intended use.

- 11. The products do not affect human health under normal use. However, they contain chemical substances and heavy metals and should therefore not be put in the mouth. The fracture surfaces of wafers and chips may be sharp. Be careful when handling these with the bare hands to prevent injuries, etc.

- 12. When disposing of the products, comply with the laws and ordinances of the country or region where they are used.

- 13. The information described herein contains copyright information and know-how of ABLIC Inc. The information described herein does not convey any license under any intellectual property rights or any other rights belonging to ABLIC Inc. or a third party. Reproduction or copying of the information from this document or any part of this document described herein for the purpose of disclosing it to a third-party is strictly prohibited without the express permission of ABLIC Inc.

- 14. For more details on the information described herein or any other questions, please contact ABLIC Inc.'s sales representative.

- 15. This Disclaimers have been delivered in a text using the Japanese language, which text, despite any translations into the English language and the Chinese language, shall be controlling.