# **CMOS IC Application Note**

# S-19912/19913 Series NOISE COUNTERMEASURES AND CISPR25 MEASUREMENT RESULTS

Rev.1.0\_00

© ABLIC Inc., 2022

This application note is a reference describing recommended noise suppression parts and board layouts that help reduce conductive noise and emission noise for the S-19912/19913 Series. It also summarizes CISPR25 compliant measurement results.

Refer to the datasheet for details and specs.

## CMOS IC Application Note S-19912/19913 Series NOISE COUNTERMEASURES AND CISPR25 MEASUREMENT RESULTS Rev. 1.0\_00

## Contents

| 1. | Need for Noise Suppression Parts                                        |   |

|----|-------------------------------------------------------------------------|---|

| 2. | Board Layout                                                            |   |

|    | 2. 1 Placement of input capacitors (CIN0, CIN1) and VIN and VSS layouts |   |

|    | 2. 2 Placement and layout of Inductor (L1)                              |   |

|    | 2.3 Placement and layout of output capacitor (COUT1)                    | 5 |

|    | 2.4 Recommended board layout                                            |   |

| 3. |                                                                         |   |

|    | 3.1 Measurement condition                                               |   |

|    | 3. 2 Measurement results of voltage method                              | 7 |

|    | 3.3 Measurement results of ALSE method                                  |   |

| 4. | Precautions                                                             | 9 |

| 5. | Related Sources                                                         |   |

|    |                                                                         |   |

### 1. Need for Noise Suppression Parts

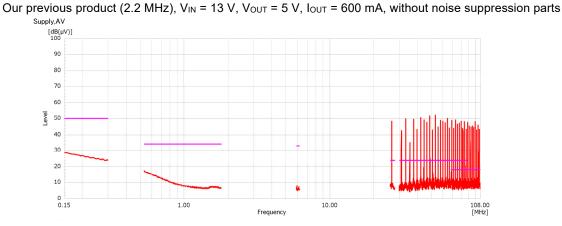

**Figure 1** shows the results of a voltage method measurement of a circuit to which no noise suppression parts have been applied. Although the measurement results significantly exceeded the CISPR25 class 5 specifications, this is not limited to this IC as general switching regulator ICs exhibit the similar tendency. For this reason, noise suppression parts must be applied to allow the IC to meet the stringent CISPR25 class 5 requirements. **Figure 1** to **Figure 3** show the necessity of noise suppression parts using our previous product as an example.

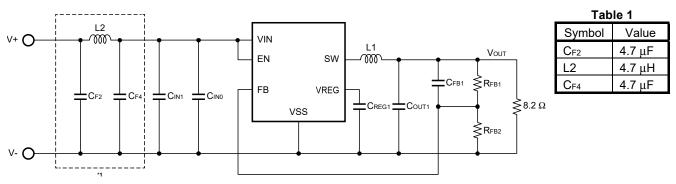

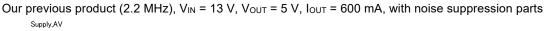

**Figure 2** is a circuit diagram to which the recommended noise suppression parts L2,  $C_{F2}$ , and  $C_{F4}$  listed in **Table 1** have been added. **Figure 3** shows the results of a voltage method measurement carried out on this circuit. The addition of noise suppression parts reduces noise by as much as 20 MHz or more allowing the IC to meet CISPR25 class 5 requirements. Also, this IC optimally adjusts the SW pin slew rate in the IC so that the minimum of noise suppression parts will obtain a substantial margin.

\*1. Noise suppression parts

#### Figure 3

This IC has a built-in spread spectrum clock generation circuit capable of reducing conductive noise and emission noise. Refer to the datasheet of the S-19912A/19912B/19913A/19913B Series for details.

### 2. Board Layout

#### 2.1 Placement of input capacitors (CINO, CIN1) and VIN and VSS layouts

The placement of input capacitors and VIN and VSS wirings are crucial. The input capacitors are of paramount importance and should be placed as close to the IC as possible and on the same surface layer.

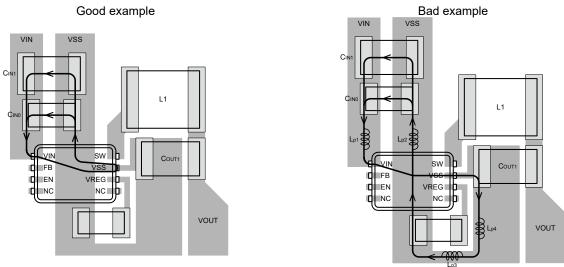

$C_{IN1}$  is an essential capacitor to ensure stable IC operation and to suppress noise.  $C_{IN0}$  is a capacitor of approximately 0.1  $\mu$ F which is connected in parallel to  $C_{IN1}$ . Add this capacitor as required to suppress mainly 10 MHz or larger noise. **Figure 4** shows an example of placing input capacitors in the immediate vicinity of the IC. The bold line indicates the current path the instant the high side power MOS FET in the IC turns on. First, current flows from the input capacitors to the VIN pin. Next, the current goes through the high side power MOS FET which is ON and the parasitic capacitance of low side power MOS FET which is OFF, both of which are inside the IC, in turn. Finally, the current returns to the input capacitors from the VSS pin. In this example, the reduction of impedance in the current path minimizes the noise generated in VIN and VSS wirings.

By contrast, **Figure 5** shows an example of input capacitors placed away from the IC and where the VSS pin is not connected to the VSS directly below the IC. At this time, there is a parasitic capacitance ( $L_{p1}$ ) between the input capacitors and the VIN pin. In addition, as the current path between the input capacitors and the VSS pin is significantly extended, the parasitic capacitances ( $L_{p2} + L_{p3} + L_{p4}$ ) extremely become large. In this example, impedance in the current path is increased and the noise generated in VIN and VSS wirings become larger.

Figure 4

#### 2. 2 Placement and layout of Inductor (L1)

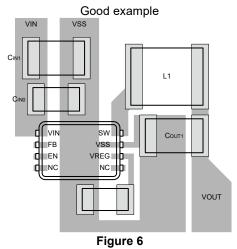

The wiring area of the SW pin should be minimized. Reduce the wiring length within the allowable current capacity range. The rectangular wave voltage output from the SW pin contains high-frequency components, which could cause SW wiring to act as an antenna and thereby increase emission noise. In addition, as the high-frequency components in the rectangular wave voltage previously mentioned are transmitted from the SW pin to VOUT via the parasitic capacitance, SW wiring must be kept apart from VOUT wiring. Select a closed magnetic path inductor with low emission noise.

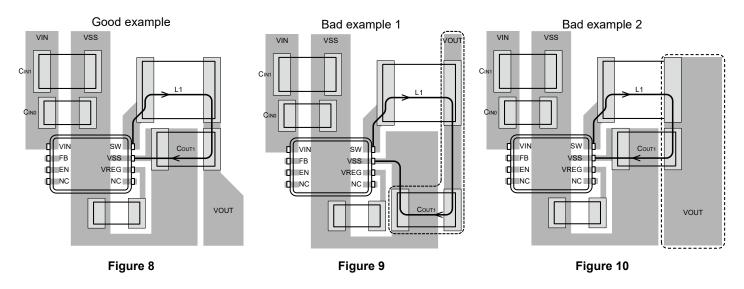

**Figure 6** shows an example where the wiring area between the SW pin and L1 is reduced and the distance between SW wiring and VOUT wiring is extended.

By contrast, **Figure 7** shows an example where the SW wiring area is excessively large, the distance between SW wiring and VOUT wiring is short, and the parasitic capacitance ( $C_p$ ) is large.

Figure 5

### 2. 3 Placement and layout of output capacitor (COUT1)

Place  $C_{OUT1}$  close to the IC.

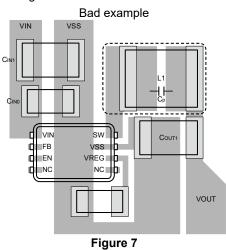

If the area of the current path indicated by the bold line (SW pin  $\rightarrow$  L1  $\rightarrow$  C<sub>OUT1</sub>  $\rightarrow$  VSS pin) is reduced, the emission noise to be generated will be minimized.

Be sure to pull out VOUT wiring after routing through the  $C_{OUT1}$  land. If this is not the case, smoothing due to L1 and  $C_{OUT1}$  is weakened causing high-frequency components in the rectangular wave voltage of SW pin to be conducted to VOUT. Similarly, when increasing the line width, pull out a wiring after routing through  $C_{OUT1}$  land.

Figure 8 is an example where the current path area is narrowed. VOUT wiring is pulled out after routing through the  $C_{OUT1}$  land.

By contrast, **Figure 9** is an example where the distance between the IC and  $C_{OUT1}$  is long and the current path area is large. VOUT wiring is pulled out from L1 land without routing through  $C_{OUT1}$  land.

Figure 10 is an example where VOUT line width is excessively increased before routing through C<sub>OUT1</sub> land.

### 2.4 Recommended board layout

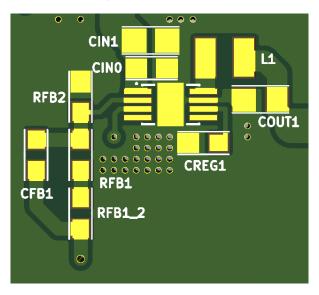

Figure 11 shows the recommended board layout that reflects the explanations previously mentioned.

Figure 11

### CMOS IC Application Note S-19912/19913 Series NOISE COUNTERMEASURES AND CISPR25 MEASUREMENT RESULTS Rev. 1.0\_00

### 3. Measurement Conditions and Measurement Results

#### 3.1 Measurement condition

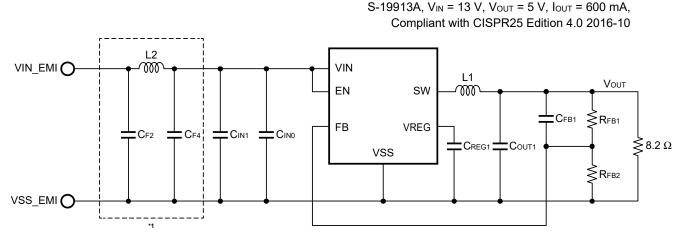

Figure 12 shows a circuit diagram of S-19913A Evaluation Board. The parts listed in Table 2 are mounted.

\*1. Noise suppression parts

#### Figure 12 Circuit Diagram of S-19913A Evaluation Board

|                  |        | Table 2              |                 |

|------------------|--------|----------------------|-----------------|

| Symbol           | Value  | Part Number          | Manufacturer    |

| CF2              | 4.7 μF | CGA4J1X7R1H475K125AC | TDK Corporation |

| L2               | 4.7 μH | TFM252012ALVA4R7MTAA | TDK Corporation |

| CF4              | 4.7 μF | CGA4J1X7R1H475K125AC | TDK Corporation |

| CIN1             | 4.7 μF | CGA4J1X7R1H475K125AC | TDK Corporation |

| CINO             | 0.1 μF | CGA3E2X7R1H104K      | TDK Corporation |

| L1               | 4.7 μH | TFM252012ALVA4R7MTAA | TDK Corporation |

| CREG1            | 1.0 μF | CGA3E1X7R1C105K080AC | TDK Corporation |

| Cout1            | 10 μF  | CGA4J3X7S1A106K125AB | TDK Corporation |

| Сғв              | 33 pF  | _                    | _               |

| R <sub>FB1</sub> | 84 kΩ  | _                    | _               |

| R <sub>FB2</sub> | 16 kΩ  | _                    | -               |

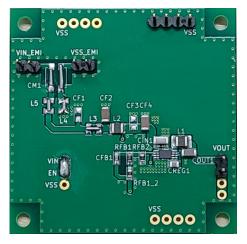

Figure 13 shows the actual board.

Figure 13

### 3. 2 Measurement results of voltage method

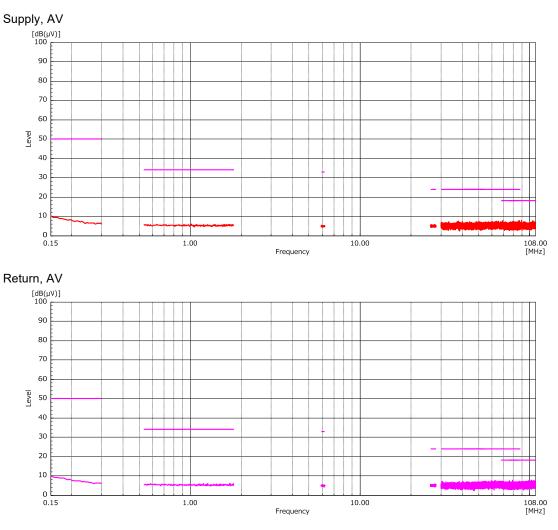

Figure 14 shows measurement results of voltage method.

Figure 14

### 3.3 Measurement results of ALSE method

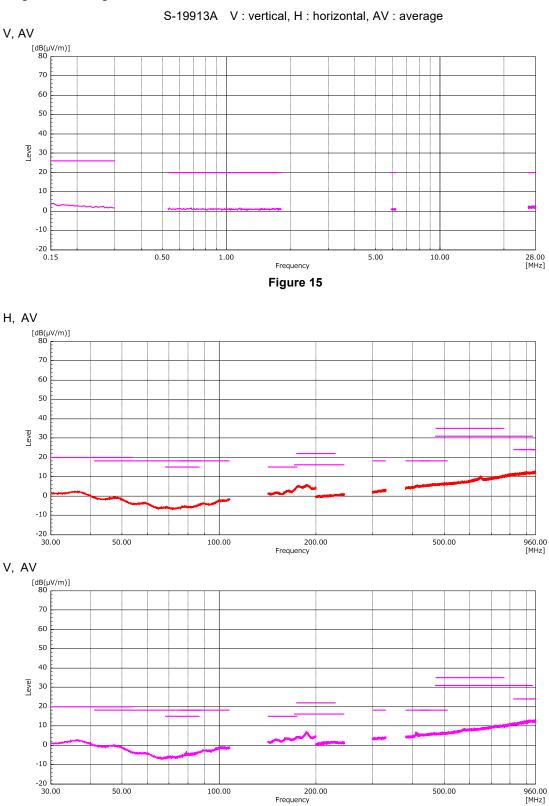

Figure 15 and Figure 16 show measurement results of ALSE method.

Figure 16

### 4. Precautions

- The usages described in this application note are typical examples using ICs of ABLIC Inc. Perform thorough evaluation before use.

- Do not apply an electrostatic discharge to this IC that exceeds the performance ratings of the built-in electrostatic protection circuit.

- ABLIC Inc. claims no responsibility for any disputes arising out of or in connection with any infringement by products including this IC of patents owned by a third party.

### 5. Related Sources

Refer to the following datasheet for details of the S-19912/19913 Series.

#### S-19912A/19912B/19913A/19913B Series Datasheet

The information described in this application note and the datasheet is subject to change without notice. Contact our sales representatives for details.

Regarding the newest version of the datasheet, select product category and product name on our website, and download the PDF file.

#### www.ablic.com ABLIC Inc. website

## **Disclaimers (Handling Precautions)**

- 1. All the information described herein (product data, specifications, figures, tables, programs, algorithms and application circuit examples, etc.) is current as of publishing date of this document and is subject to change without notice.

- The circuit examples and the usages described herein are for reference only, and do not guarantee the success of any specific mass-production design.

ABLIC Inc. is not liable for any losses, damages, claims or demands caused by the reasons other than the products described herein (hereinafter "the products") or infringement of third-party intellectual property right and any other right due to the use of the information described herein.

- 3. ABLIC Inc. is not liable for any losses, damages, claims or demands caused by the incorrect information described herein.

- 4. Be careful to use the products within their ranges described herein. Pay special attention for use to the absolute maximum ratings, operation voltage range and electrical characteristics, etc. ABLIC Inc. is not liable for any losses, damages, claims or demands caused by failures and / or accidents, etc. due to the use of the products outside their specified ranges.

- 5. Before using the products, confirm their applications, and the laws and regulations of the region or country where they are used and verify suitability, safety and other factors for the intended use.

- 6. When exporting the products, comply with the Foreign Exchange and Foreign Trade Act and all other export-related laws, and follow the required procedures.

- 7. The products are strictly prohibited from using, providing or exporting for the purposes of the development of weapons of mass destruction or military use. ABLIC Inc. is not liable for any losses, damages, claims or demands caused by any provision or export to the person or entity who intends to develop, manufacture, use or store nuclear, biological or chemical weapons or missiles, or use any other military purposes.

- 8. The products are not designed to be used as part of any device or equipment that may affect the human body, human life, or assets (such as medical equipment, disaster prevention systems, security systems, combustion control systems, infrastructure control systems, vehicle equipment, traffic systems, in-vehicle equipment, aviation equipment, aerospace equipment, and nuclear-related equipment), excluding when specified for in-vehicle use or other uses by ABLIC, Inc. Do not apply the products to the above listed devices and equipments. ABLIC Inc. is not liable for any losses, damages, claims or demands caused by unauthorized or unspecified use of the products.

- 9. In general, semiconductor products may fail or malfunction with some probability. The user of the products should therefore take responsibility to give thorough consideration to safety design including redundancy, fire spread prevention measures, and malfunction prevention to prevent accidents causing injury or death, fires and social damage, etc. that may ensue from the products' failure or malfunction.

The entire system in which the products are used must be sufficiently evaluated and judged whether the products are allowed to apply for the system on customer's own responsibility.

- 10. The products are not designed to be radiation-proof. The necessary radiation measures should be taken in the product design by the customer depending on the intended use.

- 11. The products do not affect human health under normal use. However, they contain chemical substances and heavy metals and should therefore not be put in the mouth. The fracture surfaces of wafers and chips may be sharp. Be careful when handling these with the bare hands to prevent injuries, etc.

- 12. When disposing of the products, comply with the laws and ordinances of the country or region where they are used.

- 13. The information described herein contains copyright information and know-how of ABLIC Inc. The information described herein does not convey any license under any intellectual property rights or any other rights belonging to ABLIC Inc. or a third party. Reproduction or copying of the information from this document or any part of this document described herein for the purpose of disclosing it to a third-party is strictly prohibited without the express permission of ABLIC Inc.

- 14. For more details on the information described herein or any other questions, please contact ABLIC Inc.'s sales representative.

- 15. This Disclaimers have been delivered in a text using the Japanese language, which text, despite any translations into the English language and the Chinese language, shall be controlling.

2.4-2019.07