### S-1410/1411 Series

www.ablic.com

# $$105^{\circ}\text{C}$$ OPERATION, 3.8 $\mu\text{A}$ CURRENT CONSUMPTION WATCHDOG TIMER WITH RESET FUNCTION

© ABLIC Inc., 2015-2020 Rev.2.5 00

The S-1410/1411 Series is a watchdog timer developed using CMOS technology, which can operate with low current consumption of  $3.8 \,\mu\text{A}$  typ. The reset function and the low voltage detection function are available.

### **■** Features

• Detection voltage: 2.0 V to 5.0 V, selectable in 0.1 V step

• Detection voltage accuracy: ±1.5%

• Input voltage:  $V_{DD} = 0.9 \text{ V to } 6.0 \text{ V}$

Hysteresis width: 5% typ.

Current consumption during watchdog timer operation: 3.8 μA typ.

Reset time-out period:

Watchdog time-out period:

14.5 ms typ. (C<sub>POR</sub> = 2200 pF)

24.6 ms typ. (C<sub>WDT</sub> = 470 pF)

Watchdog operation is switchable: Enable, Disable

Watchdog operation voltage range: V<sub>DD</sub> = 2.5 V to 6.0 V

• Watchdog mode switching function\*1: Time-out mode, window mode

• Watchdog input edge is selectable: Rising edge, falling edge, both rising and falling edges

• Product type is selectable: S-1410 Series

(Product with  $\overline{W}$  / T pin (Output:  $\overline{WDO}$  pin))

S-1411 Series

(Product without  $\overline{W}$  / T pin (Output:  $\overline{RST}$  pin,  $\overline{WDO}$  pin))

• Operation temperature range: Ta = -40°C to +105°C

• Lead-free (Sn 100%), halogen-free

### ■ Application

· Power supply monitoring and system monitoring in microcontroller mounted apparatus

### ■ Packages

- TMSOP-8

- HSNT-8(2030)

<sup>\*1.</sup> The S-1411 Series is fixed to the window mode.

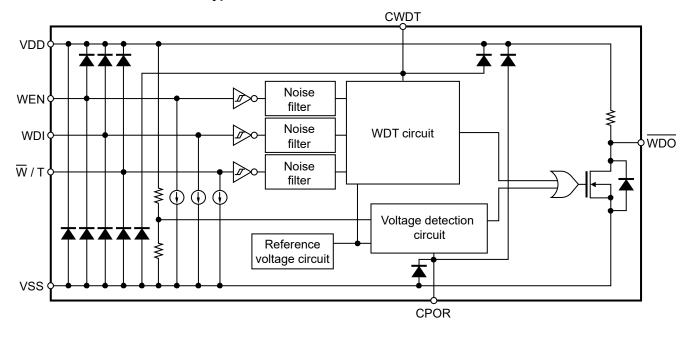

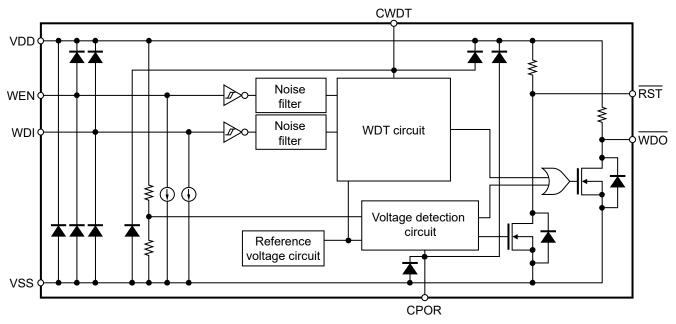

### **■** Block Diagrams

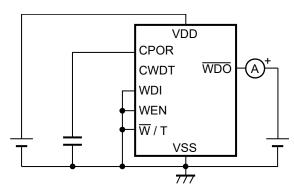

### 1. S-1410 Series A / B / C Type

Figure 1

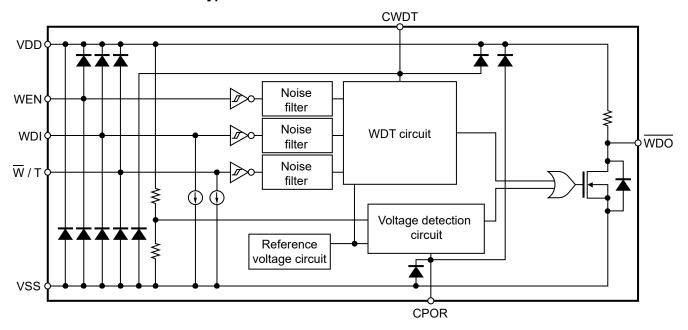

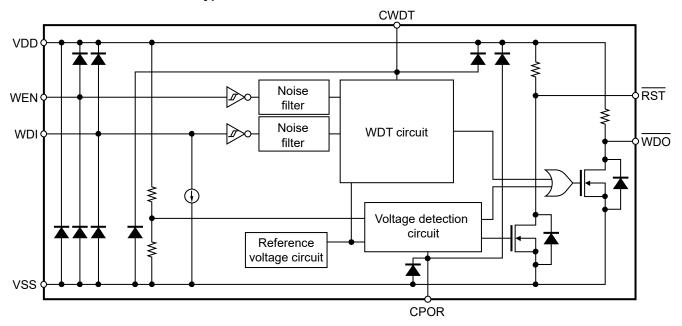

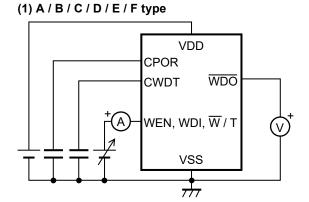

### 2. S-1410 Series D / E / F Type

Figure 2

2 ABLIC Inc.

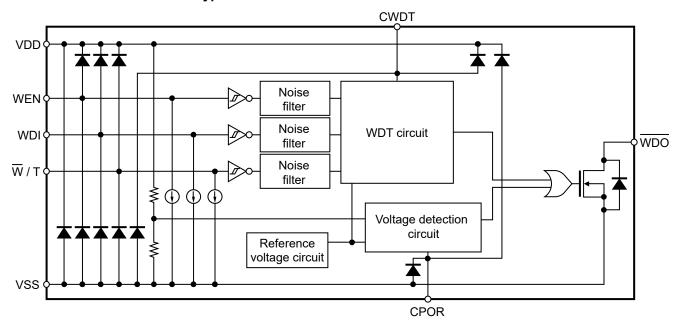

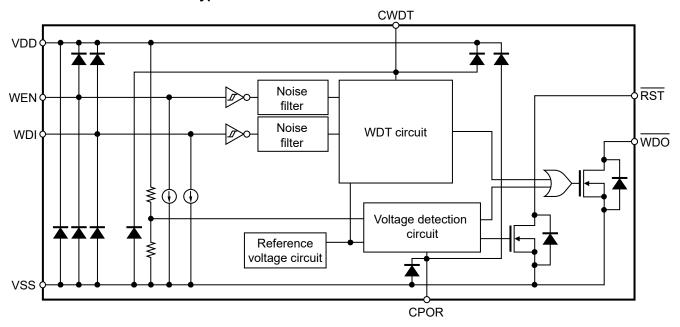

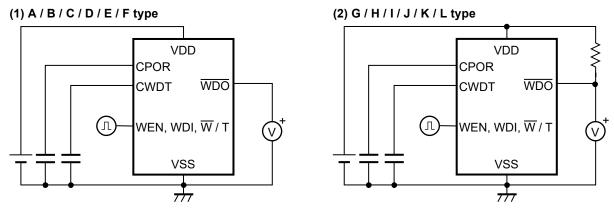

### 3. S-1410 Series G / H / I Type

Figure 3

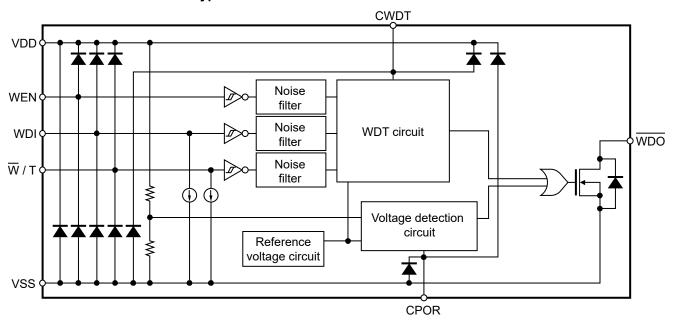

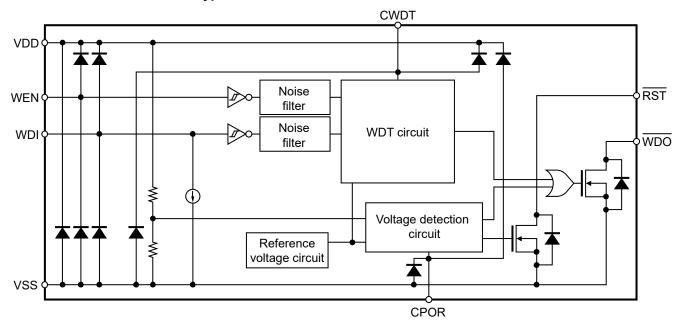

### 4. S-1410 Series J / K / L Type

Figure 4

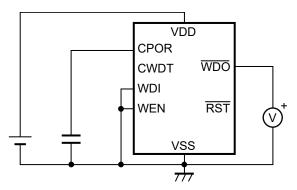

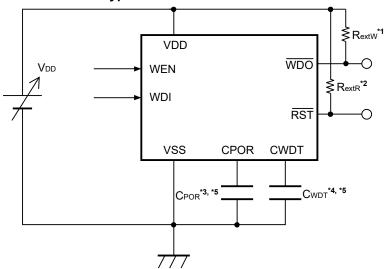

### 5. S-1411 Series A / B / C Type

Figure 5

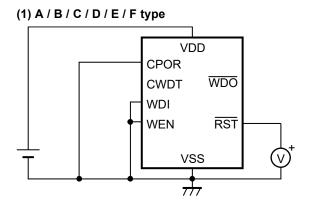

### 6. S-1411 Series D / E / F Type

Figure 6

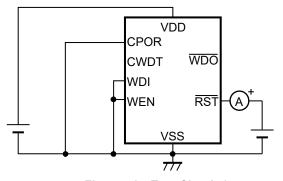

### 7. S-1411 Series G / H / I Type

Figure 7

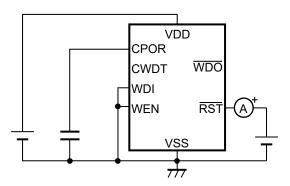

### 8. S-1411 Series J / K / L Type

Figure 8

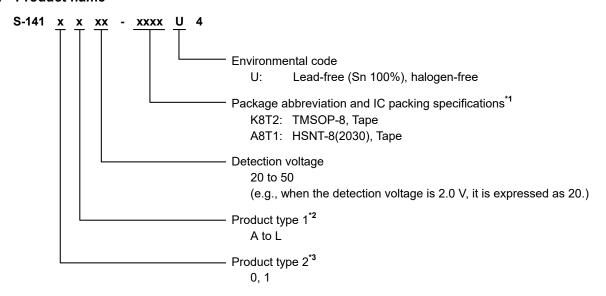

### **■ Product Name Structure**

Users can select the product type, detection voltage, and package type for the S-1410/1411 Series. Refer to

- "1. Product name" regarding the contents of product name, "2. Product type list" regarding the product types,

- "3. Packages" regarding the package drawings.

### 1. Product name

- \*1. Refer to the tape drawing.

- \*2. Refer to "2. Product type list".

- \*3. 0: S-1410 Series (Product with  $\overline{W}$  / T pin)

The WDO pin outputs the signals which are from the watchdog timer circuit and the voltage detection circuit.

1: S-1411 Series (Product without  $\overline{W}$  / T pin)

The  $\overline{\text{WDO}}$  pin outputs the signals which are from the watchdog timer circuit and the voltage detection circuit.

The  $\overline{\mathsf{RST}}$  pin outputs the signal which is from the voltage detection circuit.

The watchdog mode is fixed to the window mode.

### 2. Product type list

Table 1

| Product Type | WEN Pin Logic | Constant Current Source Pull-down for WEN Pin | Input Edge                    | Output Pull-up<br>Resistor |

|--------------|---------------|-----------------------------------------------|-------------------------------|----------------------------|

| Α            | Active "H"    | Available                                     | Rising edge                   | Available                  |

| В            | Active "H"    | Available                                     | Falling edge                  | Available                  |

| С            | Active "H"    | Available                                     | Both rising and falling edges | Available                  |

| D            | Active "L"    | Unavailable                                   | Rising edge                   | Available                  |

| E            | Active "L"    | Unavailable                                   | Falling edge                  | Available                  |

| F            | Active "L"    | Unavailable                                   | Both rising and falling edges | Available                  |

| G            | Active "H"    | Available                                     | Rising edge                   | Unavailable                |

| Н            | Active "H"    | Available                                     | Falling edge                  | Unavailable                |

| I            | Active "H"    | Available                                     | Both rising and falling edges | Unavailable                |

| J            | Active "L"    | Unavailable                                   | Rising edge                   | Unavailable                |

| K            | Active "L"    | Unavailable                                   | Falling edge                  | Unavailable                |

| L            | Active "L"    | Unavailable                                   | Both rising and falling edges | Unavailable                |

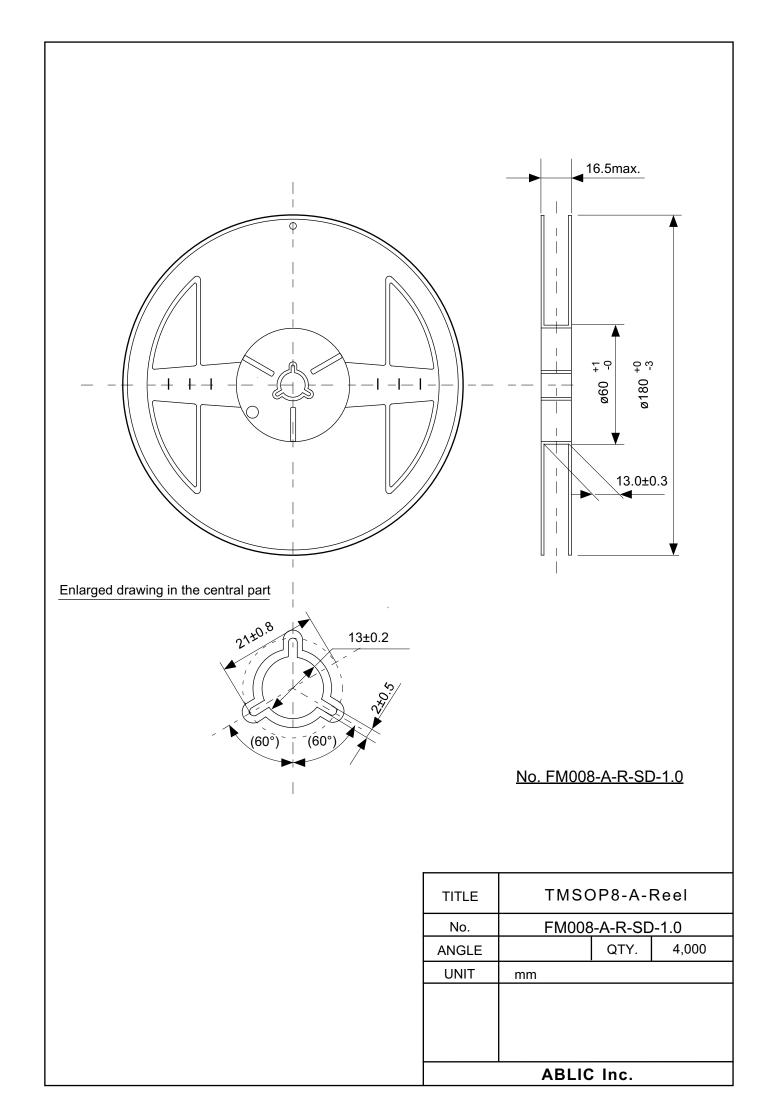

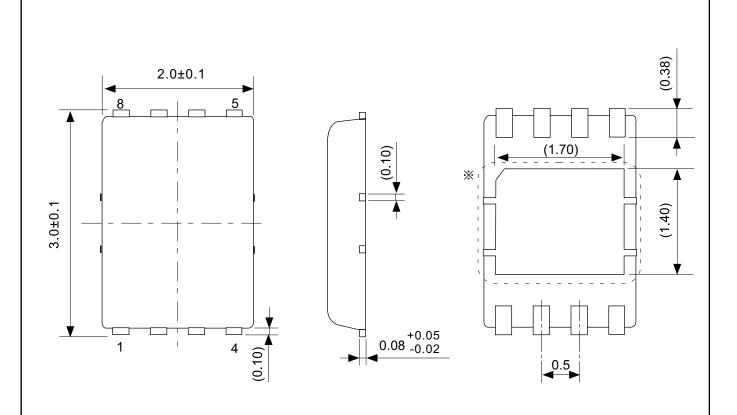

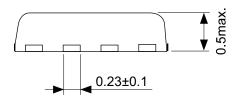

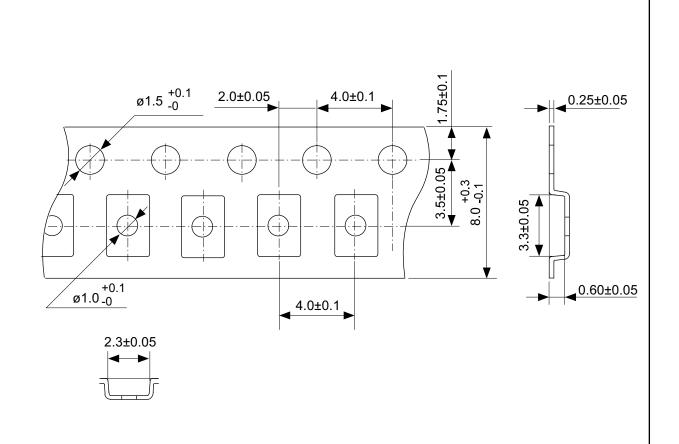

### 3. Packages

Table 2 Package Drawing Codes

| Package Name | Dimension    | Tape         | Reel         | Land         |

|--------------|--------------|--------------|--------------|--------------|

| TMSOP-8      | FM008-A-P-SD | FM008-A-C-SD | FM008-A-R-SD | _            |

| HSNT-8(2030) | PP008-A-P-SD | PP008-A-C-SD | PP008-A-R-SD | PP008-A-L-SD |

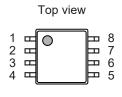

### **■** Pin Configurations

### 1. TMSOP-8

Figure 9

Table 3 S-1410 Series

| Pin No. | Symbol  | Description                             |

|---------|---------|-----------------------------------------|

| 1       | W / T*1 | Watchdog mode switching pin             |

| 2       | CPOR    | Reset time-out period adjustment pin    |

| 3       | CWDT    | Watchdog time-out period adjustment pin |

| 4       | VSS     | GND pin                                 |

| 5       | WEN     | Watchdog enable pin                     |

| 6       | WDO     | Watchdog output and reset output pin    |

| 7       | WDI     | Watchdog input pin                      |

| 8       | VDD     | Voltage input pin                       |

Table 4 S-1411 Series

| Pin No. | Symbol | Description                             |

|---------|--------|-----------------------------------------|

| 1       | RST    | Reset output pin                        |

| 2       | CPOR   | Reset time-out period adjustment pin    |

| 3       | CWDT   | Watchdog time-out period adjustment pin |

| 4       | VSS    | GND pin                                 |

| 5       | WEN    | Watchdog enable pin                     |

| 6       | WDO    | Watchdog output pin                     |

| 7       | WDI    | Watchdog input pin                      |

| 8       | VDD    | Voltage input pin                       |

<sup>\*1.</sup>  $\overline{W}$  / T pin = "H": Time-out mode  $\overline{W}$  / T pin = "L": Window mode

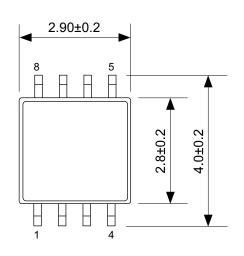

### 2. HSNT-8(2030)

Bottom view

Figure 10

Table 5 S-1410 Series

| Pin No. | Symbol  | Description                             |

|---------|---------|-----------------------------------------|

| 1       | W / T*2 | Watchdog mode switching pin             |

| 2       | CPOR    | Reset time-out period adjustment pin    |

| 3       | CWDT    | Watchdog time-out period adjustment pin |

| 4       | VSS     | GND pin                                 |

| 5       | WEN     | Watchdog enable pin                     |

| 6       | WDO     | Watchdog output and reset output pin    |

| 7       | WDI     | Watchdog input pin                      |

| 8       | VDD     | Voltage input pin                       |

Table 6 S-1411 Series

| Pin No. | Symbol | Description                             |

|---------|--------|-----------------------------------------|

| 1       | RST    | Reset output pin                        |

| 2       | CPOR   | Reset time-out period adjustment pin    |

| 3       | CWDT   | Watchdog time-out period adjustment pin |

| 4       | VSS    | GND pin                                 |

| 5       | WEN    | Watchdog enable pin                     |

| 6       | WDO    | Watchdog output pin                     |

| 7       | WDI    | Watchdog input pin                      |

| 8       | VDD    | Voltage input pin                       |

- **\*1.** Connect the heat sink of backside at shadowed area to the board, and set electric potential GND. However, do not use it as the function of electrode.

- \*2.  $\overline{W}$  / T pin = "H": Time-out mode  $\overline{W}$  / T pin = "L": Window mode

### ■ Pin Functions

Refer to "■ Operations" for details.

### 1. W / T pin (Only S-1410 Series)

This is a pin to switch the watchdog mode.

The S-1410 Series changes to the time-out mode when the  $\overline{W}$  / T pin is "H", and changes to the window mode when the  $\overline{W}$  / T pin is "L". Switching the mode is prohibited during the operation.

The  $\overline{W}$  / T pin is connected to a constant current source (0.3  $\mu$ A typ.) and is pulled down internally.

In addition, the  $\overline{W}$  / T pin has a noise filter. When the power supply voltage is 5.0 V, noise with a minimum pulse width of 200 ns can be eliminated.

### 2. RST pin (Only S-1411 Series)

This is a reset output pin. It outputs "L" when detecting a low voltage.

Be sure to connect an external pull-up resistor ( $R_{extR}$ ) to the  $\overline{RST}$  pin in the product without an output pull-up resistor.

### 3. WDO pin

### 3. 1 S-1410 Series

This pin combines the reset output and the watchdog output (time-out detection, double pulse detection). Be sure to connect an external pull-up resistor ( $R_{extW}$ ) to the  $\overline{WDO}$  pin in the product without an output pull-up resistor. **Table 7** shows the  $\overline{WDO}$  pin output status.

Table 7

| Operation Status                  | WDO Pin         |                 |  |

|-----------------------------------|-----------------|-----------------|--|

| Operation Status                  | ₩ / T Pin = "H" | ₩ / T Pin = "L" |  |

| Normal operation                  | "H"             | "H"             |  |

| Low voltage detection             | "L"             | "L"             |  |

| Time-out detection                | "L"             | "L"             |  |

| Double pulse detection            | "H"             | "L"             |  |

| When watchdog timer is in Disable | "H"             | "H"             |  |

### 3. 2 S-1411 Series

This is the watchdog output (time-out detection, double pulse detection) pin.

Be sure to connect an external pull-up resistor ( $R_{extW}$ ) to the  $\overline{WDO}$  pin in the product without an output pull-up resistor. **Table 8** shows the  $\overline{WDO}$  pin and  $\overline{RST}$  pin output statuses.

Table 8

| Operation Status                  | WDO Pin | RST Pin |

|-----------------------------------|---------|---------|

| Normal operation                  | "H"     | "H"     |

| Low voltage detection             | "L"     | "L"     |

| Time-out detection                | "L"     | "H"     |

| Double pulse detection            | "L"     | "H"     |

| When watchdog timer is in Disable | "H"     | "H"     |

### 4. CPOR pin

This is a pin to connect an adjustment capacitor for reset time-out period ( $C_{POR}$ ) in order to generate the reset time-out period ( $t_{RST}$ ).  $C_{POR}$  is charged and discharged by an internal constant current circuit, and the charge-discharge duration is  $t_{RST}$ .

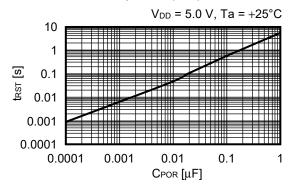

Refer to "**Recommended Operation Conditions**" and consider variation of C<sub>POR</sub> to select an appropriate C<sub>POR</sub>. t<sub>RST</sub> is calculated by using the following equation.

$t_{RST}$  [ms] =  $C_{POR}$  delay coefficient  $\times$   $C_{POR}$  [nF] +  $t_{RSTO}$  [ms]

Table 9

| Item                               | Min. | Тур. | Max. |

|------------------------------------|------|------|------|

| C <sub>POR</sub> delay coefficient | 3.9  | 6.5  | 9.1  |

| t <sub>RST0</sub> [ms]             | 0.0  | 0.2  | 0.6  |

### 5. CWDT pin

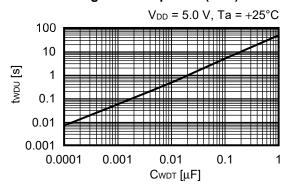

This is a pin to connect an adjustment capacitor for watchdog time-out period (C<sub>WDT</sub>) in order to generate the watchdog time-out period (t<sub>WDU</sub>) and the watchdog double pulse detection time (t<sub>WDL</sub>). C<sub>WDT</sub> is charged and discharged by an internal constant current circuit.

Refer to " $\blacksquare$  Recommended Operation Conditions" and consider variation of  $C_{WDT}$  to select an appropriate  $C_{WDT}$ .  $t_{WDU}$  is calculated by using the following equation.

$t_{WDU}$  [ms] =  $C_{WDT}$  delay coefficient  $1 \times C_{WDT}$  [nF] +  $t_{WDU0}$  [ms]

Table 10

| Item                     | Min. | Тур. | Max. |

|--------------------------|------|------|------|

| Cwdt delay coefficient 1 | 30   | 50   | 70   |

| twouo [ms]               | 0.0  | 1.1  | 3.0  |

In addition, twoL is calculated by using the following equation.

$$t_{WDL} = \frac{t_{WDU}}{32}$$

### 5. 1 Cautions on watchdog double pulse detection time

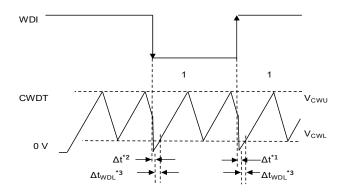

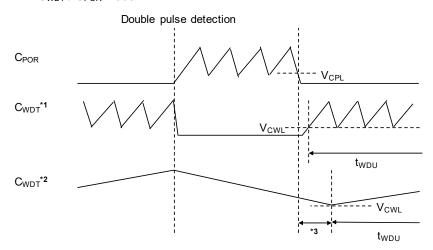

The watchdog double pulse detection time (twDL) noted in "■ Electrical Characteristics" is a value with a starting point at the time when the CWDT pin voltage (VcWDT) begins to rise from the CWDT charge lower limit threshold (VcWL).

The double pulse detection in window mode is performed even during  $\Delta t_{WDL}$  shown in **Timing Diagram 7-4**. Therefore, if setting to a value with a starting point at the time when  $V_{CWDT}$  begins to rise from 0 V, the watchdog double pulse detection time ( $t_{WDL2}$ ) is calculated adding  $\Delta t_{WDL}$  as shown in the following equations.

$t_{WDL2}$  [ms] =  $t_{WDL} + \Delta t_{WDL}$  [ms]

$\Delta t_{WDL}$  [ms] = C<sub>WDT</sub> delay coefficient 2 × C<sub>WDT</sub> [nF] + t<sub>WDL0</sub> [ms]

Table 11

|                          | Tubio II |      |      |

|--------------------------|----------|------|------|

| Item                     | Min.     | Тур. | Max. |

| Cwdt delay coefficient 2 | 0.00     | 0.27 | 0.65 |

| twDL0 [ms]               | 0.00     | 0.01 | 0.02 |

# 105°C OPERATION, 3.8 $\mu$ A CURRENT CONSUMPTION WATCHDOG TIMER WITH RESET FUNCTION S-1410/1411 Series Rev.2.5 $_{00}$

### 6. WEN pin

This is a pin to switch Enable / Disable of the watchdog timer.

The voltage detection circuit independently operates at all times regardless of the watchdog timer operation.

In addition, the WEN pin has a noise filter. When the power supply voltage is 5.0 V, noise with a minimum pulse width of 200 ns can be eliminated.

### 6. 1 S-1410/1411 Series A / B / C / G / H / I type (WEN pin logic active "H" product)

The watchdog timer goes to Enable if the input is "H", and the charge-discharge operation is performed at the CWDT pin.

The WEN pin is connected to a constant current source (0.3 µA typ.) and is pulled down internally.

### 6. 2 S-1410/1411 Series D / E / F / J / K / L type (WEN pin logic active "L" product)

The watchdog timer goes to Enable if the input is "L", and the charge-discharge operation is performed at the CWDT pin.

The WEN pin is not pulled down internally.

### 7. WDI pin

This is an input pin to receive a signal from the monitored object. By inputting an edge at an appropriate timing, the WDI pin confirms the normal operation of the monitored object.

The WDI pin is connected to a constant current source (0.3  $\mu$ A typ.) and is pulled down internally.

If the WEN pin is in Disable after the initialization and reset release are performed subsequent to the power supply voltage rise, the WDI pin will be able to receive input signals after the WEN pin goes to Enable and then the input setup time (tiset) elapses.

In addition, the WDI pin has a noise filter. When the power supply voltage is 5.0 V, noise with a minimum pulse width of 200 ns can be eliminated.

### ■ Absolute Maximum Ratings

Table 12

(Ta = +25°C unless otherwise specified)

|                                            | Item             | Symbol             | Absolute Maximum Rating                                  | Unit |

|--------------------------------------------|------------------|--------------------|----------------------------------------------------------|------|

| VDD pin voltage                            |                  | $V_{DD}$           | $V_{SS} - 0.3$ to $V_{SS} + 7.0$                         | V    |

| WDI pin voltage                            |                  | $V_{WDI}$          | $V_{SS} - 0.3 \text{ to } V_{DD} + 0.3 \le V_{SS} + 7.0$ | V    |

| WEN pin voltage                            |                  | $V_{WEN}$          | $V_{SS} - 0.3 \text{ to } V_{DD} + 0.3 \le V_{SS} + 7.0$ | V    |

| $\overline{W}$ / T pin voltage             |                  | V <sub>w</sub> / T | $V_{SS} - 0.3 \text{ to } V_{DD} + 0.3 \le V_{SS} + 7.0$ | V    |

| CPOR pin voltage                           |                  | Vcpor              | $V_{SS} - 0.3 \text{ to } V_{DD} + 0.3 \le V_{SS} + 7.0$ | V    |

| CWDT pin voltage                           |                  | V <sub>CWDT</sub>  | $V_{SS} - 0.3 \text{ to } V_{DD} + 0.3 \le V_{SS} + 7.0$ | V    |

| DCT nin voltage                            | A/B/C/D/E/F type | VRST               | $V_{SS} - 0.3 \text{ to } V_{DD} + 0.3 \le V_{SS} + 7.0$ | V    |

| RST pin voltage                            | G/H/I/J/K/L type |                    | $V_{SS} - 0.3$ to $V_{SS} + 7.0$                         | V    |

| WDO nin voltage                            | A/B/C/D/E/F type | - V <sub>WDO</sub> | $V_{SS} - 0.3 \text{ to } V_{DD} + 0.3 \le V_{SS} + 7.0$ | V    |

| WDO pin voltage G / H / I / J / K / L type |                  | ▼ WDO              | $V_{SS} - 0.3$ to $V_{SS} + 7.0$                         | V    |

| Operation ambient temperature              |                  | Topr               | -40 to +105                                              | °C   |

| Storage temperature                        |                  | T <sub>stg</sub>   | -40 to +150                                              | °C   |

Caution The absolute maximum ratings are rated values exceeding which the product could suffer physical damage. These values must therefore not be exceeded under any conditions.

### **■** Thermal Resistance Value

Table 13

| Item                                                 | Symbol | Condition    |         | Min. | Тур. | Max. | Unit |

|------------------------------------------------------|--------|--------------|---------|------|------|------|------|

| Junction-to-ambient thermal resistance <sup>*1</sup> | θја    | TMSOP-8      | Board A | 1    | 160  | 1    | °C/W |

|                                                      |        |              | Board B | _    | 133  | -    | °C/W |

|                                                      |        |              | Board C | -    | -    | 1    | °C/W |

|                                                      |        |              | Board D | 1    | 1    | 1    | °C/W |

|                                                      |        |              | Board E | 1    | ı    | 1    | °C/W |

|                                                      |        | HSNT-8(2030) | Board A | 1    | 181  | 1    | °C/W |

|                                                      |        |              | Board B | -    | 135  | -    | °C/W |

|                                                      |        |              | Board C | _    | 40   | -    | °C/W |

|                                                      |        |              | Board D | -    | 42   | -    | °C/W |

|                                                      |        |              | Board E | _    | 32   | _    | °C/W |

<sup>\*1.</sup> Test environment: compliance with JEDEC STANDARD JESD51-2A

**Remark** Refer to "■ **Power Dissipation**" and "**Test Board**" for details.

### **■** Recommended Operation Conditions

Table 14

| Table 14                                            |                      |                                               |      |      |      |      |  |  |

|-----------------------------------------------------|----------------------|-----------------------------------------------|------|------|------|------|--|--|

| Item                                                | Symbol               | Condition                                     | Min. | Тур. | Max. | Unit |  |  |

| VDD : "                                             | .,                   | Voltage detection circuit                     | 0.9  | _    | 6.0  | V    |  |  |

| VDD pin voltage                                     | $V_{DD}$             | Watchdog timer circuit                        | 2.5  | _    | 6.0  | V    |  |  |

| Set detection voltage                               | -V <sub>DET(S)</sub> | 0.1 V step                                    | 2.0  | _    | 5.0  | V    |  |  |

| External pull-up resistor for RST pin               | R <sub>extR</sub>    | S-1411 Series G / H / I / J / K / L type      | 10   | 100  | -    | kΩ   |  |  |

| External pull-up resistor for WDO pin               | R <sub>extW</sub>    | S-1410/1411 Series G / H / I / J / K / L type | 10   | 100  | -    | kΩ   |  |  |

| Adjustment capacitance for reset time-out period    | C <sub>POR</sub>     | -                                             | 0.1  | 2.2  | 1000 | nF   |  |  |

| Adjustment capacitance for watchdog time-out period | Сwdт                 | -                                             | 0.1  | 0.47 | 1000 | nF   |  |  |

### **■** Electrical Characteristics

### 1. S-1410 Series

Table 15 (1 / 2)

(WEN pin logic active "H" product,  $V_{DD} = 5.0 \text{ V}$ , Ta = +25°C unless otherwise specified)

| Item                                                | Symbol            | Condi                                                                                   | •                            | Min.                     | Тур.                         | Max.                       | Unit      | Test<br>Circuit |

|-----------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------|------------------------------|--------------------------|------------------------------|----------------------------|-----------|-----------------|

| Detection voltage*1                                 | -V <sub>DET</sub> | -                                                                                       | -V <sub>DET(S)</sub> × 0.985 | -V <sub>DET(S)</sub>     | -V <sub>DET(S)</sub> × 1.015 | V                          | 1         |                 |

| Hysteresis width                                    | V <sub>HYS</sub>  |                                                                                         |                              | -V <sub>DET</sub> × 0.03 | $-V_{DET} \times 0.05$       | -V <sub>DET</sub> × 0.07   | V         | 1               |

| Current consumption during watchdog timer operation | Iss1              | $V_{WEN} = V_{DD}$                                                                      |                              | _                        | 3.8                          | 7.8                        | μΑ        | 2               |

| Current consumption during watchdog timer stop      | I <sub>SS2</sub>  | V <sub>WEN</sub> = 0 V                                                                  |                              | _                        | 2.7                          | 5.7                        | μΑ        | 2               |

| Watchdog output voltage "H"                         | $V_{WOH}$         | Only A / B / C / D / E / F type                                                         |                              | $V_{DD}-1.0$             | _                            | _                          | V         | 5               |

| Watchdog output voltage "L"                         | $V_{WOL}$         | External pull-up resistor of 100 k $\Omega$ is connected for G / H / I / J / K / L type |                              | _                        | _                            | 0.4                        | V         | 6               |

| Watchdog output pull-up resistance                  | Rwup              | Only A / B / C / D / E / F type                                                         |                              | 2.0                      | 5.88                         | 12.5                       | $M\Omega$ | _               |

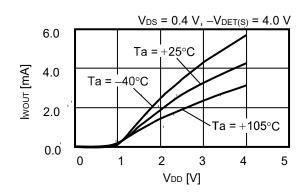

|                                                     | I <sub>WOUT</sub> | V <sub>DS</sub> = 0.4 V                                                                 | $V_{DD} = 1.5 \text{ V}$     | 0.6                      | 1.1                          | _                          | mA        | 7               |

| Watchdog output current                             |                   |                                                                                         | $V_{DD} = 1.8 \text{ V}$     | 1.1                      | 1.6                          | _                          | mΑ        | 7               |

| Watchdog output current                             |                   | VDS - 0.4 V                                                                             | $V_{DD} = 2.5 \text{ V}$     | 2.1                      | 2.6                          | _                          | mA        | 7               |

|                                                     |                   |                                                                                         | $V_{DD} = 3.0 \text{ V}$     | 2.8                      | 3.3                          | _                          | mΑ        | 7               |

| Watchdog output leakage current                     | Iwleak            | V <sub>DS</sub> = 6.0 V, V <sub>DD</sub> = 6.0 V                                        |                              | _                        | _                            | 0.096                      | μΑ        | 8               |

| Input pin voltage 1 "H"                             | V <sub>SH1</sub>  | WEN pin                                                                                 |                              | $0.7 \times V_{DD}$      | _                            | _                          | V         | 9               |

| Input pin voltage 1 "L"                             | V <sub>SL1</sub>  | WEN pin                                                                                 |                              |                          | _                            | $0.3 \times V_{DD}$        | V         | 9               |

| Input pin voltage 2 "H"                             | V <sub>SH2</sub>  | W / T pin                                                                               |                              | $0.7 \times V_{DD}$      | _                            | _                          | V         | 9               |

| Input pin voltage 2 "L"                             | V <sub>SL2</sub>  | W / T pin                                                                               |                              | _                        | _                            | $0.3 \times V_{\text{DD}}$ | V         | 9               |

| Input pin voltage 3 "H"                             | V <sub>SH3</sub>  | WDI pin                                                                                 |                              | $0.7 \times V_{DD}$      | _                            | _                          | V         | 9               |

| Input pin voltage 3 "L"                             | V <sub>SL3</sub>  | WDI pin                                                                                 |                              | _                        | _                            | $0.3 \times V_{\text{DD}}$ | V         | 9               |

Table 15 (2 / 2)

(WEN pin logic active "H" product,  $V_{DD} = 5.0 \text{ V}$ ,  $Ta = +25^{\circ}\text{C}$  unless otherwise specified)

| Item                                 | Symbol            | Condition                                                                  |                         | Min. | Тур. | Max. | Unit | Test<br>Circuit |

|--------------------------------------|-------------------|----------------------------------------------------------------------------|-------------------------|------|------|------|------|-----------------|

| Input pin current 1 "H"              | l.                | WEN pin,                                                                   | A/B/C<br>/G/H/I<br>type | -    | 0.3  | 1.0  | μΑ   | 9               |

|                                      | Ish1              | V <sub>DD</sub> = 6.0 V,<br>Input pin voltage = 6.0 V                      | D/E/F<br>/J/K/L<br>type | -0.1 | -    | 0.1  | μА   | 9               |

| Input pin current 1 "L"              | I <sub>SL1</sub>  | WEN pin, V <sub>DD</sub> = 6.0 \<br>Input pin voltage = 0                  | •                       | -0.1 | _    | 0.1  | μΑ   | 9               |

| Input pin current 2 "H"              | I <sub>SH2</sub>  | W / T pin,<br>V <sub>DD</sub> = 6.0 V, Input pin voltage = 6.0 V           |                         | -    | 0.3  | 1.0  | μΑ   | 9               |

| Input pin current 2 "L"              | I <sub>SL2</sub>  | W / T pin,<br>V <sub>DD</sub> = 6.0 V, Input pin voltage = 0 V             |                         | -0.1 | _    | 0.1  | μΑ   | 9               |

| Input pin current 3 "H"              | I <sub>SH3</sub>  | WDI pin, $V_{DD} = 6.0 \text{ V}$ ,<br>Input pin voltage = $6.0 \text{ V}$ |                         | ı    | 0.3  | 1.0  | μΑ   | 9               |

| Input pin current 3 "L"              | I <sub>SL3</sub>  | WDI pin, $V_{DD} = 6.0 \text{ V}$ ,<br>Input pin voltage = 0 V             |                         | -0.1 | _    | 0.1  | μΑ   | 9               |

| Input pulse width "H"*2              | thigh1            | Timing Diagram 1                                                           |                         | 1.5  | _    | _    | μs   | 10              |

| Input pulse width "L"*2              | t <sub>low1</sub> | Timing Diagram 1                                                           |                         | 1.5  | _    | _    | μs   | 10              |

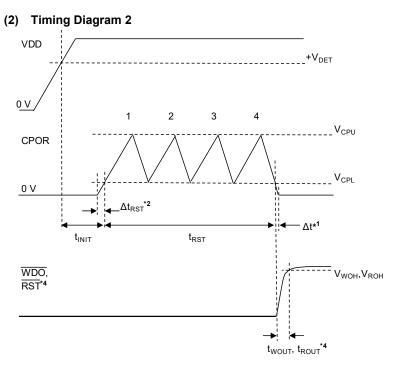

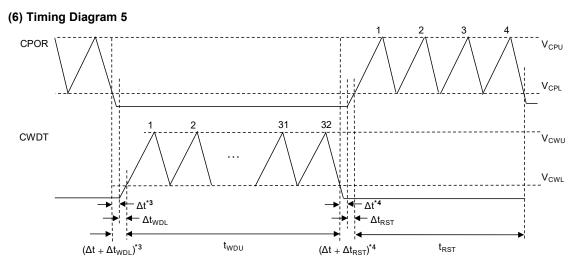

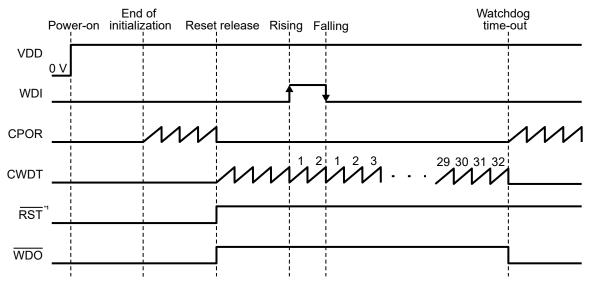

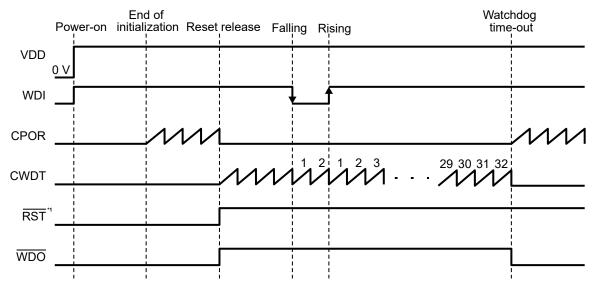

| Reset time-out period                | t <sub>RST</sub>  | C <sub>POR</sub> = 2200 pF,<br>Timing Diagram 2, 5                         |                         | 8.7  | 14.5 | 20   | ms   | 3               |

| Watchdog time-out period             | twou              | C <sub>WDT</sub> = 470 pF,<br>Timing Diagram 4, 5                          |                         | 15   | 24.6 | 34   | ms   | 3               |

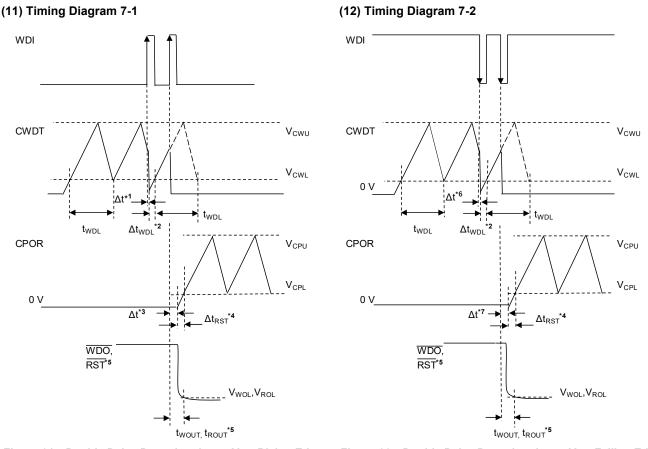

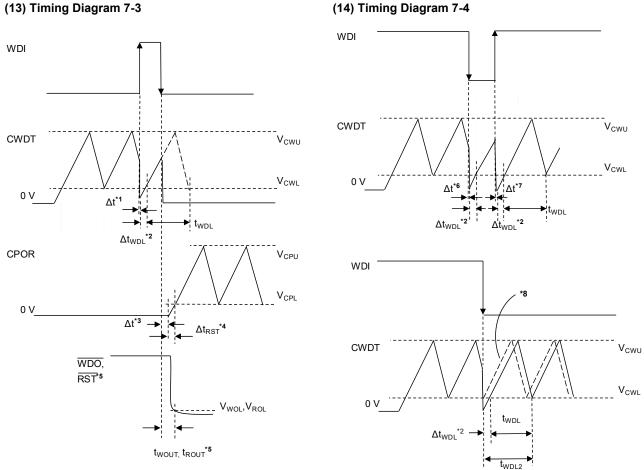

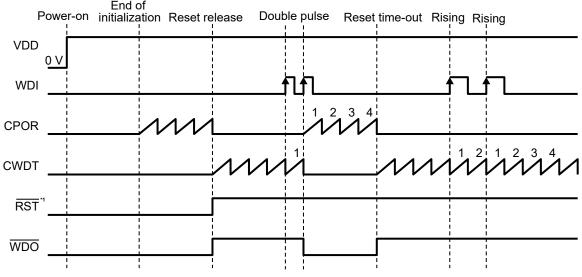

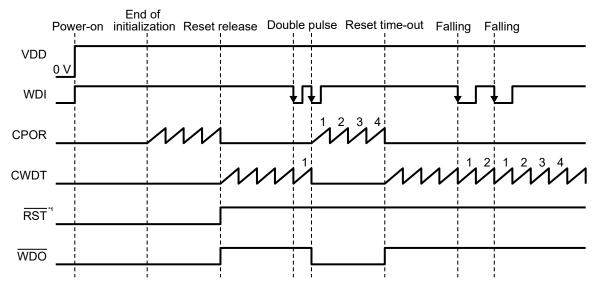

| Watchdog double pulse detection time | twoL              | C <sub>WDT</sub> = 470 pF,<br>Timing Diagram 7-1 to 7-4                    |                         | 461  | 769  | 1077 | μs   | 4               |

| Watchdog output delay time           | twout             | Timing Diagram 2, 3-2, 7-1 to 7-3                                          |                         | -    | 25   | 40   | μs   | 3               |

| Reset output delay time              | t <sub>ROUT</sub> | Timing Diagram 2, 7-1 to 7-3                                               |                         | _    | 25   | 40   | μs   | 3               |

| Input setup time                     | t <sub>iset</sub> | Timing Diagram 4                                                           |                         | 1.0  | _    | _    | μs   | 3               |

<sup>\*1. -</sup>V<sub>DET</sub>: Actual detection voltage, -V<sub>DET(S)</sub>: Set detection voltage

<sup>\*2.</sup> Inputs to the WEN pin and the WDI pin should be greater than or equal to the min. value specified in "■ Electrical Characteristics".

### 2. S-1411 Series

### Table 16 (1 / 2)

(WEN pin logic active "H" product,  $V_{DD} = 5.0 \text{ V}$ , Ta = +25°C unless otherwise specified)

| Item                                                | Symbol             | N pin logic active "<br>Condi                    | •                        | Min.                                 | Тур.                   | Max.                         | Unit      | Test<br>Circuit |

|-----------------------------------------------------|--------------------|--------------------------------------------------|--------------------------|--------------------------------------|------------------------|------------------------------|-----------|-----------------|

| Detection voltage*1                                 | -V <sub>DET</sub>  | -                                                |                          | $-V_{\text{DET(S)}} \\ \times 0.985$ | -V <sub>DET(S)</sub>   | -V <sub>DET(S)</sub> × 1.015 | V         | 11              |

| Hysteresis width                                    | V <sub>HYS</sub>   | -                                                |                          | -V <sub>DET</sub> × 0.03             | $-V_{DET} \times 0.05$ | -V <sub>DET</sub> × 0.07     | V         | 11              |

| Current consumption during watchdog timer operation | Iss <sub>1</sub>   | V <sub>WEN</sub> = V <sub>DD</sub>               |                          | _                                    | 3.8                    | 7.8                          | μΑ        | 12              |

| Current consumption during watchdog timer stop      | I <sub>SS2</sub>   | V <sub>WEN</sub> = 0 V                           |                          | _                                    | 2.7                    | 5.7                          | μΑ        | 12              |

| Reset output voltage "H"                            | V <sub>ROH</sub>   | Only A / B / C / D                               | / E / F type             | $V_{DD} - 1.0$                       | _                      | _                            | V         | 15              |

| Reset output voltage "L"                            | V <sub>ROL</sub>   | External pull-up res connected for G / H         |                          | _                                    | -                      | 0.4                          | V         | 16              |

| Reset output pull-up resistance                     | R <sub>RUP</sub>   | Only A / B / C / D / E / F type                  |                          | 2.0                                  | 5.88                   | 12.5                         | $M\Omega$ | _               |

|                                                     | I <sub>ROUT</sub>  | V <sub>DS</sub> = 0.4 V                          | V <sub>DD</sub> = 1.5 V  | 0.6                                  | 1.1                    | _                            | mΑ        | 17              |

| Reset output current                                |                    |                                                  | $V_{DD} = 1.8 \text{ V}$ | 1.1                                  | 1.6                    | _                            | mΑ        | 17              |

|                                                     |                    |                                                  | $V_{DD} = 2.5 \text{ V}$ | 2.1                                  | 2.6                    | _                            | mA        | 17              |

|                                                     |                    |                                                  | $V_{DD} = 3.0 \text{ V}$ | 2.8                                  | 3.3                    | _                            | mA        | 17              |

| Reset output leakage current                        | IRLEAK             | $V_{DS} = 6.0 \text{ V}, V_{DD} =$               | = 6.0 V                  | _                                    | _                      | 0.096                        | μΑ        | 18              |

| Watchdog output voltage "H"                         | V <sub>WOH</sub>   | Only A / B / C / D                               | / E / F type             | $V_{DD} - 1.0$                       | _                      | _                            | V         | 19              |

| Watchdog output voltage "L"                         | VwoL               | External pull-up res connected for G / F         |                          | _                                    | _                      | 0.4                          | V         | 20              |

| Watchdog output pull-up resistance                  | R <sub>WUP</sub>   | Only A / B / C / D                               | / E / F type             | 2.0                                  | 5.88                   | 12.5                         | ΜΩ        | _               |

|                                                     |                    |                                                  | V <sub>DD</sub> = 1.5 V  | 0.6                                  | 1.1                    | _                            | mΑ        | 21              |

| Watchdog output current                             | Iwout              | V <sub>DS</sub> = 0.4 V                          | $V_{DD} = 1.8 \text{ V}$ | 1.1                                  | 1.6                    | _                            | mΑ        | 21              |

| Watchdog output current                             | IWOUT              | VDS - 0.4 V                                      | $V_{DD} = 2.5 \text{ V}$ | 2.1                                  | 2.6                    | _                            | mΑ        | 21              |

|                                                     |                    |                                                  | $V_{DD} = 3.0 \text{ V}$ | 2.8                                  | 3.3                    | _                            | mΑ        | 21              |

| Watchdog output leakage current                     | I <sub>WLEAK</sub> | V <sub>DS</sub> = 6.0 V, V <sub>DD</sub> = 6.0 V |                          | _                                    | -                      | 0.096                        | μΑ        | 22              |

| Input pin voltage 1 "H"                             | V <sub>SH1</sub>   | WEN pin                                          |                          | $0.7 \times V_{DD}$                  | _                      | -                            | V         | 23              |

| Input pin voltage 1 "L"                             | V <sub>SL1</sub>   | WEN pin                                          |                          | _                                    | _                      | $0.3 \times V_{\text{DD}}$   | V         | 23              |

| Input pin voltage 3 "H"                             | V <sub>SH3</sub>   | WDI pin                                          |                          | $0.7 \times V_{\text{DD}}$           | _                      | _                            | V         | 23              |

| Input pin voltage 3 "L"                             | $V_{SL3}$          | WDI pin                                          |                          | _                                    | _                      | $0.3 \times V_{\text{DD}}$   | V         | 23              |

Table 16 (2 / 2)

(WEN pin logic active "H" product,  $V_{DD} = 5.0 \text{ V}$ , Ta = +25°C unless otherwise specified)

| ltem                                     | Symbol             | Condition                                                        | ,                       | Min. | Тур. | Max. | Unit | Test<br>Circuit |

|------------------------------------------|--------------------|------------------------------------------------------------------|-------------------------|------|------|------|------|-----------------|

| Input pin current 1 "H" I <sub>SH1</sub> |                    | WEN pin,                                                         | A/B/C<br>/G/H/I<br>type | -    | 0.3  | 1.0  | μΑ   | 23              |

|                                          | ISH1               | V <sub>DD</sub> = 6.0 V,<br>Input pin voltage = 6.0 V            | D/E/F<br>/J/K/L<br>type | -0.1 | ı    | 0.1  | μΑ   | 23              |

| Input pin current 1 "L"                  | I <sub>SL1</sub>   | WEN pin, V <sub>DD</sub> = 6.0 V,<br>Input pin voltage = 0 V     |                         | -0.1 | ı    | 0.1  | μΑ   | 23              |

| Input pin current 3 "H"                  | I <sub>SH3</sub>   | WDI pin, V <sub>DD</sub> = 6.0 V,<br>Input pin voltage = 6.0 V   |                         | -    | 0.3  | 1.0  | μΑ   | 23              |

| Input pin current 3 "L"                  | I <sub>SL3</sub>   | WDI pin, $V_{DD} = 6.0 \text{ V}$ ,<br>Input pin voltage = 0 V   |                         | -0.1 | I    | 0.1  | μΑ   | 23              |

| Input pulse width "H"*2                  | t <sub>high1</sub> | Timing Diagram 1                                                 | 1.5                     | _    | -    | μs   | 24   |                 |

| Input pulse width "L"*2                  | t <sub>low1</sub>  | Timing Diagram 1                                                 |                         | 1.5  | 1    | _    | μs   | 24              |

| Reset time-out period                    | t <sub>RST</sub>   | C <sub>POR</sub> = 2200 pF,<br>Timing Diagram 2, 5               |                         | 8.7  | 14.5 | 20   | ms   | 13              |

| Watchdog time-out period                 | twou               | C <sub>WDT</sub> = 470 pF,<br><b>Timing Diagram 4</b> , <b>5</b> |                         | 15   | 24.6 | 34   | ms   | 13              |

| Watchdog double pulse detection time     | twdL               | C <sub>WDT</sub> = 470 pF,<br>Timing Diagram 7-1 to 7-4          |                         | 461  | 769  | 1077 | μs   | 14              |

| Watchdog output delay time               | twouт              | Timing Diagram 2, 3-2, 7-1 to 7-3                                |                         | -    | 25   | 40   | μs   | 13              |

| Reset output delay time                  | t <sub>ROUT</sub>  | Timing Diagram 2, 3-1, 7-1 to 7-3                                |                         | _    | 25   | 40   | μs   | 13              |

| Input setup time                         | t <sub>iset</sub>  | Timing Diagram 4                                                 |                         | 1.0  | _    | _    | μs   | 13              |

<sup>\*1. -</sup>V<sub>DET</sub>: Actual detection voltage, -V<sub>DET(S)</sub>: Set detection voltage

### **■** Timing Diagrams on Electrical Characteristics

# WEN VSH1 VSL1 VSL1 VSL1 VSL3 VSL3 VSL3

Figure 11 Input Pulse Width

<sup>\*2.</sup> Inputs to the WEN pin and the WDI pin should be greater than or equal to the min. value specified in "■ Electrical Characteristics".

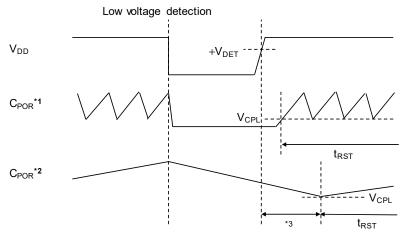

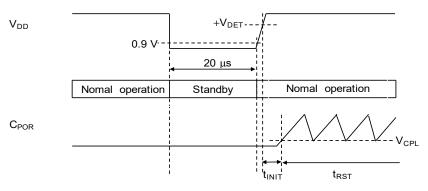

Figure 12 VDD Rising

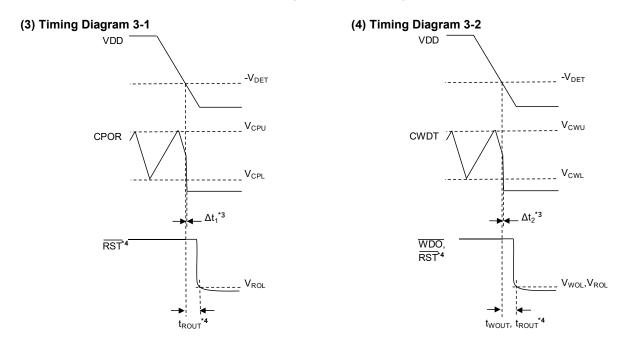

Figure 13  $V_{DD}$  Falling during CPOR Pin Charge Operation Figure 14  $V_{DD}$  Falling during CWDT Pin Charge Operation

- \*1. The CPOR pin voltage fall delay time (\(\Delta\text{t}\) is sufficiently small compared to the reset time-out period (t\_RST).

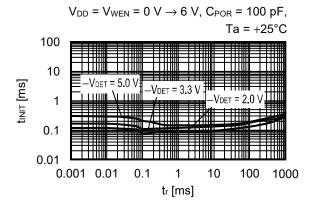

- \*2. The time (∆t<sub>RST</sub>) the CPOR pin voltage (V<sub>CPOR</sub>) reaches the CPOR charge lower limit threshold (V<sub>CPL</sub>) from 0 V is proportional to the adjustment capacitance for reset time-out period (C<sub>POR</sub>). Thus, large C<sub>POR</sub> results in large ∆t<sub>RST</sub>. Refer to "12. Initialization time (t<sub>INIT</sub>) vs. Power supply voltage rise time (t<sub>r</sub>)" in "■ Characteristics (Typical Data)".

- \*3. CPOR pin voltage forced fall delay time ( $\Delta t_1$ ) and the CWDT pin voltage forced fall delay time ( $\Delta t_2$ ) is sufficiently small compared to  $t_{RST}$  in **Timing Diagram 2**.

- \*4. Only the S-1411 Series

Remark VCPU: CPOR charge upper limit threshold (1.25 V typ.), VCPL: CPOR charge lower limit threshold (0.20 V typ.) VCWU: CWDT charge upper limit threshold (1.25 V typ.), VCWL: CWDT charge lower limit threshold (0.20 V typ.)

# (5) Timing Diagram 4 WEN V<sub>SH1</sub> V<sub>SL1</sub> CWDT V<sub>CWU</sub> V<sub>CWL</sub> At\*1 At<sub>WDL\*2</sub> t<sub>WDU</sub>

Figure 15 Counter Reset due to VWEN

Figure 16 Watchdog Time-out Detection

- \*1. CWDT pin voltage forced fall delay time ( $\Delta t$ ) is sufficiently small compared to the watchdog time-out period ( $t_{WDU}$ ).

- \*2. The CWDT pin voltage rise delay time ( $t_{iset} + \Delta t_{WDL}$ ) is sufficiently small (less than 1%) compared to  $t_{WDU}$ .

- \*3. The delay time (Δt + Δtwpl) from when the CPOR pin voltage (VcPOR) falls to the CPOR charge lower limit threshold (VcPl) to when the CWDT pin voltage (VcWpt) reaches the CWDT charge lower limit threshold (VcWl) is sufficiently small (less than 1%) compared to twpl.

- \*4. The delay time ( $\Delta t + \Delta t_{RST}$ ) from when  $V_{CWDT}$  falls to  $V_{CWL}$  to when  $V_{CPOR}$  reaches  $V_{CPL}$  is sufficiently small (less than 5%) compared to reset time-out period ( $t_{RST}$ ).

### **Remark** $t_{iset}$ : Input setup time (less than 1 $\mu s$ )

The time from when V<sub>WEN</sub> exceeds V<sub>SH1</sub> (t<sub>SH1</sub>) to when the WDI pin is able to receive input signals (t<sub>acp</sub>).

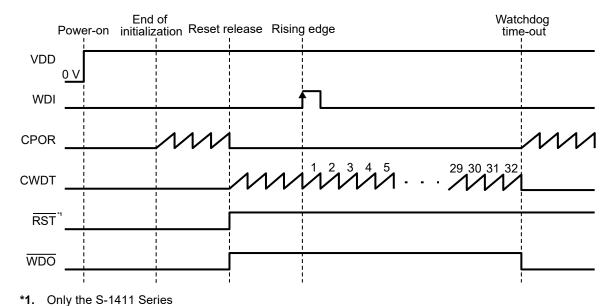

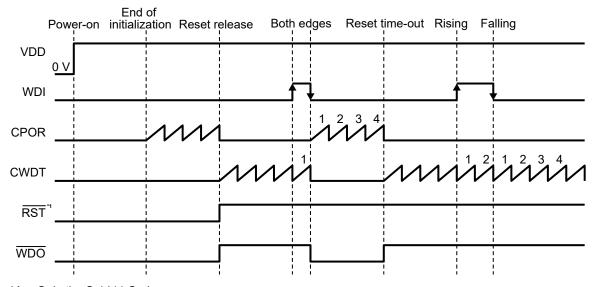

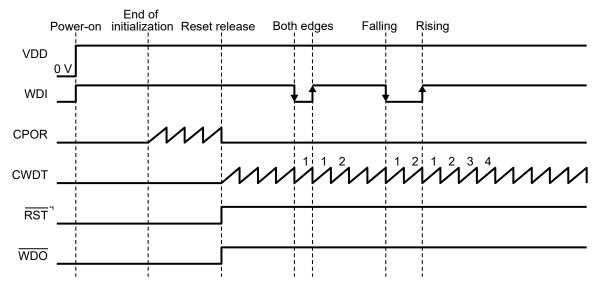

### (7) Timing Diagram 6-1

Figure 17 VwDI Rising Edge

### (8) Timing Diagram 6-2

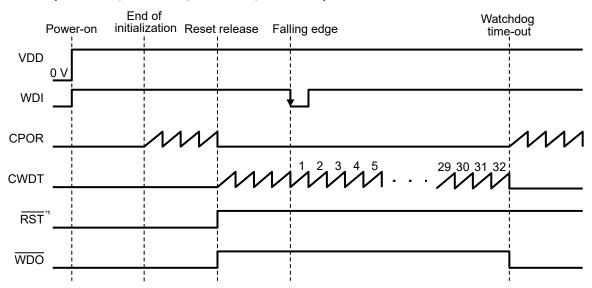

Figure 18 V<sub>WDI</sub> Falling Edge

### (9) Timing Diagram 6-3

Figure 19 V<sub>WDI</sub> Both Rising and Falling Edges 1

### (10) Timing Diagram 6-4

Figure 20 VwDI Both Rising and Falling Edges 2

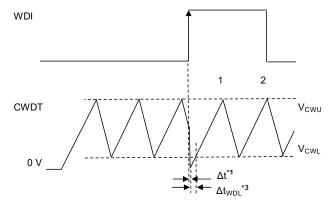

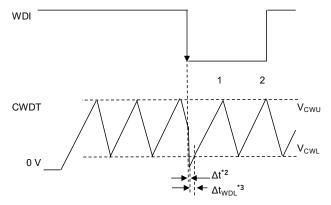

- \*1. The delay time ( $\Delta t$ ) from the WDI pin voltage ( $V_{WDI}$ ) rising edge to the CWDT pin voltage ( $V_{CWDT}$ ) rising start is sufficiently small (less than 1%) compared to  $t_{WDU}$  in **Timing Diagram 4** and **5**.

- \*2. The delay time ( $\Delta t$ ) from the  $V_{WDI}$  falling edge to the  $V_{CWDT}$  rising start is sufficiently small (less than 1%) compared to  $t_{WDU}$  in **Timing Diagram 4** and **5**.

- \*3. The time (\Delta twoll) VCWDT reaches VCWL from 0 V is proportional to the adjustment capacitance for watchdog time-out period (CWDT). Thus, large CWDT results in large \Delta twoll.

Figure 21 Double Pulse Detection due to VWDI Rising Edge Figure 22 Double Pulse Detection due to VWDI Falling Edge

- \*1. The delay time (∆t) from the V<sub>WDI</sub> rising edge to the V<sub>CWDT</sub> rising start is sufficiently small (less than 1%) compared to the watchdog double pulse detection time (t<sub>WDL</sub>).

- \*2. The time (Δtwdl) Vcwdt reaches Vcwl from 0 V is proportional to Cwdt. Thus, large Cwdt results in large Δtwdl. In window mode, a double pulse is detected during both periods of Δtwdl and twdl.

- \*3. The delay time (∆t) from the V<sub>WDI</sub> rising edge to the V<sub>CPOR</sub> rising start is sufficiently small (less than 1%) compared to t<sub>RST</sub> in **Timing Diagram 2** and **5**.

- \*4. The time (Δtrst) V<sub>CPOR</sub> reaches V<sub>CPL</sub> from 0 V is proportional to C<sub>POR</sub>. Thus, large C<sub>POR</sub> results in large Δtrst. Refer to "12. Initialization time (t<sub>INIT</sub>) vs. Power supply voltage rise time (t<sub>r</sub>)" in "■ Characteristics (Typical Data)".

- \*5. Only the S-1411 Series

- \*6. The delay time (∆t) from the V<sub>WDI</sub> falling edge to the V<sub>CWDT</sub> rising start is sufficiently small (less than 1%) compared to t<sub>WDL</sub>.

- **\*7.** The delay time (∆t) from the V<sub>WDI</sub> falling edge to the V<sub>CPOR</sub> rising start is sufficiently small (less than 1%) compared to t<sub>RST</sub> in **Timing Diagram 2** and **5**.

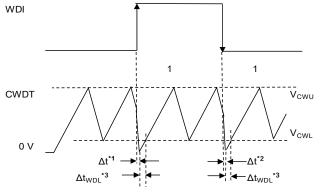

Figure 23 Double Pulse Detection due to V<sub>WDI</sub> Both Rising and Falling Edges

Figure 24 Double Pulse Non-detection due to V<sub>WDI</sub> Both Rising and Falling Edges

- \*1. The delay time (∆t) from the V<sub>WDI</sub> rising edge to the V<sub>CWDT</sub> rising start is sufficiently small (less than 1%) compared to t<sub>WDL</sub>.

- \*2. The time (Δtwpl) Vcwpt reaches Vcwl from 0 V is proportional to Cwpt. Thus, large Cwpt results in large Δtwpl. In window mode, a double pulse is detected during both periods of Δtwpl and twpl.

- \*3. The delay time ( $\Delta t$ ) from the V<sub>WDI</sub> falling edge to the V<sub>CPOR</sub> rising start is sufficiently small (less than 1%) compared to t<sub>RST</sub> in **Timing Diagram 2** and **5**.

- \*4. The time (∆trst) V<sub>CPOR</sub> reaches V<sub>CPL</sub> from 0 V is proportional to C<sub>POR</sub>. Thus, large C<sub>POR</sub> results in large ∆trst. Refer to "12. Initialization time (t<sub>INIT</sub>) vs. Power supply voltage rise time (t<sub>r</sub>)" in "■ Characteristics (Typical Data)".

- \*5. Only the S-1411 Series

- \*6. The delay time (∆t) from the V<sub>WDI</sub> falling edge to the V<sub>CWDT</sub> rising start is sufficiently small (less than 1%) compared to t<sub>WDU</sub> in **Timing Diagram 4** and **5**.

- \*7. The delay time ( $\Delta t$ ) from the V<sub>WDI</sub> rising edge to the V<sub>CWDT</sub> rising start is sufficiently small (less than 1%) compared to  $t_{WDU}$  in **Timing Diagram 4** and **5**.

- \*8. As indicated by the waveform illustrated with dashed lines, if V<sub>CWDT</sub> does not fall to 0 V when the V<sub>WDI</sub> rising or falling edge is input, ∆t<sub>WDL</sub> may approach 0. Similar phenomena may occur in **Timing Diagrams 6-1** to **6-4** and **Timing Diagram 7-1** to **7-3** as well.

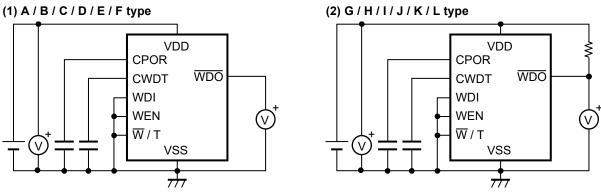

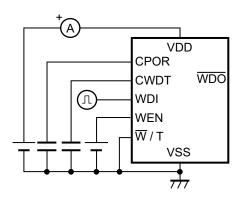

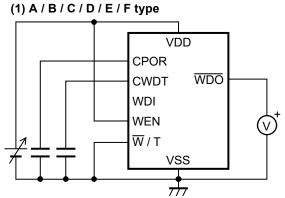

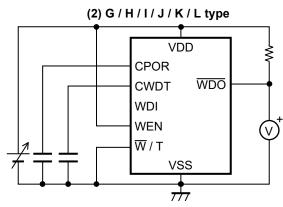

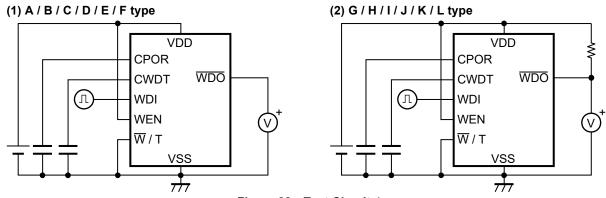

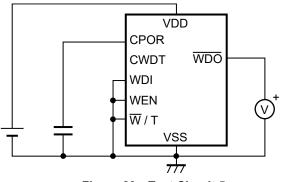

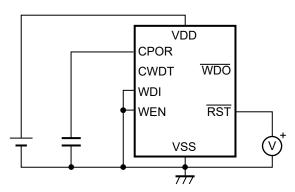

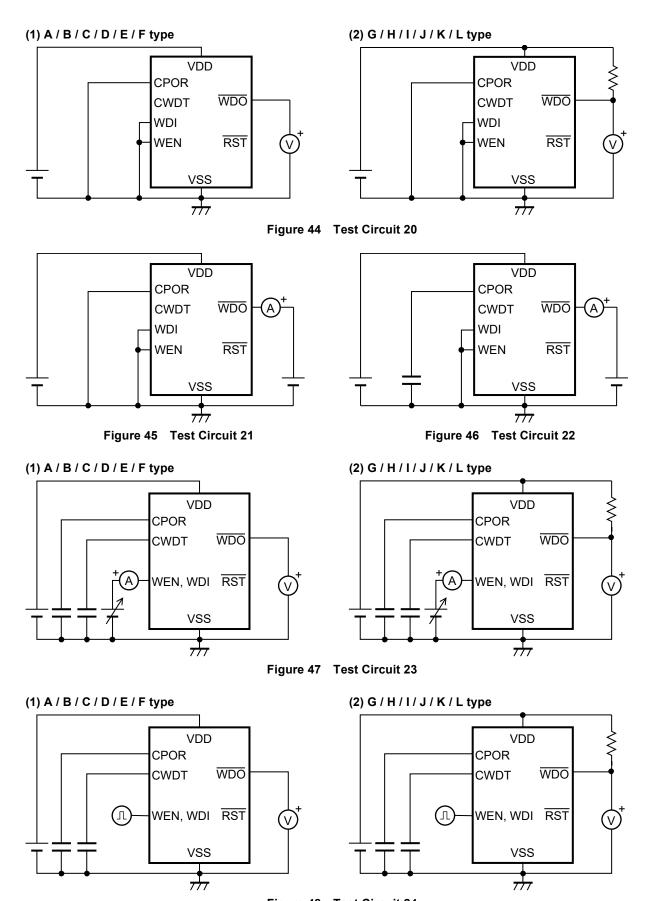

### **■** Test Circuits

Refer to "**Recommended Operation Conditions**" when setting constants of external pull-up resistors (R<sub>extR</sub>, R<sub>extW</sub>) and external capacitors (C<sub>POR</sub>, C<sub>WDT</sub>).

### 1. S-1410 Series

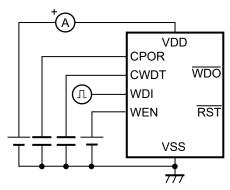

Figure 25 Test Circuit 1

Figure 26 Test Circuit 2

Figure 27 Test Circuit 3

Figure 28 Test Circuit 4

ABLIC Inc.

23

Figure 29 Test Circuit 5

Figure 30 Test Circuit 6

Figure 31 Test Circuit 7

Figure 32 Test Circuit 8

(2) G / H / I / J / K / L type

VDD

CPOR

CWDT

WEN, WDI, W/T

VSS

Figure 33 Test Circuit 9

24 ABLIC Inc.

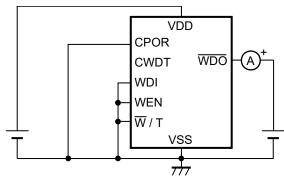

### 2. S-1411 Series

Figure 35 Test Circuit 11

Figure 36 Test Circuit 12

Figure 37 Test Circuit 13

Figure 38 Test Circuit 14

Figure 39 Test Circuit 15

Figure 40 Test Circuit 16

Figure 41 Test Circuit 17

Figure 42 Test Circuit 18

Figure 43 Test Circuit 19

Figure 48 Test Circuit 24

28

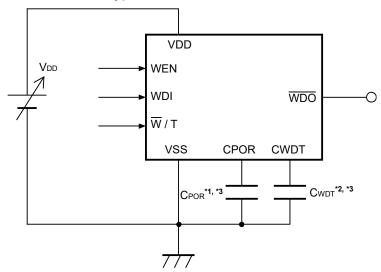

### ■ Standard Circuits

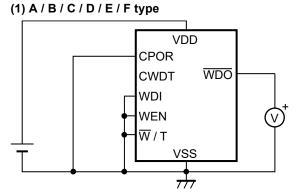

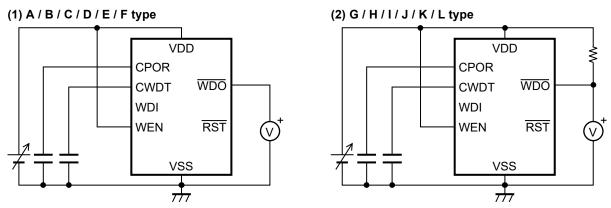

### 1. S-1410 Series A / B / C / D / E / F type

- \*1. Connect the adjustment capacitor for reset time-out period (CPOR) directly between the CPOR pin and the VSS pin.

- \*2. Connect the adjustment capacitor for watchdog time-out period (CwDT) directly between the CWDT pin and the VSS pin.

- \*3. A capacitor of 100 pF to 1 μF can be used for C<sub>POR</sub> and C<sub>WDT</sub>. Even if the capacitance is within this range, cautions are still needed when the value is extremely large. Refer to "1. Low voltage operation when C<sub>POR</sub> is extremely large" and "2. Relation between C<sub>POR</sub> and C<sub>WDT</sub>" in "■ Precautions for Use".

### Figure 49

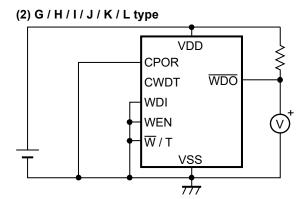

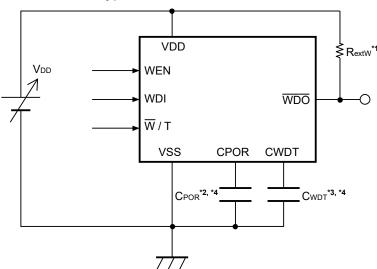

### 2. S-1410 Series G / H / I / J / K / L type

- \*1.  $R_{extW}$  is an external pull-up resistor for the  $\overline{WDO}$  pin.

- \*2. Connect the adjustment capacitor for reset time-out period (CPOR) directly between the CPOR pin and the VSS pin.

- \*3. Connect the adjustment capacitor for watchdog time-out period (CwDT) directly between the CWDT pin and the VSS pin.

- \*4. A capacitor of 100 pF to 1 μF can be used for C<sub>POR</sub> and C<sub>WDT</sub>. Even if the capacitance is within this range, cautions are still needed when the value is extremely large. Refer to "1. Low voltage operation when C<sub>POR</sub> is extremely large" and "2. Relation between C<sub>POR</sub> and C<sub>WDT</sub>" in "■ Precautions for Use".

Figure 50

Caution The above connection diagrams and constants will not guarantee successful operation. Perform thorough evaluation using the actual application to set the constants.

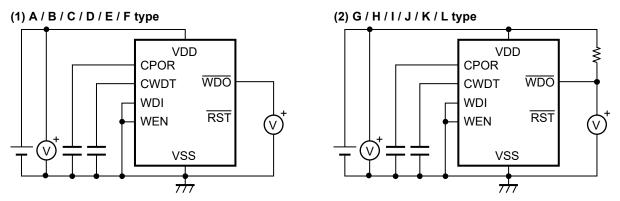

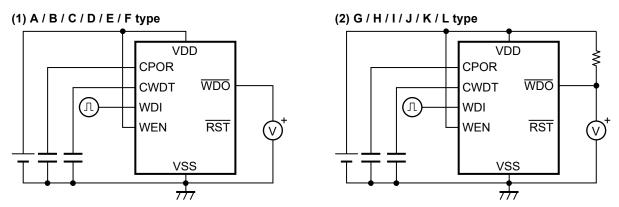

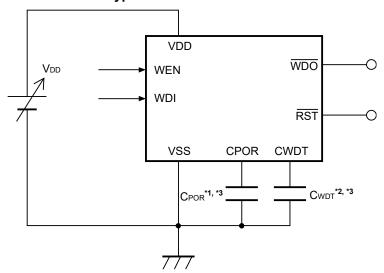

### 3. S-1411 Series A / B / C / D / E / F type

- \*1. Connect the adjustment capacitor for reset time-out period (C<sub>POR</sub>) directly between the CPOR pin and the VSS pin.

- \*2. Connect the adjustment capacitor for watchdog time-out period (CwDT) directly between the CWDT pin and the VSS pin.

- \*3. A capacitor of 100 pF to 1 μF can be used for C<sub>POR</sub> and C<sub>WDT</sub>. Even if the capacitance is within this range, cautions are still needed when the value is extremely large. Refer to "1. Low voltage operation when C<sub>POR</sub> is extremely large" and "2. Relation between C<sub>POR</sub> and C<sub>WDT</sub>" in "■ Precautions for Use".

### Figure 51

### 4. S-1411 Series G / H / I / J / K / L type

- \*1.  $R_{extW}$  is an external pull-up resistor for the  $\overline{WDO}$  pin.

- \*2.  $R_{extR}$  is an external pull-up resistor for the  $\overline{RST}$  pin.

- \*3. Connect the adjustment capacitor for reset time-out period (CPOR) directly between the CPOR pin and the VSS pin.

- \*4. Connect the adjustment capacitor for watchdog time-out period (CwDT) directly between the CWDT pin and the VSS pin.

- \*5. A capacitor of 100 pF to 1 μF can be used for C<sub>POR</sub> and C<sub>WDT</sub>. Even if the capacitance is within this range, cautions are still needed when the value is extremely large. Refer to "1. Low voltage operation when C<sub>POR</sub> is extremely large" and "2. Relation between C<sub>POR</sub> and C<sub>WDT</sub>" in "■ Precautions for Use".

### Figure 52

Caution The above connection diagrams and constants will not guarantee successful operation. Perform thorough evaluation using the actual application to set the constants.

### ■ Operations

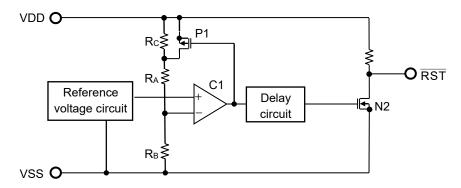

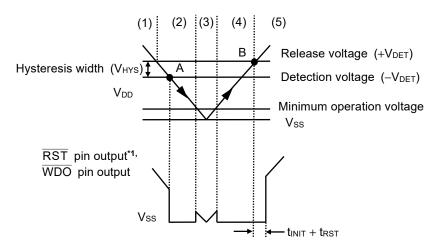

### 1. Voltage detector circuit

### 1. 1 Basic operation

- (1) When the power supply voltage ( $V_{DD}$ ) is release voltage ( $+V_{DET}$ ) of the detector or higher, the Nch transistor (N2) is turned off and "H" is output to the  $\overline{RST}$  pin. Since the Pch transistor (P1) is turned on, the input voltage to the comparator (C1) is  $\frac{R_B \bullet V_{DD}}{R_A + R_B}$ .

- (2) Even if  $V_{DD}$  decreases to  $+V_{DET}$  or lower, "H" is output to the  $\overline{RST}$  pin when  $V_{DD}$  is the detection voltage ( $-V_{DET}$ ) or higher. When  $V_{DD}$  decreases to  $-V_{DET}$  (point A in **Figure 54**) or lower, N2 which is controlled by C1 is turned on, and then "L" is output to the  $\overline{RST}$  pin. At this time, P1 is turned off, and the input voltage to C1 is  $\overline{R_B \bullet V_{DD}}$   $\overline{R_A + R_B + R_C}$ .

- (3) If  $V_{DD}$  further decreases to the IC's minimum operation voltage or lower, the  $\overline{RST}$  pin output is "H".

- (4) When  $V_{DD}$  increases to the IC's minimum operation voltage or higher, "L" is output to the  $\overline{RST}$  pin. In addition, even if  $V_{DD}$  exceeds  $-V_{DET}$ , the output is "L" when  $V_{DD}$  is lower than  $+V_{DET}$ .

- (5) When  $V_{DD}$  increases to  $+V_{DET}$  (point B in **Figure 54**) or higher, N2 is turned off, and "H" is output to the  $\overline{RST}$  pin after elapse of  $t_{INIT} + t_{RST}$ .

Figure 53 Operation of Voltage Detector Circuit

\*1. Only the S-1411 Series

Figure 54 Timing Chart of Voltage Detector Circuit

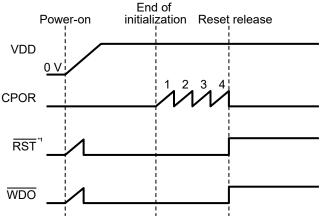

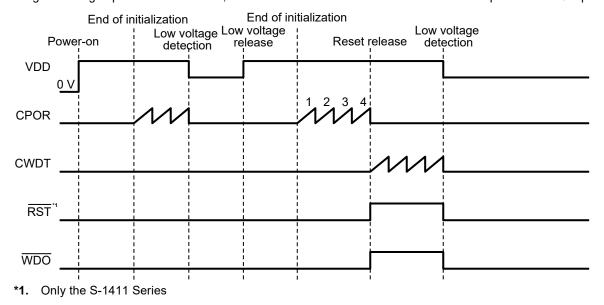

### 1. 2 From power-on to reset release

The S-1410/1411 Series initiates the initialization if the VDD pin voltage exceeds the release voltage ( $+V_{DET}$ ). The charge-discharge operation to the CPOR pin is initiated after the passage of the initialization time ( $t_{INIT}$ ), and the  $\overline{WDO}$  pin output and the  $\overline{RST}$  pin output change from "L" to "H" after the operation is performed 4 times. Refer to **Figure 55**.

t<sub>INIT</sub> changes according to the power supply voltage rise time (t<sub>r</sub>). Refer to "12. Initialization time (t<sub>INIT</sub>) vs. Power supply voltage rise time (t<sub>r</sub>)" in "■ Characteristics (Typical Data)" for the relation between t<sub>INIT</sub> and t<sub>r</sub>.

\*1. Only the S-1411 Series

Figure 55

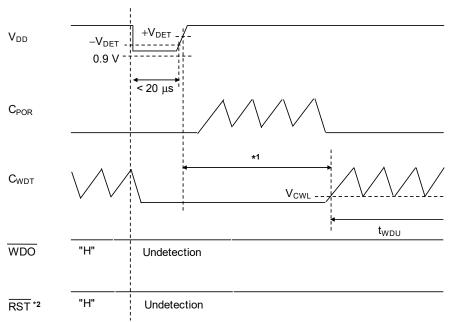

### 1. 3 Operation of low voltage detection

The voltage detection circuit detects a low voltage if the power supply voltage falls below the detection voltage, and then "L" is output from the  $\overline{\text{WDO}}$  pin and the  $\overline{\text{RST}}$  pin (only the S-1411 Series). The output is maintained until the charge-discharge operation of the CPOR pin is performed 4 times.

The S-1410/1411 Series can detect a low voltage even if either the CPOR pin or the CWDT pin performs the charge-discharge operation. In this case, no influence is exerted on the status of the WEN pin or the  $\overline{W}$  / T pin.

Figure 56

32 ABLIC Inc.

### 2. Watchdog timer

### 2. 1 Watchdog mode (only S-1410 Series)

### 2. 1. 1 Time-out mode ( $\overline{W}$ / T pin = "H")

The S-1410 Series detects an abnormality when not inputting an edge to the WDI pin during the watchdog time-out period ( $t_{WDU}$ ). And then "L" is output from the  $\overline{WDO}$  pin.

#### \*1. Only the S-1410 Series

Figure 57 Abnormality Detection during Time-out Mode

### 2. 1. 2 Window mode (W / T pin = "L")

When not inputting an edge to the WDI pin during  $t_{WDU}$ , or when an edge is input to the WDI pin again within a specific period of time (the discharge time due to an edge detection + 1 charge-discharge time ( $t_{WDL}$ )) after inputting an edge to the WDI pin, the  $\overline{WDO}$  pin output changes from "H" to "L".

\*1. Only the S-1410 Series

Figure 58 Abnormality Detection during Window Mode

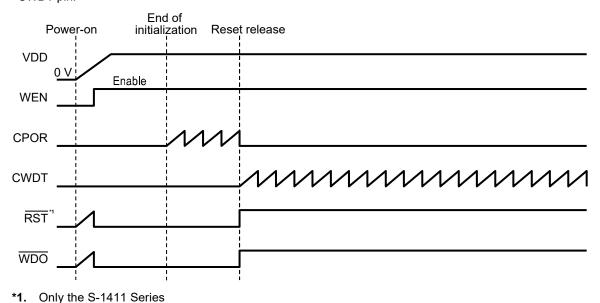

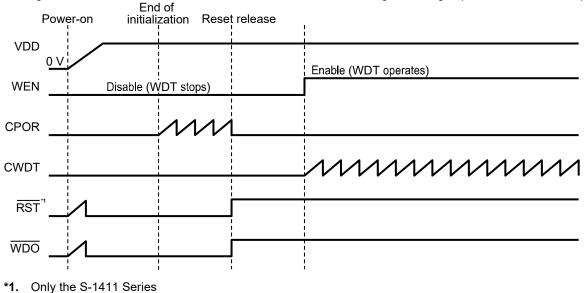

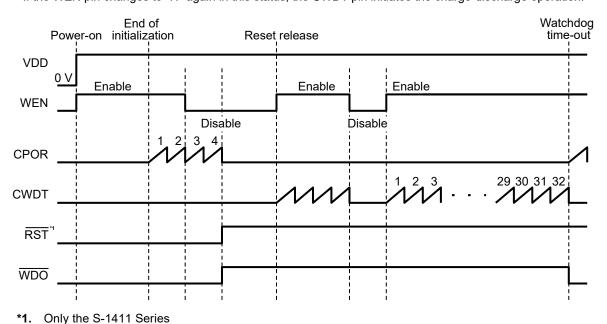

### 2. 2 From reset release to initiation of charge-discharge operation to CWDT pin

The charge-discharge operation to the CWDT pin differs depending on the status of the WEN pin at the reset release.

### 2. 2. 1 When WEN pin is in Enable at reset release

Since the watchdog timer is in Enable, the S-1410/1411 Series initiates the charge-discharge operation to the CWDT pin.

Figure 59 WEN Pin = "H"

### 2. 2. 2 When WEN pin is in Disable at reset release

Since the watchdog timer is in Disable after the CPOR pin performs the charge-discharge operation 4 times, the S-1410/1411 Series does not initiate the charge-discharge operation to the CWDT pin. If the input to the WEN pin changes to "H" in this status, the S-1410/1411 Series initiates the charge-discharge operation to the CWDT pin.

Figure 60 WEN Pin = "L" → "H"

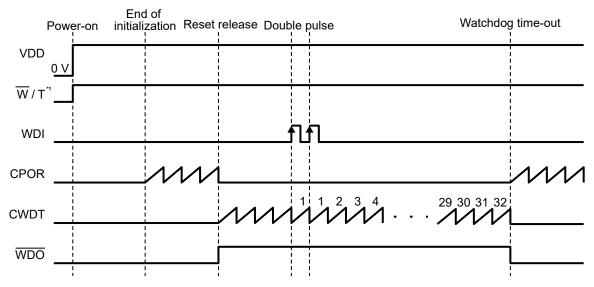

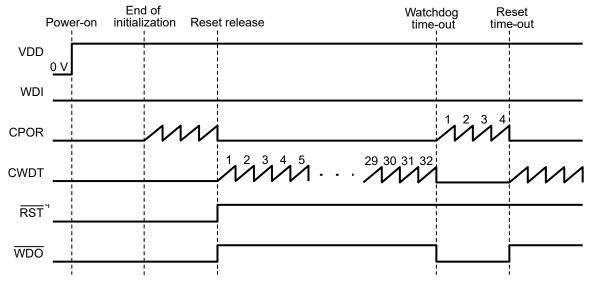

### 2. 3 Watchdog time-out detection

The watchdog timer detects a time-out after the charge-discharge operation to the CWDT pin is performed 32 times, then the  $\overline{\text{WDO}}$  pin output changes from "H" to "L".

\*1. Only the S-1411 Series

Figure 61

### 2. 4 Internal counter reset due to edge

When the WDI pin detects an edge during the charge-discharge operation to the CWDT pin, the internal counter which counts the number of times of the charge-discharge operation is reset. The CWDT pin initiates the discharge operation when an edge is detected and initiates the charge-discharge operation again after the discharge operation is completed.

### 2. 4. 1 Counter reset due to rising edge (S-141xAxx, S-141xDxx, S-141xGxx, S-141xJxx)

Figure 62

## 2. 4. 2 Counter reset due to falling edge (S-141xBxx, S-141xExx, S-141xHxx, S-141xKxx)

\*1. Only the S-1411 Series

Figure 63

# 2. 4. 3 Counter reset due to both rising and falling edges 1 (S-141xCxx, S-141xFxx, S-141xlxx, S-141xLxx)

\*1. Only the S-1411 Series

Figure 64

# 2. 4. 4 Counter reset due to both rising and falling edges 2 (S-141xCxx, S-141xFxx, S-141xLxx)

\*1. Only the S-1411 Series

Figure 65

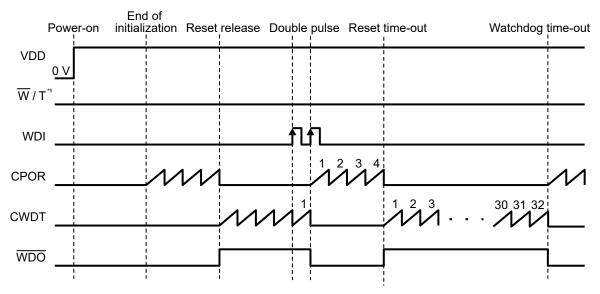

#### 2. 5 Watchdog double pulse detection (only during window mode)

If an edge is input to the WDI pin again within a specific period of time (the discharge time due to an edge detection + 1 charge-discharge time ( $t_{WDL}$ )) after inputting an edge to the WDI pin when the S-1410/1411 Series is in the window mode, the  $\overline{WDO}$  pin output changes from "H" to "L".

When the watchdog timer goes to Disable due to a change of the WEN pin ("H"  $\rightarrow$  "L"  $\rightarrow$  "H") after inputting an edge to the WDI pin, the  $\overline{\text{WDO}}$  pin continues outputting "H" even if an edge is input to the WDI pin within the specific period of time mentioned above.

## 2. 5. 1 Double pulse detection due to rising edge (S-141xAxx, S-141xDxx, S-141xGxx, S-141xJxx)

\*1. Only the S-1411 Series

Figure 66

## 2. 5. 2 Double pulse detection due to falling edge (S-141xBxx, S-141xExx, S-141xHxx, S-141xKxx)

\*1. Only the S-1411 Series

Figure 67

# 2. 5. 3 Double pulse detection due to both rising and falling edges (S-141xCxx, S-141xFxx, S-141xlxx, S-141xLxx)

The double pulse is detected only when edges are input in order of rising and falling.

#### (1) When edges are input to WDI pin in order of rising and falling

\*1. Only the S-1411 Series

Figure 68 Double Pulse Detection

#### (2) When edges are input to WDI pin in order of falling and rising

In this case, no double pulse is detected, but the counter is reset.

#### \*1. Only the S-1411 Series

Figure 69 Double Pulse Non-detection

#### 2. 6 Counter reset due to WEN pin during charge-discharge operation to CWDT pin

When the WEN pin changes from "H" to "L" during the charge-discharge operation to the CWDT pin, the CWDT pin performs the discharge operation. In addition, the internal counter which counts the number of times of the charge-discharge operation for the CWDT pin is also reset.

If the WEN pin changes to "H" again in this status, the CWDT pin initiates the charge-discharge operation.

Figure 70

#### ■ Precautions for Use

A capacitor of 100 pF to 1  $\mu$ F can be used for the adjustment capacitor for reset time-out period ( $C_{POR}$ ) and the adjustment capacitor for watchdog time-out period ( $C_{WDT}$ ). Even if the capacitance is within this range, cautions are still needed when the value is extremely large.

#### 1. Low voltage operation when CPOR is extremely large

When the S-1410/1411 Series detects a low voltage during the  $C_{POR}$  charge-discharge operation, it will take time for the  $C_{POR}$  discharge operation to be performed if  $C_{POR}$  is extremely large. Therefore, the discharge operation may not be completed by the time the power supply voltage ( $V_{DD}$ ) exceeds the release voltage ( $+V_{DET}$ ). In this case, since the charge-discharge operation is performed after the discharge operation is completed, a delay time of the same length as the  $C_{POR}$  discharge operation time occurs by the time the reset time-out period ( $t_{RST}$ ) count starts.

- \*1. When the capacitance is sufficiently small.

- \*2. When the capacitance is extremely large.

- \*3. Delay time of the same length as the CPOR discharge operation time

Figure 71

#### 2. Relation between CPOR and CWDT

Select a capacitor which satisfies the following expression for  $C_{POR}$  and  $C_{WDT}$ . When this condition is not satisfied, the S-1410/1411 Series may not complete the  $C_{WDT}$  discharge operation after a double pulse detection. Unless the  $C_{WDT}$  discharge operation has been completed, the S-1410/1411 Series will not be able to initiate the next charge-discharge operation even if  $t_{RST}$  has elapsed. For this reason, a delay time of the same length as the  $C_{WDT}$  discharge operation time occurs by the time the watchdog time-out period ( $t_{WDU}$ ) count starts.

$C_{WDT} / C_{POR} \le 600$

- \*1. When  $C_{WDT} / C_{POR} \le 600$ .

- **\*2.** When  $C_{WDT} / C_{POR} > 600$ .

- ${}^{\star}$ 3. Delay time of the same length as the  $C_{\text{WDT}}$  discharge operation time

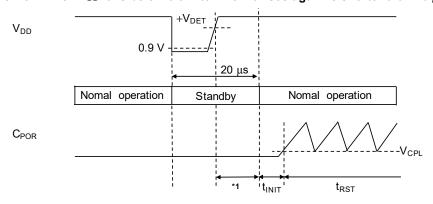

#### 3. Re-applying power supply

If the power supply voltage ( $V_{DD}$ ) falls to 0.9 V or lower, a standby status for 20  $\mu$ s is required by the time low voltage detection is released in order for the discharge operation of internal circuit to be performed fully. If an appropriate amount of time is not secured for the standby status to be completed by the time the power supply is re-applied, the initialization start will be delayed. For this reason, a delay time of the same length as the time until the standby status has been completed occurs by the time the  $t_{RST}$  count starts after the power supply rises.

#### 3. 1 If the time from when $V_{DD}$ falls below 0.9 V to when it rises again is longer than 20 $\mu s$

Figure 73

#### 3. 2 If the time from when $V_{DD}$ falls below 0.9 V to when it rises again is shorter than 20 $\mu s$

\*1. Delay time of the same length as the time until standby status at power-on has been completed

Figure 74

#### 4. Low voltage detection at instantaneous voltage drop

In the S-1410/1411 Series, when the period of  $0.9 \text{ V} \le \text{V}_{DD} \le -\text{V}_{DET}$  is shorter than  $20 \mu \text{s}$ , the WDO pin and the  $\overline{\text{RST}}$  pin may not output a low voltage detection signal. Even in this case, the S-1410/1411 Series carries out the charge-discharge operation for  $C_{POR}$  in the same manner at power-on. For this reason, a delay time of the same length as the  $C_{POR}$  charge-discharge operation time occurs by the time the  $t_{WDU}$  count starts after the power supply rises.

- \*1. Delay time of the same length as the  $C_{POR}$  discharge operation time ( $t_{INIT} + t_{RST}$ )

- \*2. Only the S-1411 Series

Figure 75

#### ■ Precautions

- Since input pins (the WEN pin, the WDI pin and the  $\overline{W}$  / T pin) in the S-1410/1411 Series are CMOS configurations, make sure that an intermediate potential is not input when the S-1410/1411 Series operates.

- Since the WDO pin and the RST pin are affected by external resistance and external capacitance, use the S-1410/1411 Series after performing thorough evaluation with the actual application.

- Do not apply an electrostatic discharge to this IC that exceeds the performance ratings of the built-in electrostatic protection circuit.

- ABLIC Inc. claims no responsibility for any disputes arising out of or in connection with any infringement by products including this IC of patents owned by a third party.

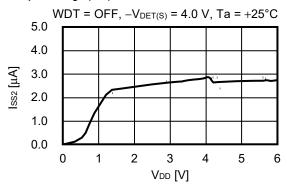

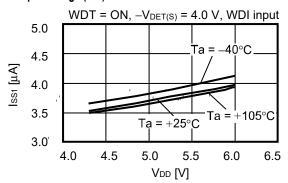

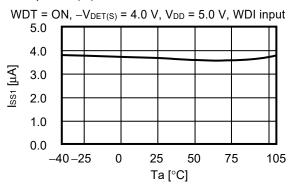

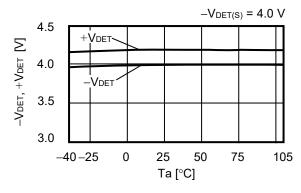

#### ■ Characteristics (Typical Data)

Input voltage (V<sub>DD</sub>)

1. Current consumption during watchdog timer stop (Iss2) vs. 2. Current consumption during watchdog timer operation (Iss1) vs. Input voltage (VDD)

3. Current consumption during watchdog timer operation (I<sub>SS1</sub>) vs. 4. Detection voltage (-V<sub>DET</sub>), Release voltage (+V<sub>DET</sub>) vs. Temperature (Ta) Temperature (Ta)

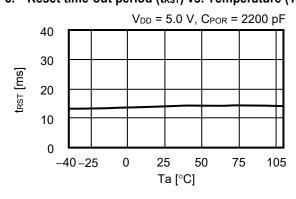

5. Reset time-out period (trst) vs. Temperature (Ta)

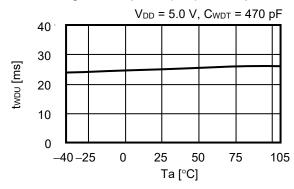

6. Watchdog time-out period (twpu) vs. Temperature (Ta)

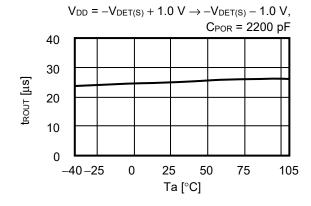

7. Reset output delay time (trout) vs. Temperature (Ta)

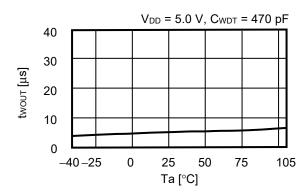

8. Watchdog output delay time (twout) vs. Temperature (Ta)

#### 9. Reset time-out period (trst) vs. CPOR

#### 10. Watchdog time-out period (twou) vs. Cwdt

#### 11. Nch driver output current (I<sub>WOUT</sub>) vs. Input voltage (V<sub>DD</sub>)

#### 12. Initialization time $(t_{INIT})$ vs. Power supply voltage rise time $(t_r)$

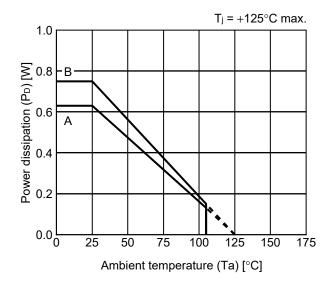

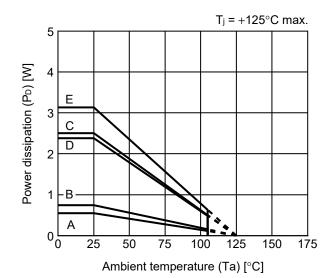

#### **■** Power Dissipation

#### TMSOP-8

| Board | Power Dissipation (P <sub>D</sub> ) |

|-------|-------------------------------------|

| Α     | 0.63 W                              |

| В     | 0.75 W                              |

| С     | _                                   |

| D     | _                                   |

| E     | -                                   |

#### **HSNT-8(2030)**

| Board | Power Dissipation (P <sub>D</sub> ) |

|-------|-------------------------------------|

| А     | 0.55 W                              |

| В     | 0.74 W                              |

| С     | 2.50 W                              |

| D     | 2.38 W                              |

| Е     | 3.13 W                              |

# **TMSOP-8 Test Board**

## (1) Board A

| Item                        |   | Specification                               |

|-----------------------------|---|---------------------------------------------|

| Size [mm]                   |   | 114.3 x 76.2 x t1.6                         |

| Material                    |   | FR-4                                        |

| Number of copper foil layer |   | 2                                           |

|                             | 1 | Land pattern and wiring for testing: t0.070 |

| Coppor foil layer [mm]      | 2 | -                                           |

| Copper foil layer [mm] -    | 3 | -                                           |

|                             | 4 | 74.2 x 74.2 x t0.070                        |

| Thermal via                 |   | -                                           |

## (2) Board B

| Item                        |   | Specification                               |

|-----------------------------|---|---------------------------------------------|

| Size [mm]                   |   | 114.3 x 76.2 x t1.6                         |

| Material                    |   | FR-4                                        |

| Number of copper foil layer |   | 4                                           |

|                             | 1 | Land pattern and wiring for testing: t0.070 |

| Copper foil layer [mm]      | 2 | 74.2 x 74.2 x t0.035                        |

|                             | 3 | 74.2 x 74.2 x t0.035                        |

|                             | 4 | 74.2 x 74.2 x t0.070                        |

| Thermal via                 |   | -                                           |

No. TMSOP8-A-Board-SD-1.0

# HSNT-8(2030) Test Board

O IC Mount Area

## (1) Board A

| Item                        |   | Specification                               |

|-----------------------------|---|---------------------------------------------|

| Size [mm]                   |   | 114.3 x 76.2 x t1.6                         |

| Material                    |   | FR-4                                        |

| Number of copper foil layer |   | 2                                           |

|                             | 1 | Land pattern and wiring for testing: t0.070 |

| Copper foil layer [mm]      | 2 | -                                           |

|                             | 3 | -                                           |

|                             | 4 | 74.2 x 74.2 x t0.070                        |

| Thermal via                 |   | -                                           |

## (2) Board B

| Item                        |   | Specification                               |

|-----------------------------|---|---------------------------------------------|

| Size [mm]                   |   | 114.3 x 76.2 x t1.6                         |

| Material                    |   | FR-4                                        |

| Number of copper foil layer |   | 4                                           |

|                             | 1 | Land pattern and wiring for testing: t0.070 |

| Copper foil layer [mm]      | 2 | 74.2 x 74.2 x t0.035                        |

|                             | 3 | 74.2 x 74.2 x t0.035                        |

|                             | 4 | 74.2 x 74.2 x t0.070                        |

| Thermal via                 |   | -                                           |

## (3) Board C

| Item                        |   | Specification                               |

|-----------------------------|---|---------------------------------------------|

| Size [mm]                   |   | 114.3 x 76.2 x t1.6                         |

| Material                    |   | FR-4                                        |

| Number of copper foil layer |   | 4                                           |

|                             | 1 | Land pattern and wiring for testing: t0.070 |

| Copper foil layer [mm]      | 2 | 74.2 x 74.2 x t0.035                        |

|                             | 3 | 74.2 x 74.2 x t0.035                        |

|                             | 4 | 74.2 x 74.2 x t0.070                        |

| Thermal via                 |   | Number: 4<br>Diameter: 0.3 mm               |

enlarged view

No. HSNT8-A-Board-SD-2.0

# HSNT-8(2030) Test Board

O IC Mount Area

## (4) Board D

| Item                        |   | Specification                                          |

|-----------------------------|---|--------------------------------------------------------|

| Size [mm]                   |   | 114.3 x 76.2 x t1.6                                    |

| Material                    |   | FR-4                                                   |

| Number of copper foil layer |   | 4                                                      |

|                             | 1 | Pattern for heat radiation: 2000mm <sup>2</sup> t0.070 |

| Coppor foil layer [mm]      | 2 | 74.2 x 74.2 x t0.035                                   |

| Copper foil layer [mm]      | 3 | 74.2 x 74.2 x t0.035                                   |

|                             | 4 | 74.2 x 74.2 x t0.070                                   |

| Thermal via                 |   | -                                                      |

enlarged view

#### (5) Board E

| Item                        |   | Specification                                          |

|-----------------------------|---|--------------------------------------------------------|

| Size [mm]                   |   | 114.3 x 76.2 x t1.6                                    |

| Material                    |   | FR-4                                                   |

| Number of copper foil layer |   | 4                                                      |

| Copper foil layer [mm]      | 1 | Pattern for heat radiation: 2000mm <sup>2</sup> t0.070 |

|                             | 2 | 74.2 x 74.2 x t0.035                                   |

|                             | 3 | 74.2 x 74.2 x t0.035                                   |

|                             | 4 | 74.2 x 74.2 x t0.070                                   |

| Thermal via                 |   | Number: 4<br>Diameter: 0.3 mm                          |

enlarged view

No. HSNT8-A-Board-SD-2.0

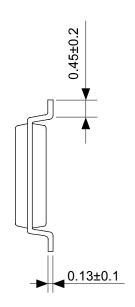

## No. FM008-A-P-SD-1.2

| TITLE | TMSOP8-A-PKG Dimensions |  |  |

|-------|-------------------------|--|--|

| No.   | FM008-A-P-SD-1.2        |  |  |

| ANGLE | <b>Q</b>                |  |  |

| UNIT  | mm                      |  |  |

|       |                         |  |  |

|       |                         |  |  |

|       |                         |  |  |

|       | ABLIC Inc.              |  |  |

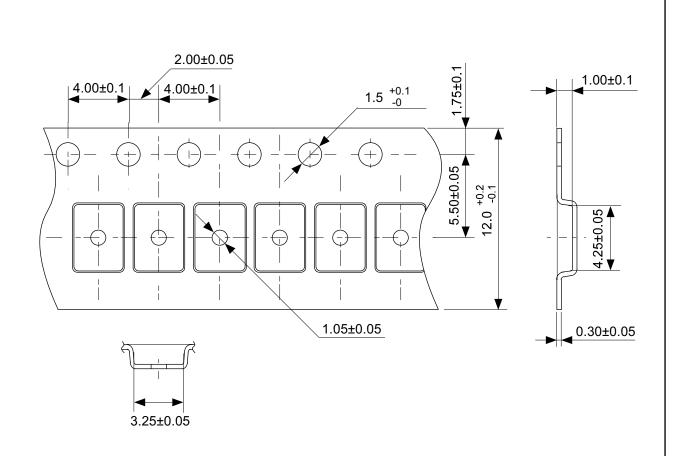

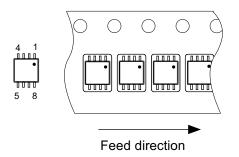

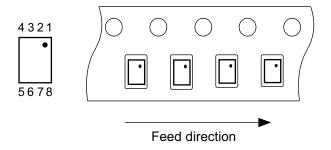

## No. FM008-A-C-SD-2.0

| TITLE      | TMSOP8-A-Carrier Tape |  |

|------------|-----------------------|--|

| No.        | FM008-A-C-SD-2.0      |  |

| ANGLE      |                       |  |

| UNIT       | mm                    |  |

|            |                       |  |

|            |                       |  |

|            |                       |  |

| ABLIC Inc. |                       |  |

The heat sink of back side has different electric potential depending on the product.Confirm specifications of each product.Do not use it as the function of electrode.

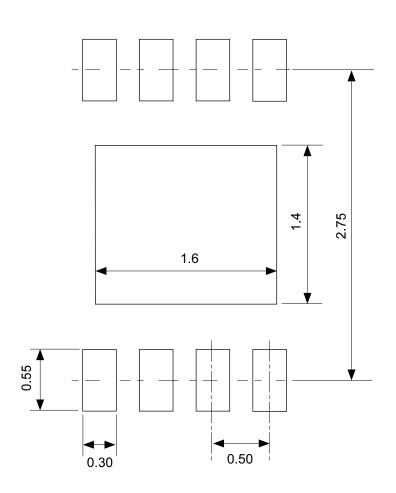

No. PP008-A-P-SD-2.0

|            | -                       |  |

|------------|-------------------------|--|

| TITLE      | HSNT-8-A-PKG Dimensions |  |

| No.        | PP008-A-P-SD-2.0        |  |

| ANGLE      | <b>♦</b> □              |  |

| UNIT       | mm                      |  |

|            |                         |  |

|            |                         |  |

|            |                         |  |

| ABLIC Inc. |                         |  |

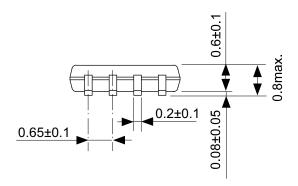

## No. PP008-A-C-SD-1.0

| TITLE      | HSNT-8-A-Carrier Tape |  |

|------------|-----------------------|--|

| No.        | PP008-A-C-SD-1.0      |  |

| ANGLE      |                       |  |

| UNIT       | mm                    |  |

|            |                       |  |

|            |                       |  |

|            |                       |  |

| ABLIC Inc. |                       |  |

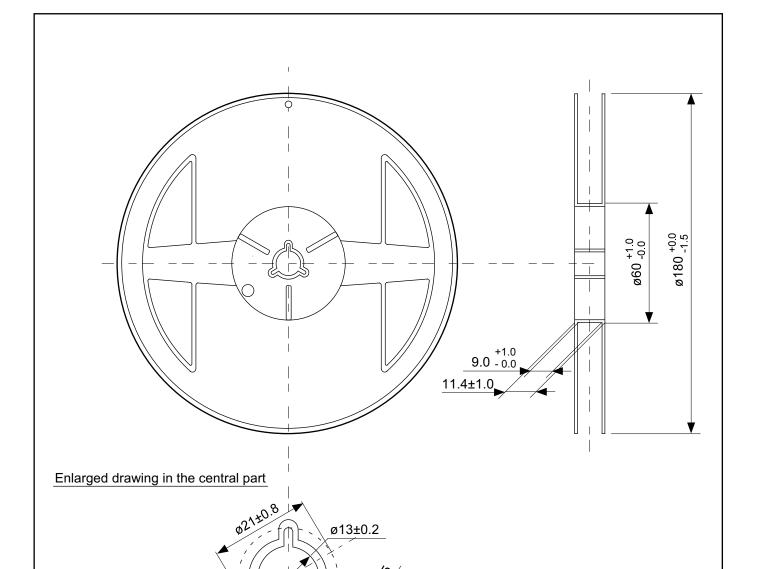

## No. PP008-A-R-SD-1.0

| TITLE      | HSNT-8-A-Reel    |      |       |  |

|------------|------------------|------|-------|--|

| No.        | PP008-A-R-SD-1.0 |      |       |  |

| ANGLE      |                  | QTY. | 5,000 |  |