# S-82B4A/5A Series

www.ablic.com

# BATTERY PROTECTION IC FOR 4-SERIAL OR 5-SERIAL CELL PACK

© ABLIC Inc., 2022 Rev.1.0\_00

This IC is a protection IC for lithium-ion rechargeable batteries, which includes high-accuracy voltage detection circuits and delay circuits. It is suitable for protecting 4-serial or 5-serial cell lithium-ion rechargeable battery packs from overcharge, overdischarge, and overcurrent.

## ■ Features

| • | High-accuracy    | voltage detect | ion for each cell |

|---|------------------|----------------|-------------------|

| • | i iluii-accuiacv | Voltage getect | ion faciliteir    |

Overcharge detection voltage n 3.900 V to 4.500 V (25 mV step) Accuracy  $\pm 20 \text{ mV}$  Overcharge release voltage n 3.500 V to  $4.500 \text{ V}^{*1}$  Accuracy  $\pm 50 \text{ mV}$  Overdischarge detection voltage n 2.000 V to 3.200 V (100 mV step) Accuracy  $\pm 50 \text{ mV}$  Overdischarge release voltage n 2.000 V to  $3.400 \text{ V}^{*2}$  Accuracy  $\pm 100 \text{ mV}$

Three-level discharge overcurrent detection

Discharge overcurrent 1 detection voltage

10 mV to 200 mV (5 mV step)

Discharge overcurrent 2 detection voltage

20 mV to 300 mV (5 mV step)

Accuracy ±5 mV

20 mV to 300 mV (5 mV step)

Accuracy ±10 mV

50 mV to 400 mV (10 mV step)

Accuracy ±20 mV

Charge overcurrent detection

• Discharge overcurrent 1 detection delay time is settable by an external capacitor (The other delay time are internally fixed)

Power saving control by a control pin

0 V battery charge: Enabled, inhibited

Power-down function: Available, unavailable

Release condition of discharge overcurrent status:

Load disconnection, charger connection

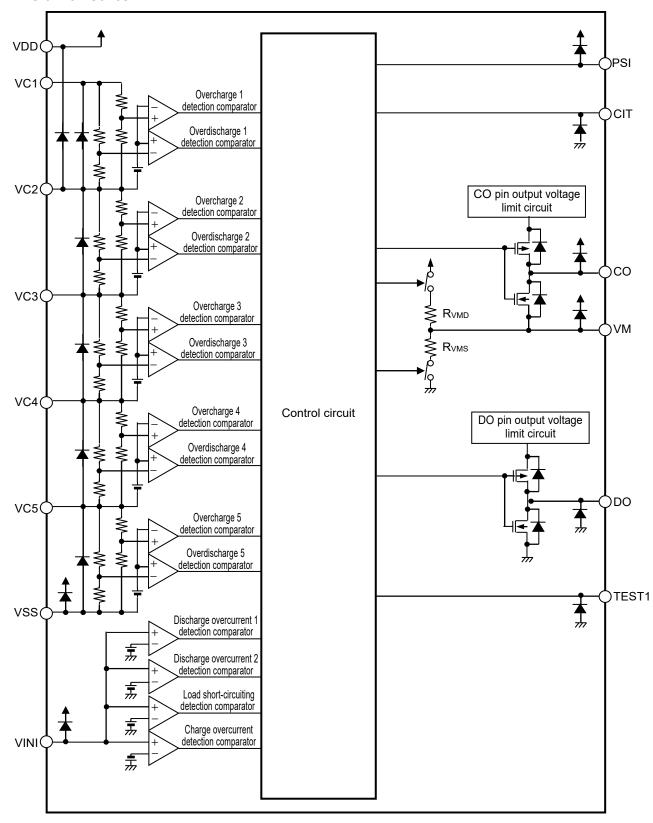

• Output voltage of CO and DO pin is limited to VC2 pin voltage. (S-82B5A Series)

High-withstand voltage:

Absolute maximum rating 28.0 V

Wide operating voltage range: 5.0 V to 24.0 V

Wide operation temperature range: Ta = -40°C to +85°C

• Low current consumption

During operation: 4.0  $\mu$ A typ., 8.0  $\mu$ A max. (Ta = +25°C) During power-down: 0.1  $\mu$ A max. (Ta = +25°C) During power-saving: 0.1  $\mu$ A max. (Ta = +25°C)

• Lead-free (Sn 100%), halogen-free

- \*1. Overcharge release voltage = Overcharge detection voltage Overcharge hysteresis voltage (Overcharge hysteresis voltage n can be selected from a range of 0 V to 0.4 V in 50 mV steps.)

- \*2. Overdischarge release voltage = Overdischarge detection voltage + Overdischarge hysteresis voltage (Overdischarge hysteresis voltage n can be selected from a range of 0 V to 0.7 V in 100 mV steps.)

**Remark** n = 1, 2, 3, 4, 5

## ■ Applications

Lithium-ion rechargeable battery packs

## ■ Package

16-Pin TSSOP

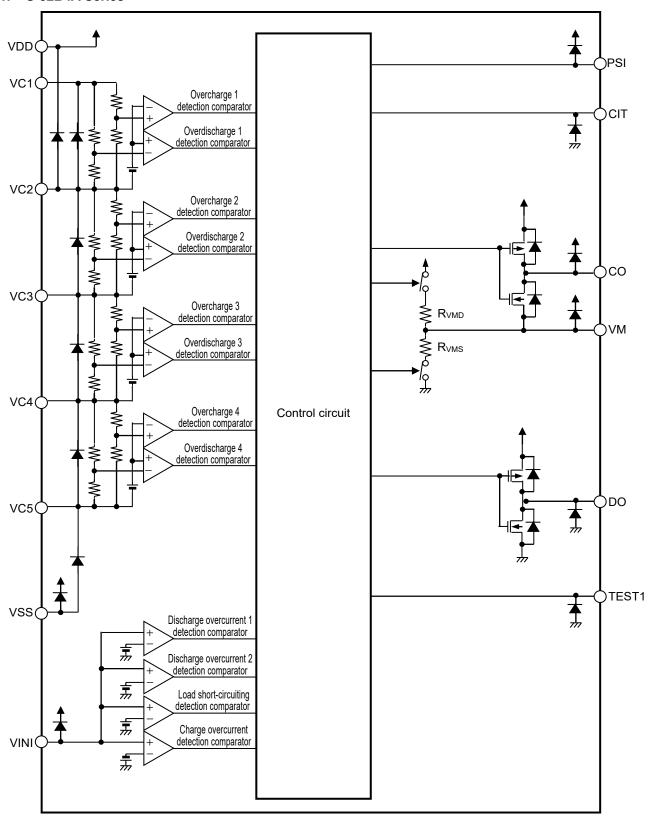

## ■ Block Diagram

#### 1. S-82B4A Series

**Remark** Diodes in the figure are parasitic diodes.

#### 2. S-82B5A Series

Remark Diodes in the figure are parasitic diodes.

Figure 2

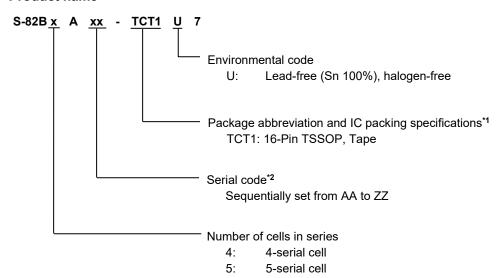

## **■ Product Name Structure**

#### 1. Product name

- \*1. Refer to the tape drawing.

- \*2. Refer to "3. Product name list".

## 2. Package

Table 1 Package Drawing Codes

| Package Name Dimension |              | Tape         | Reel         |

|------------------------|--------------|--------------|--------------|

| 16-Pin TSSOP           | FT016-A-P-SD | FT016-A-C-SD | FT016-A-R-S1 |

#### 3. Product name list

## 3. 1 S-82B5A Series

#### Table 2 (1 / 2)

| Product Name     | Overcharge<br>Detection<br>Voltage<br>[Vcu] | Overcharge<br>Release<br>Voltage<br>[V <sub>CL</sub> ] | Overdischarge<br>Detection<br>Voltage<br>[V <sub>DL</sub> ] | Overdischarge<br>Release<br>Voltage<br>[V <sub>DU</sub> ] | Discharge<br>Overcurrent 1<br>Detection<br>Voltage<br>[V <sub>DIOV1</sub> ] | Discharge<br>Overcurrent 2<br>Detection<br>Voltage<br>[V <sub>DIOV2</sub> ] | Load<br>Short-circuiting<br>Detection<br>Voltage<br>[Vshort] | Charge<br>Overcurrent<br>Detection<br>Voltage<br>[Vclov] |

|------------------|---------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------|

| S-82B5AAA-TCT1U7 | 4.225 V                                     | 4.025 V                                                | 2.500 V                                                     | 2.500 V                                                   | 50 mV                                                                       | 100 mV                                                                      | 400 mV                                                       | −50 mV                                                   |

Table 2 (2 / 2)

| Product Name     | Delay Time Combination <sup>*1</sup> | 0 V Battery Charge | Power-down Function | Release Condition of<br>Discharge Overcurrent<br>Status* <sup>2</sup> |

|------------------|--------------------------------------|--------------------|---------------------|-----------------------------------------------------------------------|

| S-82B5AAA-TCT1U7 | (1)                                  | Inhibited          | Available           | Load disconnection                                                    |

- \*1. Refer to **Table 3** about the details of the delay time combinations.

- \*2. Release condition of discharge overcurrent status: Load disconnection, charger connection

**Remark** Please contact our sales representatives for products other than the above.

#### Table 3

| Delay Time  | Overcharge Detection | Overdischarge Detection | Discharge Overcurrent 2 | Charge Overcurrent   |

|-------------|----------------------|-------------------------|-------------------------|----------------------|

| Combination | Delay Time           | Delay Time              | Detection Delay Time    | Detection Delay Time |

| Combination | [tcu]                | [t <sub>DL</sub> ]      | [t <sub>DIOV2</sub> ]   | [tclov]              |

| (1)         | 1.0 s                | 128 ms                  | 16 ms                   | 16 ms                |

**Remark** The delay times can be changed within the range listed in **Table 4**. For details, please contact our sales representatives.

### Table 4

| Delay Time                                   | Symbol             |        | Selection Range |        |        |        |        | Remark |                               |  |

|----------------------------------------------|--------------------|--------|-----------------|--------|--------|--------|--------|--------|-------------------------------|--|

| Overcharge detection delay time              | tcu                | 256 ms | 512 ms          | 1.0 s  | 2.0 s  | -      | -      | -      | Select a value from the left. |  |

| Overdischarge detection delay time           | $t_{DL}$           | 32 ms  | 64 ms           | 128 ms | 256 ms | 512 ms | 1.0 s  | -      | Select a value from the left. |  |

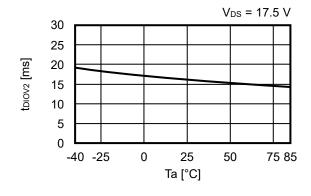

| Discharge overcurrent 2 detection delay time | t <sub>DIOV2</sub> | 4 ms   | 8 ms            | 16 ms  | 32 ms  | 64 ms  | -      | -      | Select a value from the left. |  |

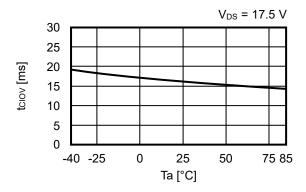

| Charge overcurrent detection delay time      | tciov              | 4 ms   | 8 ms            | 16 ms  | 32 ms  | 64 ms  | 128 ms | 256 ms | Select a value from the left. |  |

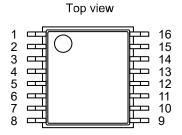

# ■ Pin Configuration

## 1. 16-Pin TSSOP

Figure 3

| Т | ab | le | 5 |

|---|----|----|---|

|---|----|----|---|

| Pin No. | Symbol  | Description                                        |

|---------|---------|----------------------------------------------------|

| 1       | VC1     | Connection pin for battery 1's positive voltage    |

| _       | V/C0    | Connection pin for battery 1's negative voltage,   |

| 2       | VC2     | Connection pin for battery 2's positive voltage    |

| 3       | VC3     | Connection pin for battery 2's negative voltage,   |

| 3       | VC3     | Connection pin for battery 3's positive voltage    |

| 4       | VC4     | Connection pin for battery 3's negative voltage,   |

| 4       | V 04    | Connection pin for battery 4's positive voltage    |

| 5       | VC5     | Connection pin for battery 4's negative voltage,   |

| 3       | VC3     | Connection pin for battery 5's positive voltage    |

| 6       | VSS     | Input pin for negative power supply,               |

|         | V 0 0   | Connection pin for battery 5's negative voltage    |

| 7       | VINI    | Voltage detection pin between VSS pin and VINI pin |

| 8       | CIT     | Capacitor connection pin for discharge overcurrent |

| 0       | CII     | 1 detection delay time                             |

| 9       | NC*1    | No connection                                      |

| 10      | TEST1*2 | Test pin                                           |

| 11      | PSI     | Control pin for power-saving                       |

| 40      | DO      | Connection pin of discharge control FET gate       |

| 12      | DO      | (CMOS output)                                      |

| 13      | NC*1    | No connection                                      |

| 4.4     | 00      | Connection pin of charge control FET gate          |

| 14      | CO      | (CMOS output)                                      |

| 15      | VM      | Voltage detection pin between VSS pin and VM pin   |

| 16      | VDD     | Input pin for positive power supply,               |

| 10      | VUU     | Connection pin for battery 1's positive voltage    |

<sup>\*1.</sup> The NC pin is electrically open. The NC pin can be connected to the VDD pin or the VSS pin.

<sup>\*2.</sup> Set the TEST1 pin open in use.

## ■ Absolute Maximum Ratings

Table 6

(Ta = +25°C unless otherwise specified)

| ltem                                      | Symbol            | Applied Pin   | Absolute Maximum Rating                                                   | Unit |

|-------------------------------------------|-------------------|---------------|---------------------------------------------------------------------------|------|

| Input voltage between VDD pin and VSS pin | V <sub>DS</sub>   | VDD           | Vss – 0.3 to Vss + 28.0                                                   | ٧    |

|                                           |                   | VC1           | $V_{VC2} - 0.3$ to $V_{VC2} + 6.0$                                        | V    |

| Input pin voltage 1                       | V <sub>IN1</sub>  | VC3           | $V_{VC4} - 0.3$ to $V_{DD} + 0.3 \le V_{VC4} + 6.0$                       | V    |

|                                           |                   | VC4           | $V_{\text{VC5}} - 0.3$ to $V_{\text{DD}} + 0.3 \leq V_{\text{VC5}} + 6.0$ | V    |

| Input pin voltage 2                       | V <sub>IN2</sub>  | VC2           | $V_{DD} - 6.0 \le V_{VC3} - 0.3$ to $V_{DD} + 0.3 \le V_{VC3} + 6.0$      | V    |

| Input pin voltage 3                       | V <sub>IN3</sub>  | VC5           | $V_{SS} - 0.3 \text{ to } V_{DD} + 0.3 \le V_{SS} + 6.0$                  | V    |

| Input pin voltage 4                       | V <sub>IN4</sub>  | TEST1, CIT    | $V_{SS}-0.3$ to $V_{SS}+6.0$                                              | V    |

| Input pin voltage 5                       | V <sub>IN5</sub>  | PSI, VM, VINI | $V_{DD}$ – 28.0 to $V_{DD}$ + 0.3                                         | V    |

| Output pin voltage 1                      | V <sub>OUT1</sub> | DO            | $V_{SS}-0.3$ to $V_{DD}+0.3 \leq V_{SS}+28.0$                             | V    |

| Output pin voltage 2                      | V <sub>OUT2</sub> | СО            | $V_{DD}-28.0 \leq V_{VM}-0.3$ to $V_{DD}+0.3$                             | V    |

| Operation ambient temperature             | T <sub>opr</sub>  | _             | -40 to +85                                                                | °C   |

| Storage temperature                       | T <sub>stg</sub>  | _             | -55 to +125                                                               | °C   |

Caution The absolute maximum ratings are rated values exceeding which the product could suffer physical damage. These values must therefore not be exceeded under any conditions.

## **■** Thermal Resistance Value

Table 7

| Item                                     | Symbol | Condition    |         | Min. | Тур. | Max. | Unit |

|------------------------------------------|--------|--------------|---------|------|------|------|------|

|                                          |        | 16-Pin TSSOP | Board A | 1    | 88   | 1    | °C/W |

|                                          | θЈΑ    |              | Board B | _    | 74   | _    | °C/W |

| Junction-to-ambient thermal resistance*1 |        |              | Board C | ı    |      | ı    | °C/W |

|                                          |        |              | Board D | 1    | 1    | 1    | °C/W |

|                                          |        |              | Board E | 1    | -    | 1    | °C/W |

<sup>\*1.</sup> Test environment: compliance with JEDEC STANDARD JESD51-2A

**Remark** Refer to "■ **Power Dissipation**" and "**Test Board**" for details.

## **■** Electrical Characteristics

Table 8 (1 / 2)

$(V1 = V2 = V3 = V4 = V5 = 3.5 \text{ V}, \text{ Ta} = +25^{\circ}\text{C} \text{ unless otherwise specified})$

| Item                                            | Symbol             | ,                               | Min.                          | Тур.               | Max.                    | Unit | Test<br>Circuit |

|-------------------------------------------------|--------------------|---------------------------------|-------------------------------|--------------------|-------------------------|------|-----------------|

| Detection Voltage                               |                    |                                 |                               |                    |                         |      |                 |

| Overcharge detection voltage n                  | Vcun               | -                               | $V_{\text{CU}}-0.020$         | Vcu                | $V_{CU} + 0.020$        | V    | 1               |

| Overcharge release voltage n                    | V <sub>CLn</sub>   | _                               | V <sub>CL</sub> - 0.050       | VcL                | V <sub>CL</sub> + 0.050 | V    | 1               |

| Overdischarge detection voltage n               | $V_{DLn}$          | _                               | V <sub>DL</sub> - 0.050       | $V_{DL}$           | V <sub>DL</sub> + 0.050 | V    | 1               |

| Overdischarge release voltage n                 | $V_{DUn}$          | _                               | V <sub>DU</sub> - 0.100       | V <sub>DU</sub>    | V <sub>DU</sub> + 0.100 | V    | 1               |

| Discharge overcurrent 1 detection voltage       | V <sub>DIOV1</sub> | _                               | V <sub>DIO1V</sub> – 5        | V <sub>DIOV1</sub> | V <sub>DIOV1</sub> + 5  | mV   | 1               |

| Discharge overcurrent 2 detection voltage       | $V_{\text{DIOV2}}$ | _                               | V <sub>DIOV2</sub> – 10       | V <sub>DIOV2</sub> | V <sub>DIOV2</sub> + 10 | mV   | 1               |

| Load short-circuiting detection voltage         | Vshort             | _                               | Vshort – 20                   | Vshort             | Vshort + 20             | mV   | 1               |

| Charge overcurrent detection voltage            | Vciov              | _                               | Vciov – 5                     | Vciov              | Vciov + 5               | mV   | 1               |

| Delay Time                                      |                    |                                 |                               |                    |                         |      |                 |

| CIT pin charge current                          | Ісіт               | _                               | 80                            | 120                | 170                     | nA   | 1               |

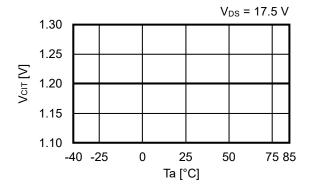

| CIT pin detection voltage                       | Vcit               | _                               | 1.1                           | 1.2                | 1.3                     | V    | 1               |

| Overcharge detection delay time                 | tcu                | _                               | tcu × 0.7                     | <b>t</b> cu        | tcu × 1.3               | _    | 1               |

| Overdischarge detection delay time              | <b>t</b> DL        | _                               | $t_{\text{DL}}\times 0.7$     | <b>t</b> DL        | $t_{DL} \times 1.3$     | _    | 1               |

| Discharge overcurrent 2 detection delay time    | tdiov2             | _                               | $t_{\text{DIOV2}} \times 0.7$ | t <sub>DIOV2</sub> | tdiov2 × 1.3            | _    | 1               |

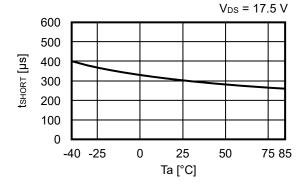

| Load short-circuiting detection delay time      | <b>t</b> short     | Internally fixed delay time     | 100                           | 300                | 600                     | μs   | 1               |

| Charge overcurrent detection delay time         | tciov              | _                               | $t$ ciov $\times$ $0.7$       | tciov              | tciov × 1.3             | -    | 1               |

| PSI pin response time                           | <b>t</b> psi       | _                               | 1.4                           | 2.0                | 2.6                     | ms   | 1               |

| 0 V Battery Charge                              |                    |                                 |                               |                    |                         |      |                 |

| 0 V battery charge starting charger voltage     | V <sub>0</sub> CHA | 0 V battery charge enabled      | -                             | 0.8                | 1.5                     | V    | 1               |

| 0 V battery charge inhibition battery voltage n | Voinh              | 0 V battery<br>charge inhibited | 1.0                           | 1.2                | 1.5                     | V    | 1               |

**Remark** n = 1, 2, 3, 4, 5

## Table 8 (2 / 2)

(V1 = V2 = V3 = V4 = V5 = 3.5 V,  $Ta = +25^{\circ}C$  unless otherwise specified)

|                                       | •                 | (V1 - V2 - V3 - V4 - V3 - 3 | .o v, ra - | 120 0 011100           | 30 01110111      | .00 Op    | Jooniou         |  |  |  |  |

|---------------------------------------|-------------------|-----------------------------|------------|------------------------|------------------|-----------|-----------------|--|--|--|--|

| Item                                  | Symbol            | Condition                   | Min.       | Тур.                   | Max.             | Unit      | Test<br>Circuit |  |  |  |  |

| Internal Resistance                   |                   |                             |            |                        |                  |           |                 |  |  |  |  |

| Resistance between VDD pin and VM pin | R <sub>VMD</sub>  | _                           | 0.5        | 1                      | 1.5              | $M\Omega$ | 1               |  |  |  |  |

| Resistance between VM pin and VSS pin | R <sub>VMS</sub>  | -                           | 7.5        | 15                     | 30               | kΩ        | 1               |  |  |  |  |

| Input Voltage                         |                   |                             |            |                        |                  |           |                 |  |  |  |  |

| Operation voltage between VDD pin and | .,                | Fixed output voltage of DO  | <b>-</b> 0 |                        | 04.0             | .,        | _               |  |  |  |  |

| VSS pin                               | VDSOP             | pin and CO pin              | 5.0        | _                      | 24.0             | V         | 1               |  |  |  |  |

| External control input pin            |                   |                             |            |                        |                  |           |                 |  |  |  |  |

| PSI pin reverse voltage "H"           | V <sub>PSIH</sub> | _                           | 0.8        | 1.0                    | 1.3              | V         | 1               |  |  |  |  |

| PSI pin reverse voltage "L"           | V <sub>PSIL</sub> | _                           | 0.5        | 0.8                    | 1.0              | V         | 1               |  |  |  |  |

| Input Current                         |                   |                             |            |                        |                  |           |                 |  |  |  |  |

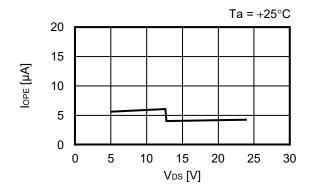

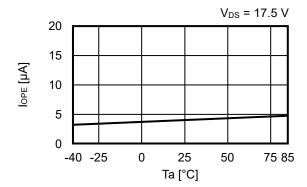

| Current consumption during operation  | IOPE              | -                           | _          | 4                      | 8                | μΑ        | 1               |  |  |  |  |

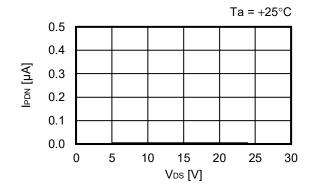

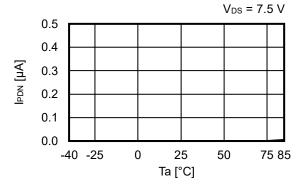

| Current consumption during power-down | I <sub>PDN</sub>  | -                           | -          | _                      | 0.1              | μΑ        | 1               |  |  |  |  |

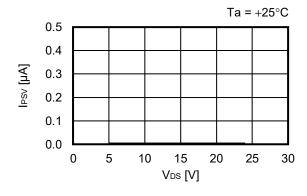

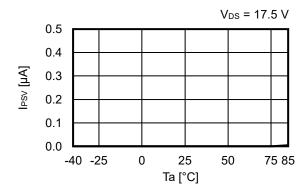

| Current consumption during            | I <sub>PSV</sub>  |                             |            |                        | 0.1              | μA        | 1               |  |  |  |  |

| power-saving                          | IPSV              | _                           |            | _                      | 0.1              | μΛ        | '               |  |  |  |  |

| VC1 pin current                       | I <sub>VC1</sub>  | -                           | -          | 0.25                   | 0.4              | μΑ        | 1               |  |  |  |  |

| VC2 pin current                       | I <sub>VC2</sub>  | _                           | -0.4       | 0.05                   | 0.4              | μΑ        | 1               |  |  |  |  |

| VC3 pin current                       | Ivcз              | -                           | -0.4       | -0.1                   | 0.4              | μΑ        | 1               |  |  |  |  |

| VC4 pin current                       | I <sub>VC4</sub>  | -                           | -0.4       | -0.1                   | 0.4              | μΑ        | 1               |  |  |  |  |

| VC5 pin current                       | I <sub>VC5</sub>  | -                           | -0.4       | -0.1                   | 0.4              | μΑ        | 1               |  |  |  |  |

| PSI pin current "H"                   | I <sub>PSIH</sub> | -                           | -400       | -200                   | -100             | nA        | 1               |  |  |  |  |

| PSI pin current "L"                   | I <sub>PSIL</sub> | _                           | 100        | 200                    | 400              | nA        | 1               |  |  |  |  |

| Output pin                            |                   |                             |            |                        |                  |           |                 |  |  |  |  |

| CO pin voltage "H"                    | V <sub>сон</sub>  | 4-serial cell               | -          | -                      | $V_{DD}$         | V         | 1               |  |  |  |  |

| CO pili voltage H                     | V COH             | 5-serial cell               | -          | V <sub>VC2</sub> - 0.5 | V <sub>VC2</sub> | V         | 1               |  |  |  |  |

| DO nin voltago "Ll"                   | \/= a             | 4-serial cell               | -          | -                      | V <sub>DD</sub>  | V         | 1               |  |  |  |  |

| DO pin voltage "H"                    | Vоон              | 5-serial cell               | 1          | V <sub>VC2</sub> - 0.5 | V <sub>VC2</sub> | V         | 1               |  |  |  |  |

| CO pin source current                 | Ісон              | _                           | 10         | -                      | 1                | μΑ        | 1               |  |  |  |  |

| CO pin sink current                   | Icol              | _                           | 180        | 200                    | -                | μΑ        | 1               |  |  |  |  |

| DO pin source current                 | Ірон              | _                           | 10         | _                      | 1                | μΑ        | 1               |  |  |  |  |

| DO pin sink current                   | I <sub>DOL</sub>  | -                           | 1700       | 2000                   | -                | μΑ        | 1               |  |  |  |  |

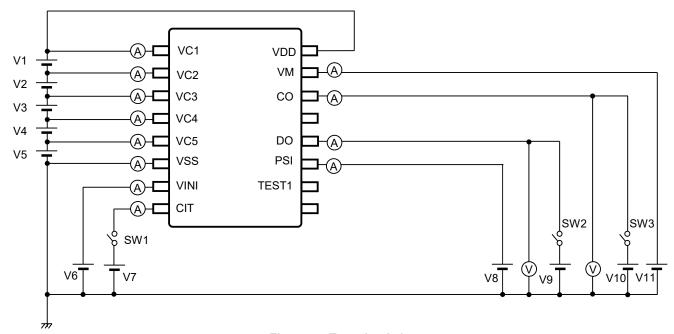

#### ■ Test Circuits

Caution Unless otherwise specified, the output voltage levels "H" and "L" at CO pin (V<sub>CO</sub>) and DO pin (V<sub>DO</sub>) are judged as follows.

L:  $[V_{CO}, V_{DO}] \le V_{DS} \times 0.1 \text{ V}$ H:  $[V_{CO}, V_{DO}] > V_{DS} \times 0.1 \text{ V}$

**Remark** V<sub>DS</sub>: Input voltage between VDD pin and VSS pin (V1 + V2 + V3 + V4 + V5)

Figure 4 Test circuit 1

This section provides explanations of Test items using Test circuit 1.

Perform each test after setting as shown in Table 9.

| Table 9 Initial Setting of Test Circuit 1 (1 / 2) |       |       |       |       |       |     |     |                 |    |     |     |     |     |     |

|---------------------------------------------------|-------|-------|-------|-------|-------|-----|-----|-----------------|----|-----|-----|-----|-----|-----|

| Symbol                                            | V1    | V2    | V3    | V4    | V5    | V6  | V7  | V8              | V9 | V10 | V11 | SW1 | SW2 | SW3 |

| Setting                                           | 3.5 V | 0 V | 0 V | V <sub>DS</sub> | _  | _   | 0 V | ON  | OFF | OFF |

#### 1. Overcharge detection voltage n (Vcun), overcharge release voltage n (VcLn)

Overcharge detection voltage 1 ( $V_{CU1}$ ) is defined as the voltage V1 at which  $V_{CO}$  goes from "H" to "L" when the voltage V1 is gradually increased after setting V1 = V2 = V3 = V4 = V5 =  $V_{CUn} - 0.05$  V. Overcharge release voltage 1 ( $V_{CL1}$ ) is defined as the voltage V1 at which  $V_{CO}$  goes from "L" to "H" when the voltage V1 is then gradually decreased after setting V2 = V3 = V4 = V5 =  $V_{CLn} - 0.05$  V, V11 = 0.2 V.

Overcharge detection voltage n ( $V_{CUn}$ ) and overcharge release voltage n ( $V_{CLn}$ ) (n = 2 to 5) can be determined in the same way as when n = 1.

#### 2. Overdischarge detection voltage n (V<sub>DLn</sub>), overdischarge release voltage n (V<sub>Dun</sub>)

Overdischarge detection voltage 1 ( $V_{DL1}$ ) is defined as the voltage V1 at which  $V_{D0}$  goes from "H" to "L" when the voltage V1 is gradually decreased. Overdischarge release voltage 1 ( $V_{DU1}$ ) is defined as the voltage V1 at which  $V_{D0}$  goes from "L" to "H" when the voltage V1 is then gradually increased after setting V11 = 0.2 V. Overdischarge detection voltage n ( $V_{DLn}$ ) and overdischarge release voltage n ( $V_{DUn}$ ) (n = 2 to 5) can be determined in the same way as when n = 1.

10

#### 3. Discharge overcurrent 1 detection voltage (VDIOV1)

Discharge overcurrent 1 detection voltage ( $V_{DIOV1}$ ) is defined as the voltage V6 at which CIT pin current changes from the direction of flowing into the IC to the direction of flowing out from the IC when the voltage V6 is gradually increased after setting V7 = 0.01 V.

#### 4. Discharge overcurrent 2 detection voltage (VDIOV2)

Discharge overcurrent 2 detection voltage ( $V_{DIOV2}$ ) is defined as the voltage V6 at which  $V_{DO}$  goes from "H" to "L" when the voltage V6 is gradually increased after setting V11 = 0.5 V.

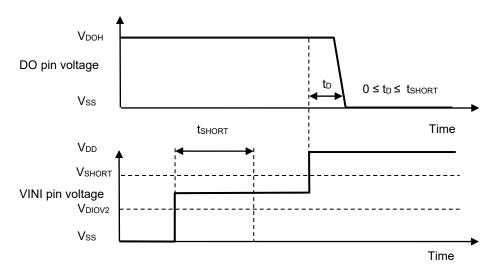

#### 5. Load short-circuiting detection voltage (VSHORT)

Load short-circuiting detection voltage ( $V_{SHORT}$ ) is defined as the voltage V6 at which delay time from when V6 is increased after setting V11 = 0.5 V to when  $V_{DO}$  goes from "H" to "L" is load short-circuiting detection delay time ( $t_{SHORT}$ ).

#### 6. Charge overcurrent detection voltage (Vciov)

Charge overcurrent detection voltage ( $V_{CIOV}$ ) is defined as the voltage V6 at which  $V_{CO}$  goes from "H" to "L" when the voltage V6 is gradually decreased after setting V11 = -0.1 V.

### 7. CIT pin charge current (ICIT), CIT pin detection voltage (VCIT)

CIT pin charge current ( $I_{CIT}$ ) is defined as the CIT pin current when setting V6 = ( $V_{DIOV1} + V_{DIOV2}$ ) / 2. CIT pin detection voltage ( $V_{CIT}$ ) is defined as the voltage V7 at which  $V_{DO}$  goes from "H" to "L" when the voltage V7 is then gradually increased.

#### 8. Overcharge detection delay time (tcu)

Overcharge detection delay time ( $t_{CU}$ ) is the time period from when the voltage V1 exceeds  $V_{CU1}$  after setting V1 = V2 = V3 = V4 = V5 = 3.5 V till when  $V_{CO}$  goes from "H" to "L".

### 9. Overdischarge detection delay time (t<sub>DL</sub>)

Overdischarge detection delay time ( $t_{DL}$ ) is the time period from when the voltage V1 falls below  $V_{DL1}$  after setting V1 = V2 = V3 = V4 = V5 = 3.5 V till when  $V_{DO}$  goes from "H" to "L".

#### 10. Discharge overcurrent 2 detection delay time (t<sub>DIOV2</sub>)

Discharge overcurrent 2 detection delay time ( $t_{DIOV2}$ ) is the time period from when the voltage V6 exceeds  $V_{DIOV2}$  after setting V11 = 0.5 V till when  $V_{DO}$  changes from "H" to "L".

## 11. Load short-circuiting detection delay time (tshort)

Load short-circuiting detection delay time ( $t_{SHORT}$ ) is the time period from when the voltage V6 exceeds  $V_{SHORT}$  after setting V11 = 0.5 V till when  $V_{DO}$  changes from "H" to "L".

#### 12. Charge overcurrent detection delay time (tciov)

Charge overcurrent detection delay time ( $t_{CIOV}$ ) is the time period from when the voltage V6 falls below  $V_{CIOV}$  after setting V11 = -0.1 V till when  $V_{CO}$  changes from "H" to "L".

#### 13. PSI pin response time (t<sub>PSI</sub>)

PSI pin response time ( $t_{PSI}$ ) is the time period from when the voltage V8 is changed to 0 V till when  $V_{DO}$  changes from "H" to "L".

#### 14. 0 V battery charge starting charger voltage (V₀cHA) (0 V battery charge enabled)

This IC reaches the overdischarge status after setting V1 =  $V_{DL1} - 0.1$  V. Then set V1 = V2 = V3 = V4 = V5 = 0 V. 0 V battery charge starting charger voltage ( $V_{0CHA}$ ) is defined as the absolute value of voltage V11 at which I<sub>CO</sub> exceeds 1.0  $\mu$ A when the voltage V11 is then gradually decreased after setting SW3 ON and V10 = V11 = -0.5 V.

#### 15. 0 V battery charge inhibition battery voltage n (Voinhn) (0 V battery charge inhibited)

0 V battery charge inhibition battery voltage 1 ( $V_{0INH1}$ ) is defined as the voltage V1 at which  $V_{CO}$  goes from "H" to "L" when the voltage V1 is gradually decreased after setting V1 = V2 = V3 = V4 = V5 =  $V_{DLn} - 0.1$  V.

0 V battery charge inhibition battery voltage n (VolNHn) (n = 2 to 5) can be determined in the same way as when n = 1.

## 16. Resistance between VM pin and VDD pin (R<sub>VMD</sub>)

Resistance between VM pin and VDD pin ( $R_{VMD}$ ) is defined by  $R_{VMD} = (V_{DS} + 0.1) / I_{VM}$  using  $I_{VM}$  when setting V1 = V2 = V3 = V4 = V5 = 1.5 V and V11= -0.1 V.

#### 17. Resistance between VM pin and VSS pin (R<sub>VMS</sub>)

Resistance between VM pin and VSS pin ( $R_{VMS}$ ) is defined by  $R_{VMS}$  = V11 /  $I_{VM}$  using  $I_{VM}$  when setting V6 = 1.0 V and V11 = 2.0 V.

## 18. PSI pin reverse voltage "H" (VPSIH)

PSI pin reverse voltage "H" ( $V_{PSIH}$ ) is defined as the voltage V8 at which  $V_{DO}$  goes from "L" to "H" when the voltage V8 is gradually increased after setting V8 = 0 V.

#### 19. PSI pin reverse voltage "L" (V<sub>PSIL</sub>)

PSI pin reverse voltage "L" ( $V_{PSIL}$ ) is defined as the voltage V8 at which  $V_{DO}$  goes from "H" to "L" when the voltage V8 is gradually decreased.

#### 20. Current consumption during operation (IOPE)

Current consumption during operation (IOPE) is defined as the sum of VSS pin current, VM pin current and VINI pin current after setting SW1 OFF.

## 21. Current consumption during power-down (IPDN)

Current consumption during power-down (IPDN) is defined as Ivss under the setting conditions of V1 = V2 = V3 = V4 = V5 = 1.5 V and V11 =  $V_{DS}$ .

#### 22. Current consumption during power-saving (IPSV)

Current consumption during power-saving ( $I_{PSV}$ ) is defined as  $I_{VSS}$  under the setting conditions of V8 = 0 V and V11 =  $V_{DS}$ .

## 23. PSI pin current "H" (IPSIH), PSI pin current "L" (IPSIL)

PSI pin current "H" (I<sub>PSIH</sub>) is defined as I<sub>PSI</sub> when setting V8 = V<sub>DS</sub> - 1 V after setting V8 = V<sub>DS</sub>. PSI pin current "L" (I<sub>PSIL</sub>) is defined as I<sub>PSI</sub> when setting V8 = (V<sub>PSIH</sub> + V<sub>PSIL</sub>) / 2 after setting V8 = 0 V.

#### 24. CO pin voltage "H" (Vcoh), CO pin source current (Icoh)

CO pin voltage "H" ( $V_{COH}$ ) is defined as CO pin voltage ( $V_{CO}$ ) in the settings shown in **Table 9**. CO pin source current ( $I_{COH}$ ) is defined as  $I_{CO}$  when setting V10 =  $V_{COH}$  – 0.5 V and SW3 ON.

#### 25. CO pin sink current (Icol)

CO pin sink current (I<sub>COL</sub>) is defined as I<sub>CO</sub> when setting V1 = V<sub>CU1</sub> + 0.1 V, V10 = 0.5 V and SW3 ON.

# BATTERY PROTECTION IC FOR 4-SERIAL OR 5-SERIAL-CELL PACK S-82B4A/5A Series

## Rev.1.0\_00

## 26. DO pin voltage "H" ( $V_{DOH}$ ), DO pin source current ( $I_{DOH}$ )

DO pin voltage "H" ( $V_{DOH}$ ) is defined as DO pin voltage ( $V_{DO}$ ) in the settings shown in **Table 9**. DO pin source current ( $I_{DOH}$ ) is defined as  $I_{DO}$  when setting V9 =  $V_{DOH}$  – 0.5 V and SW2 ON.

## 27. DO pin sink current (IDOL)

DO pin sink current ( $I_{DOL}$ ) is defined as  $I_{DO}$  when setting V1 =  $V_{DL1} - 0.1 \text{ V}$ , V9 = 0.5 V and SW2 ON.

Rev.1.0\_00

## Operation

Remark Refer to "■ Battery Protection IC Connection Example".

#### 1. Normal status

The status when the CO pin output voltage ( $V_{CO}$ ) = "H" and DO pin output voltage ( $V_{DO}$ ) = "H" is the normal status. CO pin voltage "H" ( $V_{COH}$ ) is the voltage  $V_{CO}$  when the  $V_{CO}$  is "H". DO pin voltage "H" ( $V_{DOH}$ ) is the voltage  $V_{DO}$  when the  $V_{DO}$  is "H".

All the conditions mentioned below should be satisfied for returning to the normal status.

- The voltage of each of the batteries is in the range from the overcharge detection voltage n (V<sub>CUn</sub>) to overdischarge detection voltage n (V<sub>DLn</sub>).

- The VINI pin voltage is in the range of the charge overcurrent detection voltage (V<sub>CIOV</sub>) to discharge overcurrent 1 detection voltage (V<sub>DIOV1</sub>).

- The PSI pin voltage is higher than the PSI pin reverse voltage "H" (VPSIH).

Caution After a battery is connected, there may be cases when discharging cannot be performed. In this case, this IC returns to the normal status when any of the following conditions is satisfied.

- (1) Connecting a charger

- (2) Shorting between the VM pin and the VSS pin

- (3) Changing the PSI pin voltage to be  $V_{DS} \rightarrow 0 \ V \rightarrow V_{DS}$

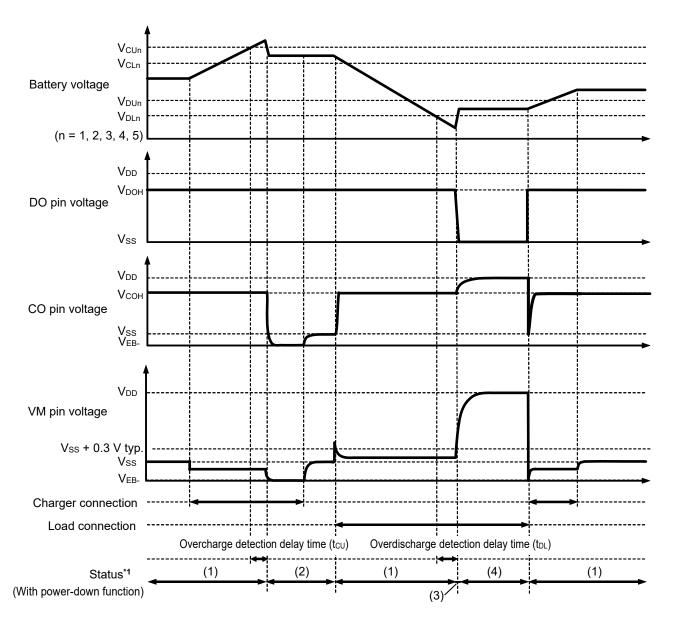

#### 2. Overcharge status

When the voltage of any of the batteries exceeds the overcharge detection voltage n ( $V_{CUn}$ ) and the status continues for the overcharge detection delay time ( $t_{CU}$ )\*1 or longer, the CO pin changes to VM pin voltage. This is the overcharge status. In this case, the charge control FET is turned off and charging is stopped.

The overcharge status is released if either condition mentioned below is satisfied.

- (1)  $V_{VM} < 0.3 \ V$  typ., and voltage of all batteries  $\leq V_{CLn}$

- (2)  $V_{VM} \ge 0.3 \text{ V typ.}$ , and voltage of all batteries  $\le V_{CUn}$

\*1. Refer to "6. Delay time setting" for details.

Remark V<sub>VM</sub>: VM pin voltage

$V_{\text{CUn}}$ : Overcharge detection voltage n (n = 1, 2, 3, 4, 5)  $V_{\text{CLn}}$ : Overcharge release voltage n (n = 1, 2, 3, 4, 5)

14 ABLIC Inc.

#### 3. Overdischarge status

When the voltage of any of the batteries decreases to the overdischarge detection voltage n ( $V_{DLn}$ ) or lower and the status continues for the overdischarge detection delay time ( $t_{DL}$ )\*1 or longer, the DO pin changes to the  $V_{SS}$  level. This is the overdischarge status. The discharge control FET is turned off and discharging is stopped.

The overdischarge status is released if either condition mentioned below is satisfied.

- (1)  $V_{VM} \le 0 \text{ V typ.}$ , and voltage of all batteries  $\ge V_{DLn}$

- (2)  $V_{VM} > 0$  V typ., and voltage of all battery  $\geq V_{DUn}$

#### \*1. Refer to "6. Delay time setting" for details.

Remark V<sub>VM</sub>: VM pin voltage

$V_{DLn}$ : Overdischarge detection voltage n (n = 1, 2, 3, 4, 5)  $V_{DUn}$ : Overdischarge release voltage n (n = 1, 2, 3, 4, 5)

#### 3. 1 With power-down function

When this IC reaches the overdischarge status, the VM pin is pulled up to the  $V_{DD}$  level by a resistance between VM pin and VDD pin ( $R_{VMD}$ ). If the VM pin voltage changes to 0.7 V typ. or higher, the power-down function starts to operate and most operations in this IC halt. The CO pin changes to VM pin voltage. In this case, the charge control FET is turned off and charging is stopped.

By connecting a battery charger, the power-down function is released when the VM pin voltage is 0.7 V typ. or lower.

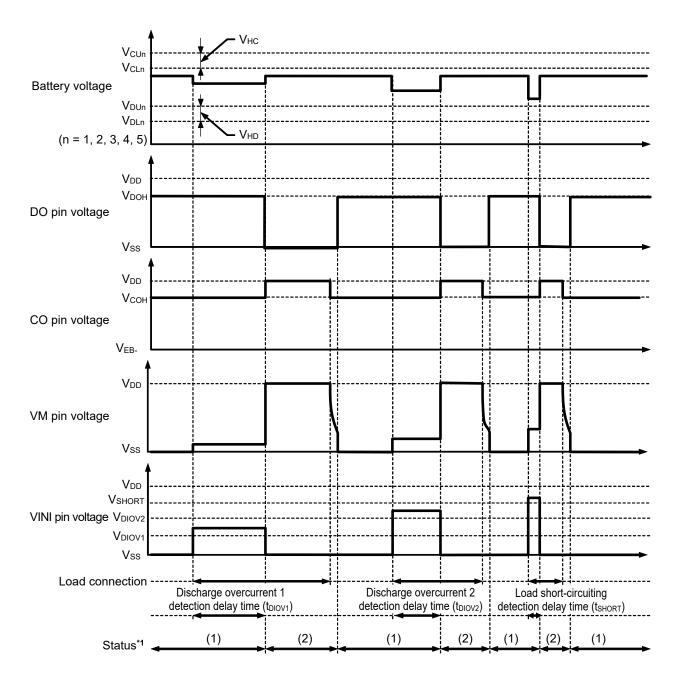

#### 4. Discharge overcurrent status

When the discharge current increases to a certain value or more, the VINI pin voltage increases to the level of discharge overcurrent 1 detection voltage (VDIOV1) or higher. If the condition continues for the discharge overcurrent 1 detection delay time (tDIOV1)\*1 or longer, the DO pin changes to the Vss level. This is the discharge overcurrent status. The discharge control FET is turned off and discharging is stopped.

Discharge overcurrent is detected at the following three levels: VDIOV1, VDIOV2, and VSHORT. When discharge overcurrent 2 detection voltage (VDIOV2) and load short-circuiting detection voltage (VSHORT) are detected, the same operations as VDIOV1 detection are performed.

## 4. 1 Release condition of discharge overcurrent status "Load disconnection"

Under the discharge overcurrent status, VM pin and VSS pin are shorted by  $R_{VMS}$  in this IC. However, the VM pin voltage is the  $V_{DD}$  level due to the load as long as the load is connected. When the load is disconnected, the VM pin voltage returns to the Vss level. When the VM pin voltage returns to  $V_{DS}/3$  or lower, this IC releases the discharge overcurrent status.

$R_{\text{VMD}}$  is not connected in the discharge overcurrent status.

## 4. 2 Release condition of discharge overcurrent status "Charger connection"

Under the discharge overcurrent status, VDD pin and VM pin are shorted by  $R_{VMD}$  in this IC. When a battery is connected to a charger and VM pin voltage returns to  $V_{DIOV1}$  or lower, this IC releases the discharge overcurrent status.

R<sub>VMS</sub> is not connected in the discharge overcurrent status.

#### Charge overcurrent status

When the charge current increases to a certain value or more, the VINI pin voltage decreases to the level of charge overcurrent detection voltage (Vciov) or lower. If the status continues for the charge overcurrent detection delay time (tciov)\*1 or longer, the CO pin voltage changes to the VM pin voltage. This is the charge overcurrent status. In this case, the charge control FET is turned off and charging is stopped. The VM pin is pulled up to the VDD level by a resistance between VM pin and VDD pin (RVMD).

The charge overcurrent status is released if the VM pin voltage increases 0.3 V typ. or higher.

\*1. Refer to "6. Delay time setting" for details.

#### 6. Delay time setting

Users are able to set delay time for the period from when this IC detects change in the voltage of any of the batteries or the VINI pin until when it outputs to the CO pin or DO pin. The discharge overcurrent 1 detection delay time (t<sub>DIOV1</sub>) is determined by constant current in this IC and an external capacitor. The other detection delay times are fixed internally.

#### 6. 1 Other than discharge overcurrent 1 detection delay time (tDIOV1)

The detection delay times are determined by dividing a clock of approximately 4 kHz by the counter.

Remark t<sub>DIOV2</sub> and t<sub>SHORT</sub> start when V<sub>DIOV2</sub> is detected. When V<sub>SHORT</sub> is detected over t<sub>SHORT</sub> after the detection of V<sub>DIOV2</sub>, this IC turns the discharge control FET off within t<sub>DIOV2</sub> or t<sub>SHORT</sub> of each detection.

Figure 5

#### 6. 2 Discharge overcurrent 1 detection delay time (t<sub>DIOV1</sub>)

In the discharge overcurrent 1 detection, when the VINI pin voltage increases to discharge overcurrent 1 detection voltage (VDIOV1) or higher, the internal circuit of this IC starts charging to an external capacitor connected to the CIT pin via the CIT pin current (ICIT) = 120 nA typ. When the CIT pin voltage increases to the CIT pin detection voltage (VCIT) or higher, the DO pin voltage changes to Vss level. This period is discharge overcurrent 1 detection delay time (IDIOV1).

$t_{\text{DIOV1}}$  is calculated by the following formula.

$t_{\text{DIOV1}}$  [s] =  $C_{\text{CIT}}$  [F]  $\times$   $V_{\text{CIT}}$  [V] /  $I_{\text{CIT}}$  [A]

If  $C_{CIT} = 0.01 \,\mu\text{F}$ ,  $t_{DIOV1}$  is calculated as follows:

$t_{DIOV1}$  [s] = 0.01  $\mu$ F × 1.2 V typ. / 120 nA typ. = 100 ms typ.

### 7. 0 V Battery charge function

Regarding how to charge a self-discharged battery (0 V battery), users are able to select either function mentioned below.

- (1) 0 V battery charge enabled

- A 0 V battery is charged when charger voltage is higher than the 0 V battery charge starting charger voltage (V<sub>0CHA</sub>).

- (2) 0 V battery charge inhibited

- A 0 V battery is not charged when the voltage of any of the batteries is the 0 V battery charge inhibition battery voltage n ( $V_{OINHn}$ ) or lower.

Caution When the VDD pin voltage is lower than the minimum value of operation voltage between the VDD pin and VSS pin (VDSOP), this IC's operation is not assured.

**Remark** n = 1, 2, 3, 4, 5

### 8. PSI pin

When the PSI pin is activated, the power-saving function starts to operate, and most operations halt. In this case, the CO pin changes to the VM pin level, and DO pin changes to the Vss level.

PSI pin

CO pin

DO pin

$V_{PSIH} \le PSI$  pin voltage ≤  $V_{DD}$  level

"H"

"H"

$V_{PSIL} < PSI$  pin voltage <  $V_{PSIH}$  Maintains the status

Maintains the status

$V_{SS}$  level ≤ PSI pin voltage ≤  $V_{PSIL}$  VM pin level

Vss level

Table 10 Status Set by PSI Pin

This IC is initialized and becomes the normal status by deactivating the PSI pin after activating PSI pin and enabling the power-saving function. As a result, each detection operation is carried out after returning to the normal status.

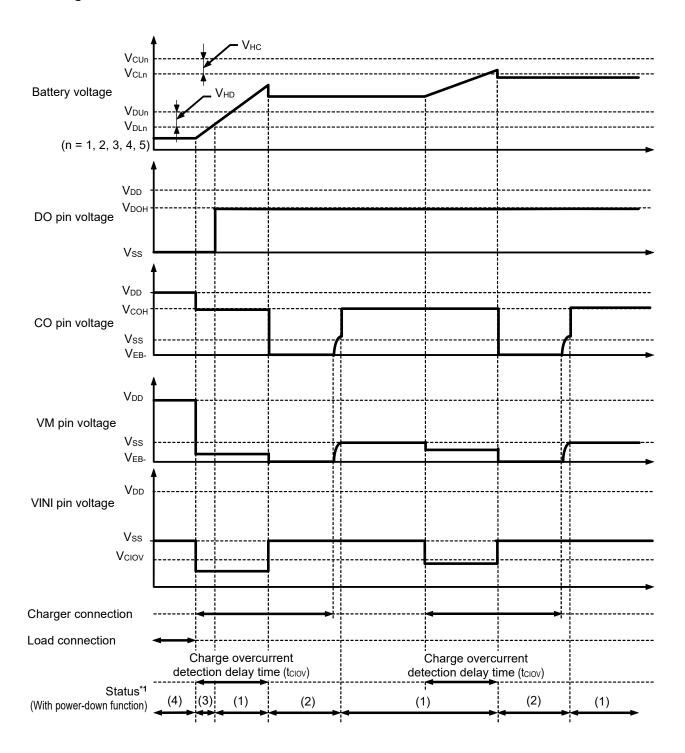

## ■ Timing Charts

## 1. Overcharge detection, overdischarge detection

Figure 6

\*1. (1): Normal status

(2): Overcharge status

(3): Overdischarge status

(4): Power-down status

## 2. Discharge overcurrent detection

Figure 7

\*1. (1): Normal status

(2): Discharge overcurrent status

## 3. Charge overcurrent detection

Figure 8

\*1. (1): Normal status

(2): Charge overcurrent status(3): Overdischarge status(4): Power-down status

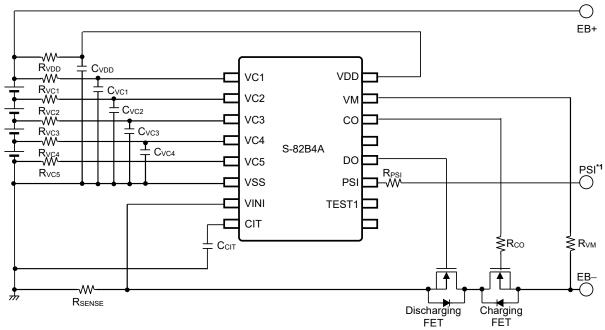

## **■** Connection Examples of Battery Protection IC

## 1. S-82B4A Series (4-serial cell)

Figure 9

\*1. If you do not use the power-saving function, connect the PSI pin to the VDD pin.

Remark Regarding the recommended values for external components, refer to "Table 11 Constants for External Components".

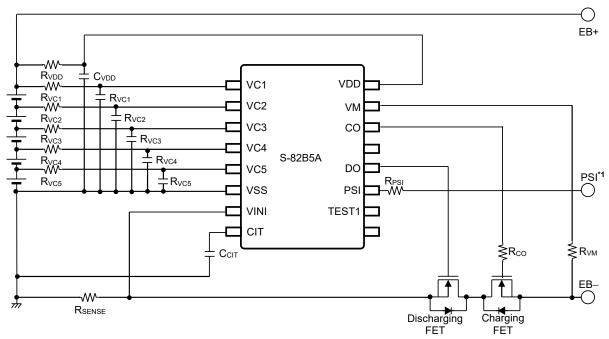

## 2. S-82B5A Series (5-serial cell)

Figure 10

\*1. If you do not use the power-saving function, connect the PSI pin to the VDD pin.

Remark Regarding the recommended values for external components, refer to "Table 11 Constants for External Components".

Table 11 Constants for External Components

| Symbol                               | Тур.         | Unit  |

|--------------------------------------|--------------|-------|

| R <sub>VDD</sub>                     | 100          | Ω     |

| R <sub>VCn</sub> (n = 1, 2, 3, 4, 5) | 1            | kΩ    |

| R <sub>PSI</sub>                     | 1            | kΩ    |

| R <sub>CO</sub>                      | 1            | kΩ    |

| R <sub>VM</sub>                      | 1            | kΩ    |

| R <sub>SENSE</sub>                   | _            | m $Ω$ |

| C <sub>VDD</sub>                     | 1            | μF    |

| C <sub>VCn</sub> (n = 1, 2, 3, 4, 5) | 0.1          | μF    |

| Ccit                                 | 0.01 or more | μF    |

## Caution 1. The constants may be changed without notice.

- 2. Sufficient evaluation of transient power supply fluctuation and overcurrent protection function with the actual application is needed to determine the proper constants when setting the filter constants between the VDD pin and VSS pin. Contact our sales representatives if setting the constants between the VDD pin and VSS pin to anything other than the recommended values.

- 3. It has not been confirmed whether the operation is normal or not in circuits other than the connection examples. In addition, the connection examples and the constants do not guarantee proper operation. Perform thorough evaluation using the actual application to set the constants.

#### Precautions

- The application conditions for the input voltage, output voltage, and load current should not exceed the power dissipation.

- Batteries can be connected in any order; however, there may be cases when discharging cannot be performed after a battery is connected. In this case, this IC returns to the normal status when any of the following conditions is satisfied.

- (1) Connecting a charger

- (2) Shorting between the VM pin and the VSS pin

- (3) Changing the PSI pin voltage to be  $V_{DS} \, o \, 0 \; V \, o \, V_{DS}$

- If an overcharged battery and an overdischarged battery intermix, this IC will change to the overcharge and overdischarge statuses. Therefore, in this case, both charging and discharging are impossible.

- Do not apply an electrostatic discharge to this IC that exceeds the performance ratings of the built-in electrostatic protection circuit.

- ABLIC Inc. claims no responsibility for any disputes arising out of or in connection with any infringement by products including this IC of patents owned by a third party.

## ■ Characteristics (Typical Data)

## 1. Current consumption

## 1. 1 IOPE VS. VDS

#### 1. 2 IOPE vs. Ta

#### 1. 3 IPDN VS. VDS

1. 4 IPDN vs. Ta

1. 5 IPSV VS. VDS

1. 6 I<sub>PSV</sub> vs. Ta

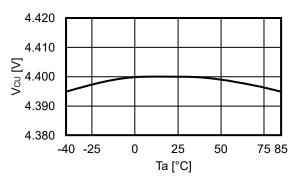

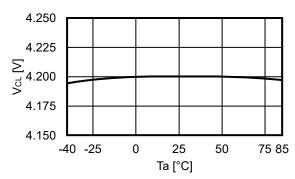

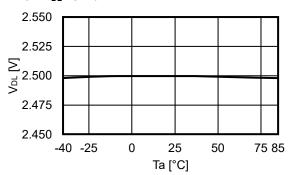

## 2. Detection voltage, release voltage

#### 2. 1 Vcu vs. Ta

#### 2. 2 V<sub>CL</sub> vs. Ta

2. 3 V<sub>DL</sub> vs. Ta

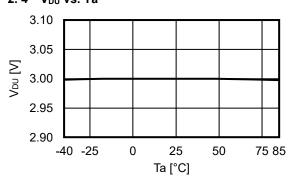

2. 4 V<sub>DU</sub> vs. Ta

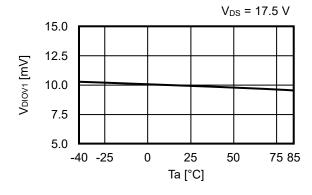

2. 5 V<sub>DIOV1</sub> vs. Ta

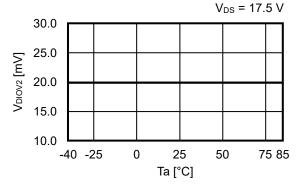

2. 6 V<sub>DIOV2</sub> vs. Ta

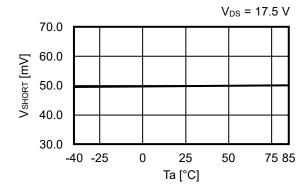

2. 7 V<sub>SHORT</sub> vs. Ta

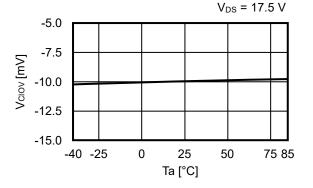

2. 8 V<sub>CIOV</sub> vs. Ta

## 3. Delay time function

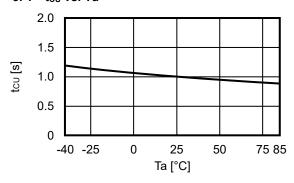

#### 3. 1 t<sub>CU</sub> vs. Ta

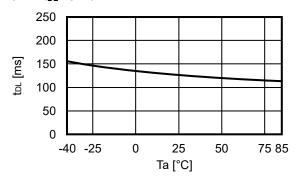

#### 3. 2 t<sub>DL</sub> vs. Ta

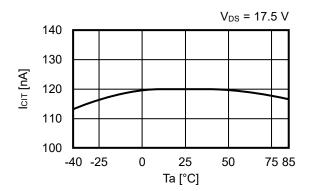

#### 3. 3 Icit vs. Ta

3. 4 Vcit vs. Ta

## 3. 5 t<sub>DIOV2</sub> vs. Ta

3. 6 tshort vs. Ta

## 3. 7 tciov vs. Ta

## 4. Output pin

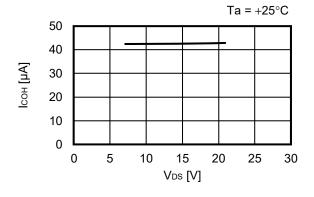

## 4. 1 Icon vs. VDS

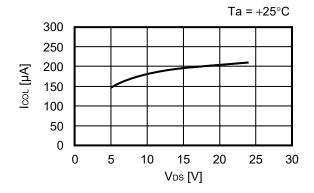

#### 4. 2 Icol vs. VDS

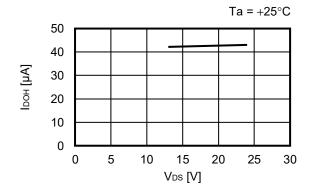

#### 4. 3 IDOH VS. VDS

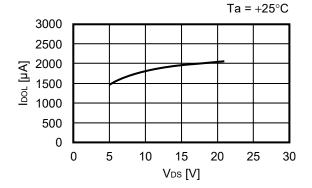

#### 4. 4 IDOL VS. VDS

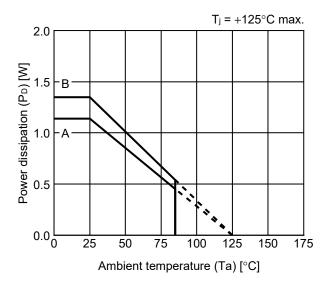

# **■** Power Dissipation

## 16-Pin TSSOP

| Board | Power Dissipation (P <sub>D</sub> ) |  |  |

|-------|-------------------------------------|--|--|

| Α     | 1.14 W                              |  |  |

| В     | 1.35 W                              |  |  |

| С     | _                                   |  |  |

| D     | _                                   |  |  |

| Е     | -                                   |  |  |

# 16-Pin TSSOP Test Board

## (1) Board A

| Item                     |      | Specification                               |  |  |

|--------------------------|------|---------------------------------------------|--|--|

| Size [mm]                |      | 114.3 x 76.2 x t1.6                         |  |  |

| Material                 |      | FR-4                                        |  |  |

| Number of copper foil la | ayer | 2                                           |  |  |

|                          | 1    | Land pattern and wiring for testing: t0.070 |  |  |

| Copper foil layer [mm]   | 2    | -                                           |  |  |

| Copper foil layer [min]  | 3    | -                                           |  |  |

|                          | 4    | 74.2 x 74.2 x t0.070                        |  |  |

| Thermal via              |      | -                                           |  |  |

# (2) Board B

| Item                     |      | Specification                               |  |  |

|--------------------------|------|---------------------------------------------|--|--|

| Size [mm]                |      | 114.3 x 76.2 x t1.6                         |  |  |

| Material                 |      | FR-4                                        |  |  |

| Number of copper foil la | ayer | 4                                           |  |  |

|                          | 1    | Land pattern and wiring for testing: t0.070 |  |  |

| Coppor foil lover [mm]   | 2    | 74.2 x 74.2 x t0.035                        |  |  |

| Copper foil layer [mm]   | 3    | 74.2 x 74.2 x t0.035                        |  |  |

|                          | 4    | 74.2 x 74.2 x t0.070                        |  |  |

| Thermal via              |      | -                                           |  |  |

No. TSSOP16-A-Board-SD-1.0

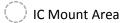

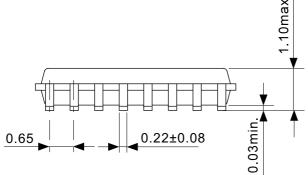

# No. FT016-A-P-SD-1.2

| TITLE      | TSSOP16-A-PKG Dimensions |  |  |  |  |  |  |

|------------|--------------------------|--|--|--|--|--|--|

| No.        | FT016-A-P-SD-1.2         |  |  |  |  |  |  |

| ANGLE      | <b>\$</b> E              |  |  |  |  |  |  |

| UNIT       | mm                       |  |  |  |  |  |  |

|            |                          |  |  |  |  |  |  |

|            |                          |  |  |  |  |  |  |

|            |                          |  |  |  |  |  |  |

| ABLIC Inc. |                          |  |  |  |  |  |  |

Feed direction

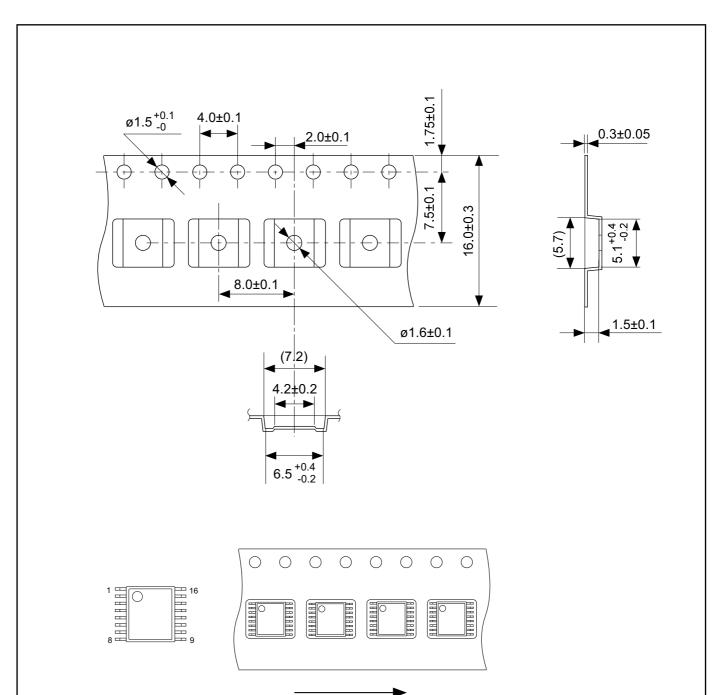

No. FT016-A-C-SD-1.1

| TITLE      | TSSOP16-A-Carrier Tape |  |  |  |  |  |  |  |

|------------|------------------------|--|--|--|--|--|--|--|

| No.        | FT016-A-C-SD-1.1       |  |  |  |  |  |  |  |

| ANGLE      |                        |  |  |  |  |  |  |  |

| UNIT       | mm                     |  |  |  |  |  |  |  |

|            |                        |  |  |  |  |  |  |  |

|            |                        |  |  |  |  |  |  |  |

|            |                        |  |  |  |  |  |  |  |

| ABLIC Inc. |                        |  |  |  |  |  |  |  |

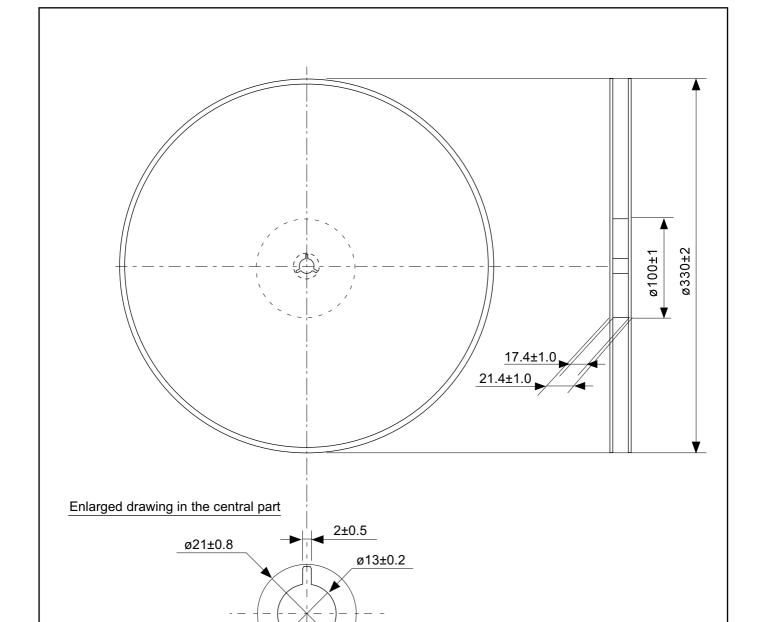

# No. FT016-A-R-S1-2.0

| TITLE      | TITLE TSSOP16-A- Reel |  |  |  |  |  |  |  |  |

|------------|-----------------------|--|--|--|--|--|--|--|--|

| No.        | FT016-A-R-S1-2.0      |  |  |  |  |  |  |  |  |

| ANGLE      | QTY. 4,000            |  |  |  |  |  |  |  |  |

| UNIT       | mm                    |  |  |  |  |  |  |  |  |

|            |                       |  |  |  |  |  |  |  |  |

|            |                       |  |  |  |  |  |  |  |  |

|            |                       |  |  |  |  |  |  |  |  |

| ABLIC Inc. |                       |  |  |  |  |  |  |  |  |

## **Disclaimers (Handling Precautions)**

- 1. All the information described herein (product data, specifications, figures, tables, programs, algorithms and application circuit examples, etc.) is current as of publishing date of this document and is subject to change without notice.

- 2. The circuit examples and the usages described herein are for reference only, and do not guarantee the success of any specific mass-production design.

- ABLIC Inc. is not liable for any losses, damages, claims or demands caused by the reasons other than the products described herein (hereinafter "the products") or infringement of third-party intellectual property right and any other right due to the use of the information described herein.

- 3. ABLIC Inc. is not liable for any losses, damages, claims or demands caused by the incorrect information described herein.

- 4. Be careful to use the products within their ranges described herein. Pay special attention for use to the absolute maximum ratings, operation voltage range and electrical characteristics, etc.

- ABLIC Inc. is not liable for any losses, damages, claims or demands caused by failures and / or accidents, etc. due to the use of the products outside their specified ranges.

- 5. Before using the products, confirm their applications, and the laws and regulations of the region or country where they are used and verify suitability, safety and other factors for the intended use.

- 6. When exporting the products, comply with the Foreign Exchange and Foreign Trade Act and all other export-related laws, and follow the required procedures.

- 7. The products are strictly prohibited from using, providing or exporting for the purposes of the development of weapons of mass destruction or military use. ABLIC Inc. is not liable for any losses, damages, claims or demands caused by any provision or export to the person or entity who intends to develop, manufacture, use or store nuclear, biological or chemical weapons or missiles, or use any other military purposes.

- 8. The products are not designed to be used as part of any device or equipment that may affect the human body, human life, or assets (such as medical equipment, disaster prevention systems, security systems, combustion control systems, infrastructure control systems, vehicle equipment, traffic systems, in-vehicle equipment, aviation equipment, aerospace equipment, and nuclear-related equipment), excluding when specified for in-vehicle use or other uses by ABLIC, Inc. Do not apply the products to the above listed devices and equipments.

- ABLIC Inc. is not liable for any losses, damages, claims or demands caused by unauthorized or unspecified use of the products.

- 9. In general, semiconductor products may fail or malfunction with some probability. The user of the products should therefore take responsibility to give thorough consideration to safety design including redundancy, fire spread prevention measures, and malfunction prevention to prevent accidents causing injury or death, fires and social damage, etc. that may ensue from the products' failure or malfunction.

- The entire system in which the products are used must be sufficiently evaluated and judged whether the products are allowed to apply for the system on customer's own responsibility.

- 10. The products are not designed to be radiation-proof. The necessary radiation measures should be taken in the product design by the customer depending on the intended use.

- 11. The products do not affect human health under normal use. However, they contain chemical substances and heavy metals and should therefore not be put in the mouth. The fracture surfaces of wafers and chips may be sharp. Be careful when handling these with the bare hands to prevent injuries, etc.

- 12. When disposing of the products, comply with the laws and ordinances of the country or region where they are used.

- 13. The information described herein contains copyright information and know-how of ABLIC Inc. The information described herein does not convey any license under any intellectual property rights or any other rights belonging to ABLIC Inc. or a third party. Reproduction or copying of the information from this document or any part of this document described herein for the purpose of disclosing it to a third-party is strictly prohibited without the express permission of ABLIC Inc.

- 14. For more details on the information described herein or any other questions, please contact ABLIC Inc.'s sales representative.

- 15. This Disclaimers have been delivered in a text using the Japanese language, which text, despite any translations into the English language and the Chinese language, shall be controlling.