## S-19954/19955 Series

## AUTOMOTIVE, 125°C OPERATION, 5.5 V INPUT, 1 A, POWER GOOD, SYNCHRONOUS **STEP-DOWN SWITCHING REGULATOR**

© ABLIC Inc., 2023-2024

www.ablic.com

Rev.1.3 00

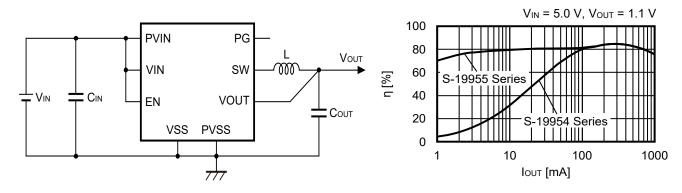

This IC is a secondary step-down switching regulator developed using CMOS process technologies with a built-in Power Good function.

PWM control (S-19954 Series) or PWM / PFM switching control (S-19955 Series) can be selected as an option.

S-19954 Series, which features PWM control, can be used without interfering with AM radio bands.

Since the S-19955 Series, which features PWM / PFM switching control, operates with PWM control under heavy load and automatically switches to PFM control under light load. It achieves high-efficiency operation in accordance with the device's status.

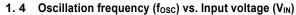

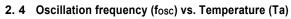

This IC is implemented as a small package and can comprise an application circuit with an inductor and two capacitors at the minimum configuration. Since the switching frequency is as high as 2.25 MHz, and the peripheral parts can be made compact, the IC is suitable for space-saving uses.

ABLIC Inc. offers FIT rate calculated based on actual customer usage conditions in order to support customer functional safety desian.

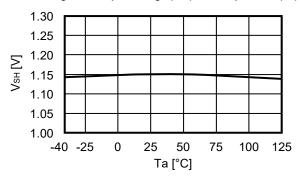

For more information regarding our FIT rate calculation, contact our sales representatives.

Caution This product can be used in vehicle equipment and in-vehicle equipment. Before using the product for these purposes, it is imperative to contact our sales representatives.

## Features

- Input voltage:

- Output voltage:

- Output current:

- VOUT pin detection voltage accuracy:

- Efficiency:

- Oscillation frequency:

- Overcurrent protection function:

- Thermal shutdown function:

- Short-circuit protection function:

- 100% duty cycle operation

- Output discharge function:

- Power Good function:

- Soft-start function:

- Under voltage lockout function (UVLO):

- Input and output capacitors:

- Operation temperature range:

- Lead-free (Sn 100%), halogen-free

- AEC-Q100 gualified<sup>\*1</sup>

- 2.7 V to 5.5 V 0.8 V to 3.3 V

- 1 A

- $\pm 1.5\%$  (T<sub>j</sub> =  $-40^{\circ}$ C to  $+125^{\circ}$ C)

- 95%

- 2.25 MHz typ.

- 170°C typ. (detection temperature)

- Hiccup control, Latch control

- "Available " / "Unavailable " is selectable Nch open-drain output 0.35 ms typ. 2.43 V typ. (detection voltage)

- Ceramic capacitor compatible

- Ta =  $-40^{\circ}$ C to  $+125^{\circ}$ C

## Applications

- Secondary power supply for automotive equipment

- Camera module

- For automotive use (engine, transmission, suspension, ABS, related-devices for EV / HEV / PHEV, etc.)

- 1.75 A typ. (pulse-by-pulse method) Constant-voltage power supply for electrical application for vehicle interior

### Packages

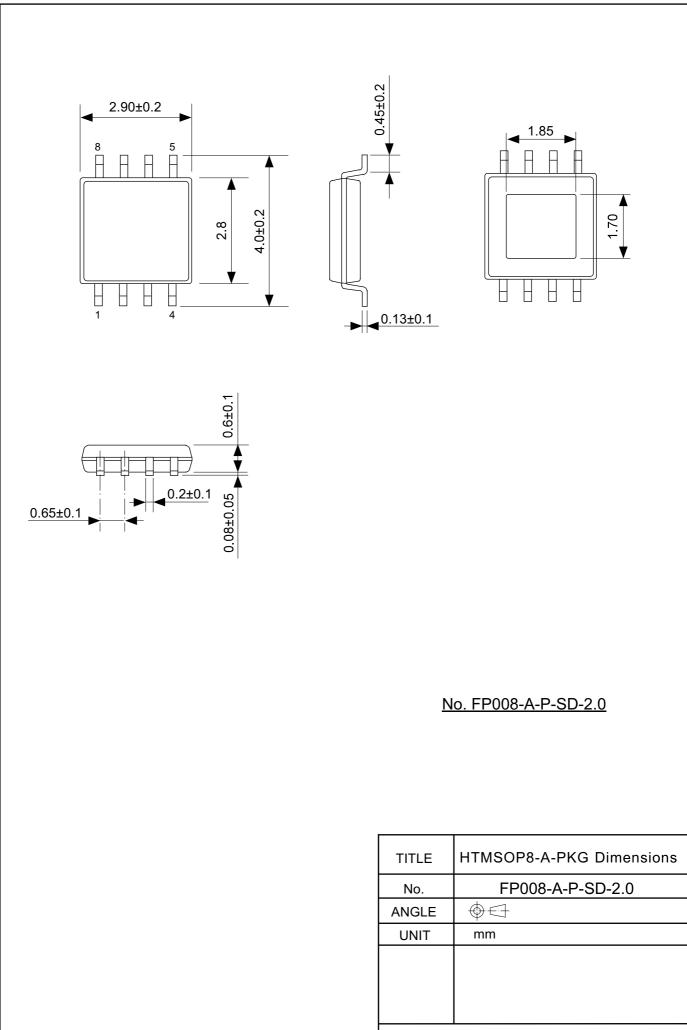

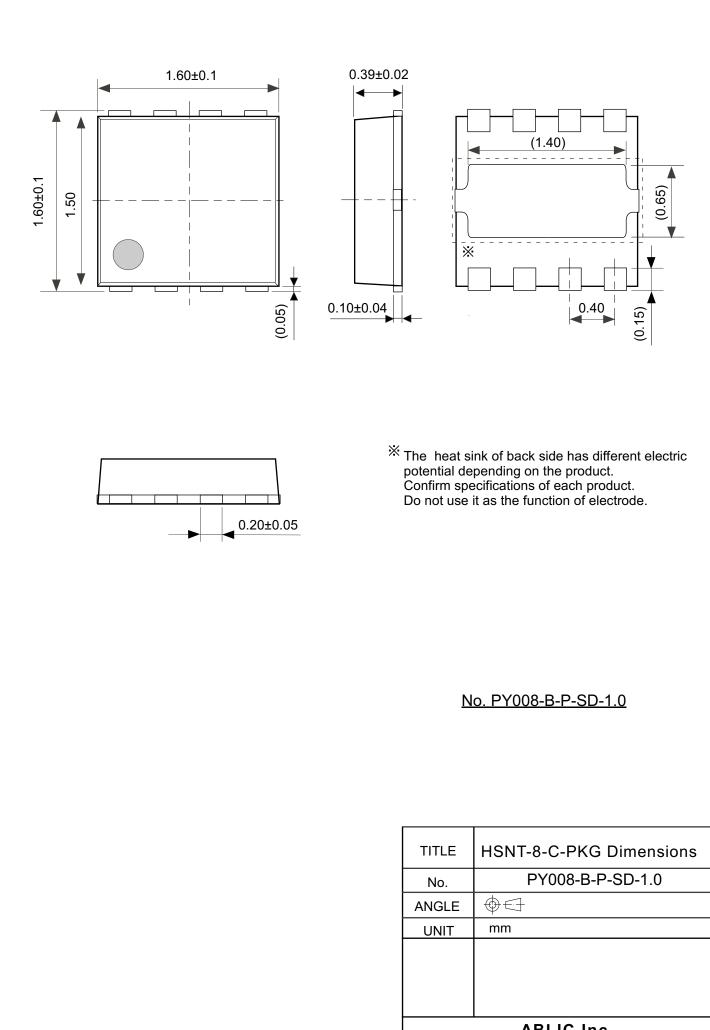

- HTMSOP-8  $(2.9 \text{ mm} \times 4.0 \text{ mm} \times t0.8 \text{ mm} \text{ max.})$ • HSNT-8(1616)B

- $(1.6 \text{ mm} \times 1.6 \text{ mm} \times t0.41 \text{ mm} \text{ max.})$

\*1. Contact our sales representatives for details.

## Typical Application Circuit

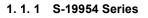

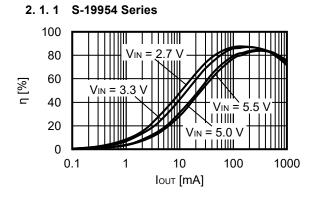

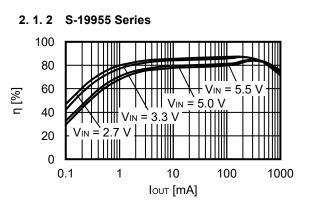

### Efficiency

ABLIC Inc.

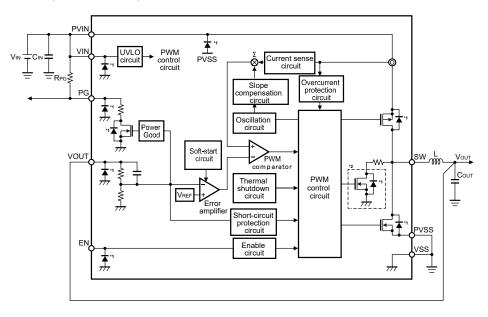

#### Block Diagrams

1. S-19954 Series (PWM control)

- \*1. Parasitic diode

- \*2. Discharge switch

Figure 1

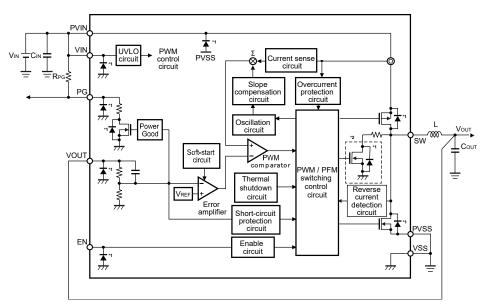

2. S-19955 Series (PWM / PFM switching control)

- \*1. Parasitic diode

- \*2. Discharge switch

Figure 2

### ■ AEC-Q100 Qualified

This IC supports AEC-Q100 for operation temperature grade 1. Contact our sales representatives for details of AEC-Q100 reliability specification.

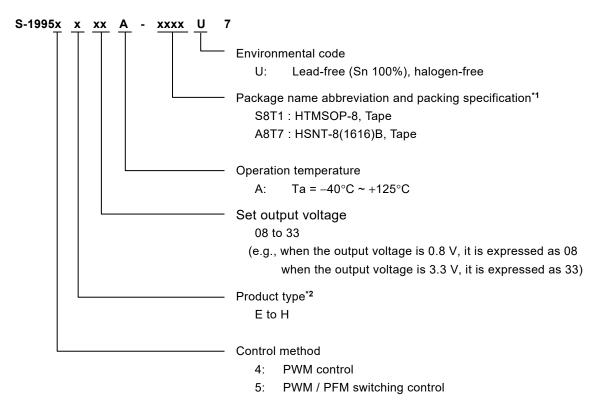

#### Product Name Structure

1. Product name

- \*1. Refer to the tape drawing.

- \*2. Refer to "2. Function list of product types".

#### 2. Function list of product types

| Table | 1 |

|-------|---|

|-------|---|

| Product Type | Oscillation Frequency | Output Discharge Function*1 | Short-circuit Protection Function |

|--------------|-----------------------|-----------------------------|-----------------------------------|

| E            | 2.25 MHz              | Available                   | Hiccup control                    |

| F            | 2.25 MHz              | Available                   | Latch control                     |

| G            | 2.25 MHz              | Unavailable                 | Hiccup control                    |

| Н            | 2.25 MHz              | Unavailable                 | Latch control                     |

\*1. Refer to "12. Output Discharge Function" in "

Operation"

#### 3. Packages

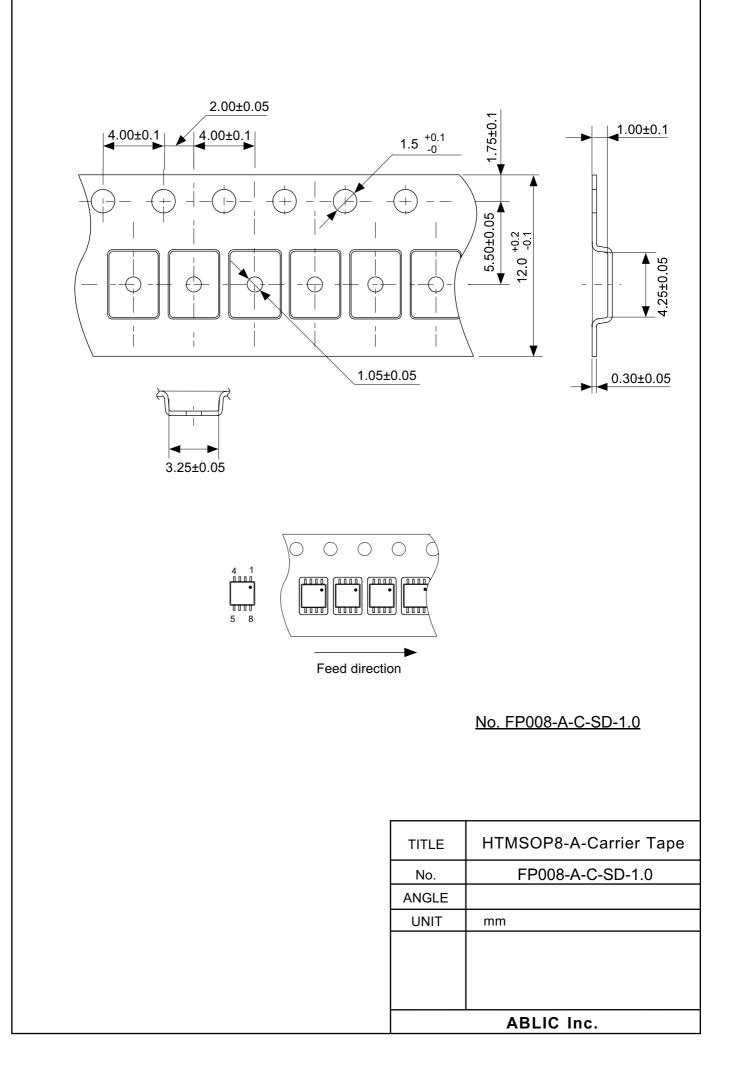

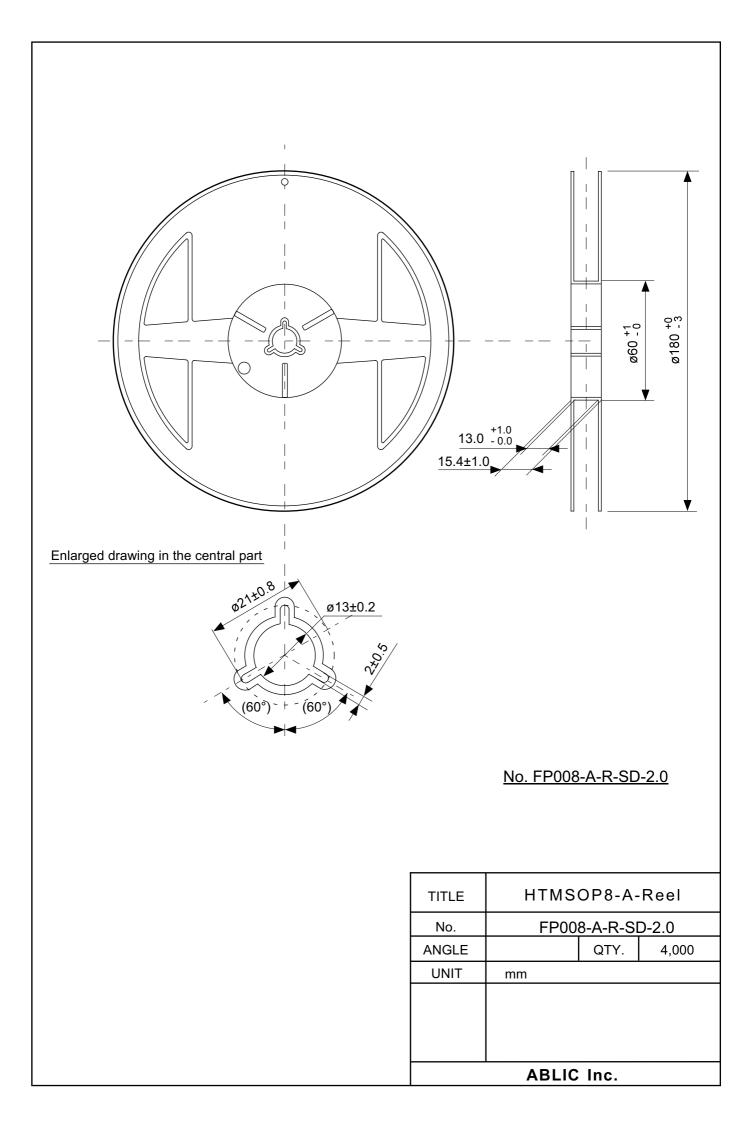

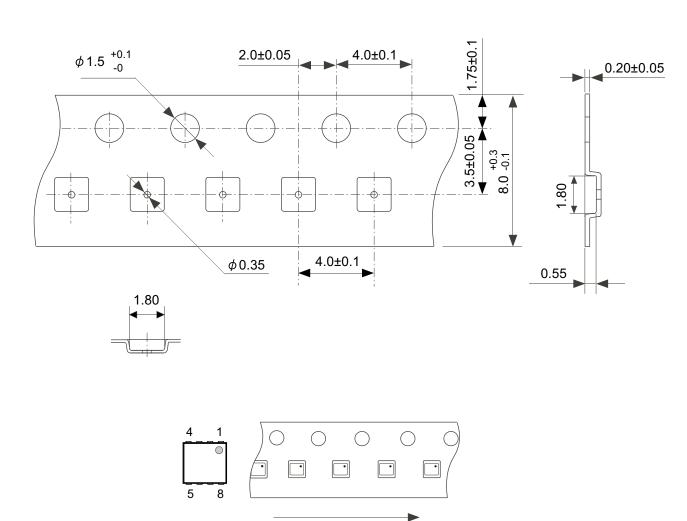

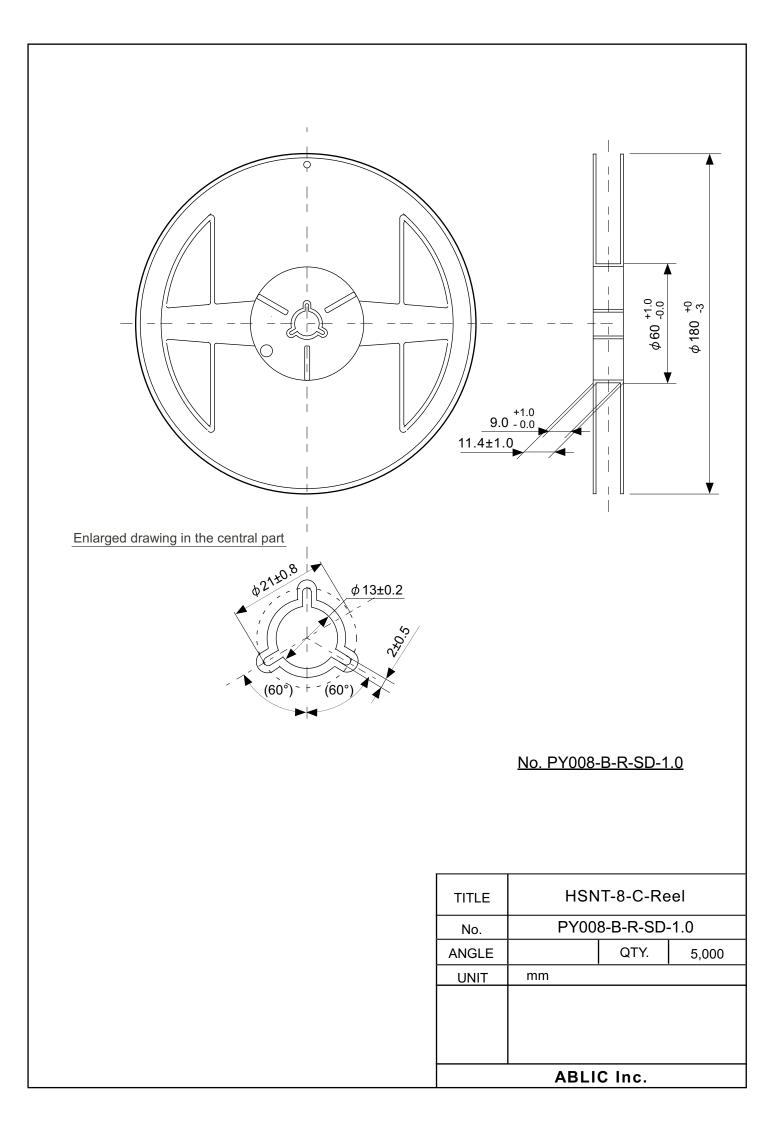

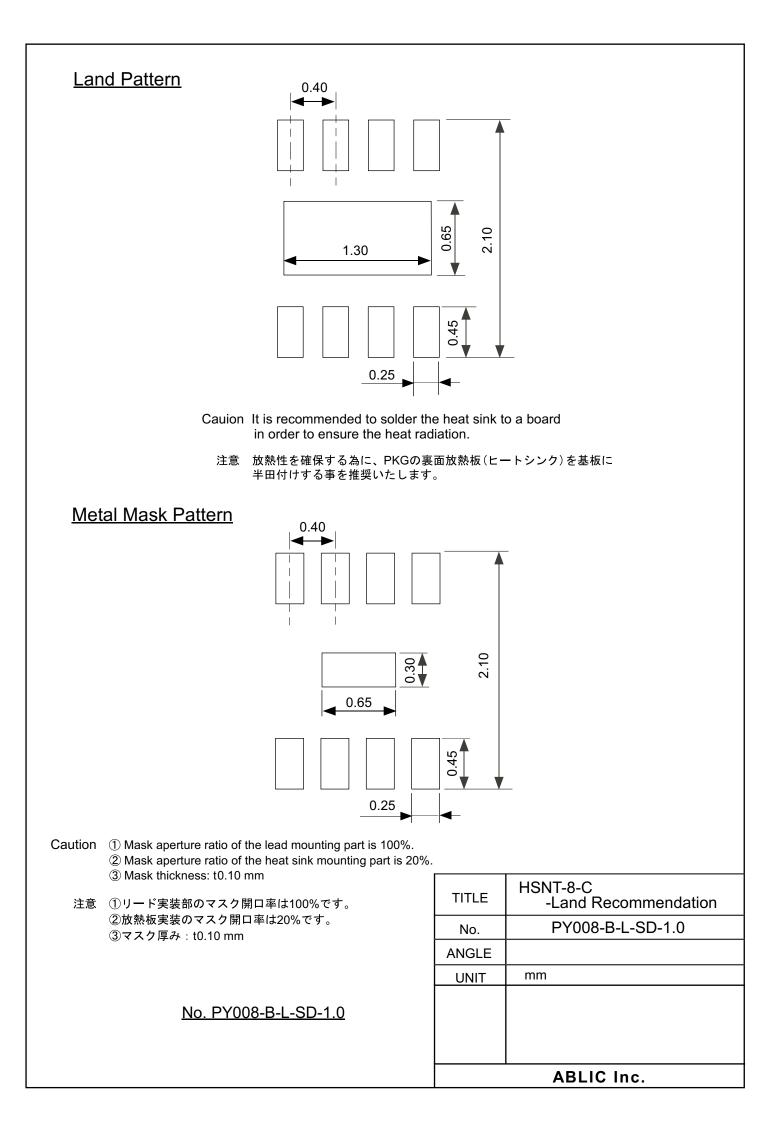

| Table 2 | Package | Drawing | Codes |

|---------|---------|---------|-------|

|---------|---------|---------|-------|

| Package Name  | Dimension    | Таре         | Reel         | Land         |

|---------------|--------------|--------------|--------------|--------------|

| HTMSOP-8      | FP008-A-P-SD | FP008-A-C-SD | FP008-A-R-SD | FP008-A-L-SD |

| HSNT-8(1616)B | PY008-B-P-SD | PY008-B-C-SD | PY008-B-R-SD | PY008-B-L-SD |

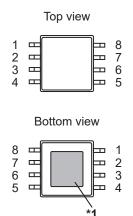

#### Pin Configurations

#### 1. HTMSOP-8

Figure 3

| Table 3 |                    |                                               |  |  |  |

|---------|--------------------|-----------------------------------------------|--|--|--|

| Pin No. | Symbol             | Description                                   |  |  |  |

| 1       | PVSS*2             | Power GND pin                                 |  |  |  |

| 2       | SW                 | External inductor connection pin              |  |  |  |

| 3       | VSS*2              | GND pin                                       |  |  |  |

| 4       | VOUT               | Output voltage monitor pin                    |  |  |  |

| 5       | PG <sup>*3</sup>   | Power Good output pin (Nch open-drain output) |  |  |  |

| 6       | EN <sup>*4</sup>   | Enable pin (active "H")                       |  |  |  |

| 7       | VIN <sup>*5</sup>  | Power supply pin (analog)                     |  |  |  |

| 8       | PVIN <sup>*5</sup> | Power supply pin (power)                      |  |  |  |

- \*1. Connect the heat sink of backside at shadowed area to the board, and set electric potential GND. However, do not use it as the function of electrode.

- \*2. Connect the PVSS and VSS pins to the board, and set electric potential GND.

- \*3. If the PG pin is unused, open it or connect to GND. If the PG pin is used, pull it up with a resistor.

- \*4. Do not float the EN pin. Pull it up to the VIN pin or connect to GND.

- \*5. Connect the VIN and PVIN pins on the board.

#### 2. HSNT-8(1616)B

| Table 4 |                                 |                                                                                                                                                                        |  |  |

|---------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin No. | Symbol                          | Description                                                                                                                                                            |  |  |

| 1       | PVSS*2                          | Power GND pin                                                                                                                                                          |  |  |

| 2       | SW                              | External inductor connection pin                                                                                                                                       |  |  |

| 3       | VSS*2                           | GND pin                                                                                                                                                                |  |  |

| 4       | VOUT                            | Output voltage monitor pin                                                                                                                                             |  |  |

| 5       | PG <sup>*3</sup>                | Power Good output pin (Nch open-drain output)                                                                                                                          |  |  |

| 6       | EN <sup>*4</sup>                | Enable pin (active "H")                                                                                                                                                |  |  |

| 7       | VIN <sup>*5</sup>               | Power supply pin (analog)                                                                                                                                              |  |  |

| 8       | PVIN <sup>*5</sup>              | Power supply pin (power)                                                                                                                                               |  |  |

|         | 1<br>2<br>3<br>4<br>5<br>6<br>7 | 1         PVSS*2           2         SW           3         VSS*2           4         VOUT           5         PG*3           6         EN*4           7         VIN*5 |  |  |

#### Figure 4

- \*1. Connect the heat sink of backside at shadowed area to the board, and set electric potential GND. However, do not use it as the function of electrode.

- \*2. Connect the PVSS and VSS pins to the board, and set electric potential GND.

- \*3. If the PG pin is unused, open it or connect to GND.

- If the PG pin is used, pull it up with a resistor.\*4. Do not float the EN pin.Pull it up to the VIN pin or connect to GND.

- **\*5.** Connect the VIN and PVIN pins on the board.

## ABLIC Inc.

...

## ■ Absolute Maximum Ratings

|                               | Tab<br>(Unless other) | rwise specified: Ta = +25°C, V <sub>SS</sub> = V <sub>PVSS</sub> = 0 V,                                                               | V <sub>IN</sub> = V <sub>F</sub> |

|-------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Item                          | Symbol                | Absolute Maximum Ratings                                                                                                              | Unit                             |

| VIN pin voltage               | VIN                   | $V_{SS} - 0.3$ to $V_{SS} + 6.5$                                                                                                      | V                                |

| EN pin voltage                | VEN                   | $V_{SS} - 0.3$ to $V_{SS} + 6.5$                                                                                                      | V                                |

| PG pin voltage                | Vpg                   | $V_{SS} - 0.3$ to $V_{SS} + 6.5$                                                                                                      | V                                |

| PVIN pin voltage              | VPVIN                 | $V_{SS} - 0.3$ to $V_{SS} + 6.5$                                                                                                      | V                                |

| VOUT pin voltage              | Vout                  | $V_{SS} - 0.3$ to $V_{SS} + 6.5$                                                                                                      | V                                |

| SW pin voltage                | Vsw                   | $\frac{V_{SS} - 0.3 \text{ to } V_{IN} + 0.3 \le V_{SS} + 6.5}{V_{SS} - 2 \text{ to } V_{IN} + 2 \le V_{SS} + 6.5 (< 20 \text{ ns})}$ | V                                |

| Junction temperature          | Tj                    | -40 to +150                                                                                                                           | °C                               |

| Operation ambient temperature | Topr                  | -40 to +125                                                                                                                           | °C                               |

| Storage temperature           | T <sub>stg</sub>      | -40 to +150                                                                                                                           | °C                               |

Caution The absolute maximum ratings are rated values exceeding which the product could suffer physical damage. These values must therefore not be exceeded under any conditions.

## ■ Thermal Resistance Value

| Table 6                                  |        |               |         |      |      |      |      |

|------------------------------------------|--------|---------------|---------|------|------|------|------|

| Item                                     | Symbol | Condit        | ion     | Min. | Тур. | Max. | Unit |

|                                          |        |               | Board A | _    | 159  | _    | °C/W |

|                                          |        |               | Board B | _    | 113  | -    | °C/W |

|                                          | ALθ    | HTMSOP-8      | Board C | -    | 39   | I    | °C/W |

|                                          |        |               | Board D | -    | 40   | I    | °C/W |

| 1                                        |        |               | Board E | -    | 30   | I    | °C/W |

| Junction-to-ambient thermal resistance*1 |        | HSNT-8(1616)B | Board A | -    | 214  | I    | °C/W |

|                                          |        |               | Board B | -    | 172  | I    | °C/W |

|                                          |        |               | Board C | -    | 52   | I    | °C/W |

|                                          |        |               | Board D | -    | 55   | I    | °C/W |

|                                          |        |               | Board E | _    | 43   | _    | °C/W |

\*1. Test environment: compliance with JEDEC STANDARD JESD51-2A

**Remark** Refer to "■ **Power Dissipation**" and "**Test Board**" for details.

### Recommended Operation Conditions

| Table 7                            |        |           |      |      |      |      |

|------------------------------------|--------|-----------|------|------|------|------|

| ltem                               | Symbol | Condition | Min. | Тур. | Max. | Unit |

| Output current                     | lout   | -         | _    | -    | 1    | А    |

| Effective output capacitance value | Соит   | -         | 5    | 10   | 20   | μF   |

| Effective inductance value         | L      | _         | 1.05 | 2.2  | 3.0  | μH   |

Remark Refer to Table 12 in "■ External Parts Selection" for details on recommended values.

Rev.1.3\_00

## Electrical Characteristics

Table 8

| Item                                        | Symbol              |                                                                                                                                       | Condition                                                                                                                                                              | Min.            | Тур.    | Max.                           | Unit |

|---------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------|--------------------------------|------|

| Operating input voltage                     | VIN                 | VIN = VPVIN                                                                                                                           |                                                                                                                                                                        | 2.7             | -       | 5.5                            | V    |

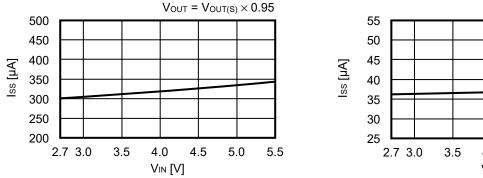

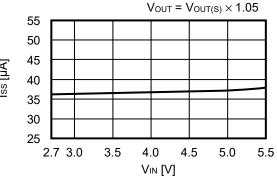

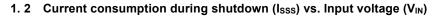

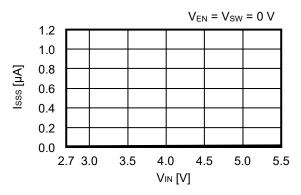

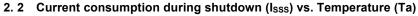

| Current consumption during shutdown         | lsss                | $V_{IN} = V_{PVIN} = 5.5$                                                                                                             | V*1, V <sub>EN</sub> = V <sub>SW</sub> = 0 V                                                                                                                           | -               | 0.1     | 18                             | μA   |

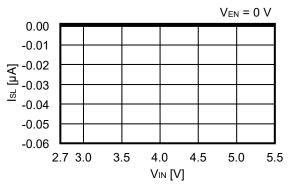

| Current consumption during                  |                     | S-19954 Series                                                                                                                        | $\label{eq:Vout} \begin{split} V_{\text{OUT}} &\leq V_{\text{OUT}(S)} \times 0.95, \\ \text{Power supply current}^{*1}, \\ V_{\text{EN}} &= 5.0 \text{ V} \end{split}$ | _               | 0.33    | -                              | mA   |

| switching off                               | lss                 | S-19955 Series                                                                                                                        | $V_{OUT} \ge V_{OUT(S)} \times 1.05$ ,<br>Power supply current <sup>*1</sup> ,<br>$V_{EN} = 5.0 V$                                                                     | _               | 38      | 80                             | μA   |

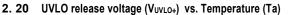

| UVLO detection voltage                      | VUVLO-              | V <sub>IN</sub> = V <sub>PVIN</sub> *1, fallii                                                                                        | ng                                                                                                                                                                     | 2.3             | 2.43    | 2.55                           | V    |

| UVLO release voltage                        | V <sub>UVLO+</sub>  | V <sub>IN</sub> = V <sub>PVIN</sub> *1, risir                                                                                         | Ig                                                                                                                                                                     | 2.4             | 2.53    | 2.65                           | V    |

| Maximum duty ratio                          | MaxDuty             |                                                                                                                                       | -                                                                                                                                                                      | 100             | -       | _                              | %    |

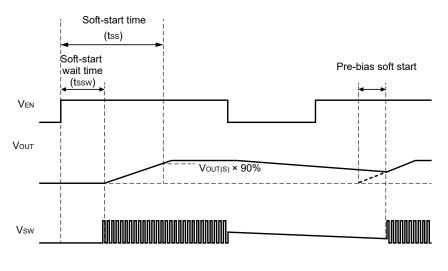

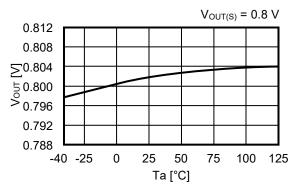

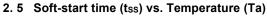

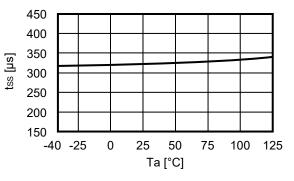

| Soft-start time                             | tss                 | Time after $V_{EN} = V_{OUT(S)}$                                                                                                      | $V_{SL} \rightarrow V_{SH}$ is applied until $V_{OUT}$ < 90% is reached                                                                                                | 0.18            | 0.35    | 0.65                           | ms   |

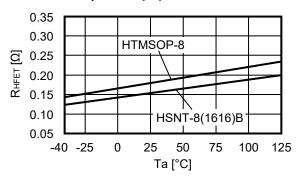

| High side power                             | Dura                | HTMSOP-8, Isw =                                                                                                                       | = 100 mA                                                                                                                                                               | _               | 0.17    | 0.275                          | Ω    |

| MOS FET on-resistance                       | Rhfet               | HSNT-8(1616)B,                                                                                                                        | Isw = 100 mA                                                                                                                                                           | -               | 0.155   | 0.25                           | Ω    |

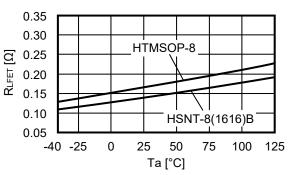

| Low side power                              | RLFET               | HTMSOP-8, Isw =                                                                                                                       | = –100 mA                                                                                                                                                              | _               | 0.13    | 0.245                          | Ω    |

| MOS FET on-resistance                       | INLFEI              | HSNT-8(1616)B,                                                                                                                        | I <sub>sw</sub> = -100 mA                                                                                                                                              | -               | 0.12    | 0.22                           | Ω    |

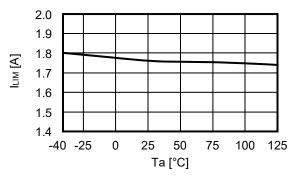

| Limit current                               | Ilim                |                                                                                                                                       | MOS FET peak current value                                                                                                                                             | 1.4             | 1.75    | 2.2                            | А    |

| High level input voltage                    | VsH                 | EN pin, V <sub>IN</sub> = 2.7                                                                                                         |                                                                                                                                                                        | 2.0             | -       | -                              | V    |

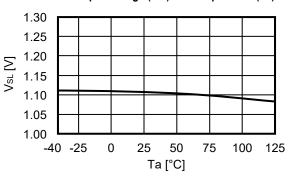

| Low level input voltage                     | Vsl                 | EN pin, V <sub>IN</sub> = 2.7                                                                                                         |                                                                                                                                                                        | -               | -       | 0.8                            | V    |

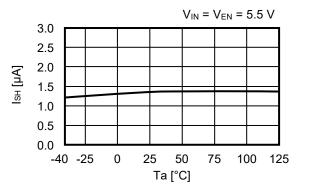

| High level input current                    | lsн                 |                                                                                                                                       | in = 5.5 V <sup>*1</sup> , V <sub>EN</sub> = Vin                                                                                                                       | 0.3             | 1.3     | 5                              | μA   |

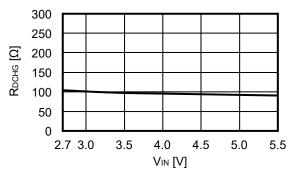

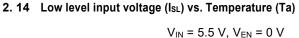

| Low level input current                     | Isl                 | EN pin, V <sub>IN</sub> = V <sub>PV</sub>                                                                                             | <sub>IN</sub> = 5.5 V <sup>*1</sup> , V <sub>EN</sub> = 0 V                                                                                                            | -0.1<br>Vout(s) | -       | 0.1                            | μA   |

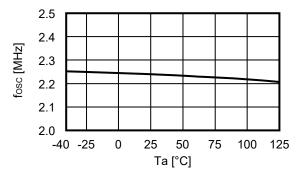

| Output voltage*2                            | Vout(e)             | During PWM operation, Iout = 1 mA                                                                                                     |                                                                                                                                                                        |                 | Vout(s) | V <sub>OUT(S)</sub><br>× 1.015 | V    |

| PWM operation oscillation<br>frequency      | fosc                |                                                                                                                                       | _                                                                                                                                                                      | 2.025           | 2.25    | 2.475                          | MHz  |

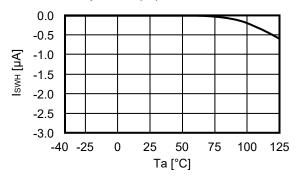

| SW pin leakage current "H"                  | lswн                | $V_{IN} = V_{PVIN} = 5.5 V^{*1}, V_{SW} = 0 V,$<br>High side power MOS FET OFF,<br>Low side power MOS FET OFF                         |                                                                                                                                                                        | -16             | -       | _                              | μΑ   |

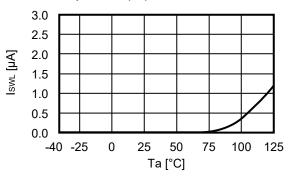

| SW pin leakage current "L"                  | I <sub>SWL</sub>    | $V_{IN} = V_{PVIN} = 5.5 V^{*1}, V_{SW} = 5.5 V,$<br>High side power MOS FET OFF, Low side power<br>MOS FET OFF, discharge switch OFF |                                                                                                                                                                        | -               | -       | 16                             | μA   |

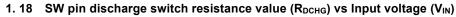

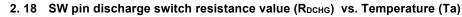

| SW pin discharge switch<br>resistance value | Rdchg               | Discharge switch                                                                                                                      | Discharge switch ON, $V_{IN} = V_{PVIN} = 5.5 V^{*1}$                                                                                                                  |                 | 95      | 200                            | Ω    |

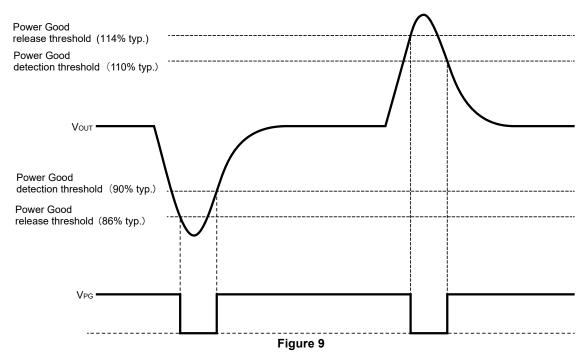

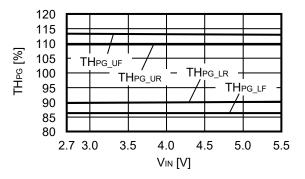

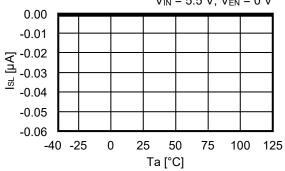

| Power Good detection                        | TH <sub>PG_UR</sub> | VOUT(E) ratio, VOUT falling                                                                                                           |                                                                                                                                                                        | _               | 110     | _                              | %    |

| threshold*3                                 | TH <sub>PG_LR</sub> | V <sub>OUT(E)</sub> ratio, VOUT rising                                                                                                |                                                                                                                                                                        | _               | 90      | _                              | %    |

| Power Good release                          | TH <sub>PG_UF</sub> | V <sub>OUT(E)</sub> ratio, VOUT rising                                                                                                |                                                                                                                                                                        | _               | 114     | _                              | %    |

| threshold*3                                 | TH <sub>PG_LF</sub> | V <sub>OUT(E)</sub> ratio, VOUT falling                                                                                               |                                                                                                                                                                        | _               | 86      | _                              | %    |

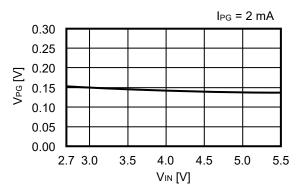

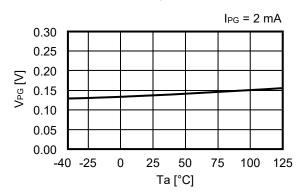

| PG pin low level voltage                    | Vpg                 | $V_{IN} = V_{PVIN} = 5.5$                                                                                                             | V <sup>*1</sup> , I <sub>PG</sub> = 2 mA                                                                                                                               | -               | _       | 0.4                            | V    |

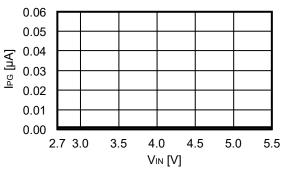

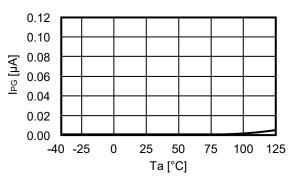

| PG pin leakage current                      | Ipg                 |                                                                                                                                       | _                                                                                                                                                                      | -               | _       | 1                              | μA   |

| Thermal shutdown detection temperature      | T <sub>SD</sub>     | Junction tempera                                                                                                                      | ture                                                                                                                                                                   | _               | 170     | _                              | °C   |

| Thermal shutdown release temperature        | T <sub>SR</sub>     | Junction tempera                                                                                                                      | ture                                                                                                                                                                   | _               | 145     | _                              | °C   |

$(V_{IN} = V_{PVIN} = 5.0 V^{*1}, T_i = -40^{\circ}C \text{ to } +125^{\circ}C \text{ unless otherwise specified})$

\*1. Short the VIN and PVIN pins on the board.

\*2. V<sub>OUT(S)</sub>: Set output voltage

V<sub>OUT(E)</sub>: Actual output voltage

\*3. When the soft start function is working, the Power Good function is disabled, and the PG pin is pulled down regardless of V<sub>OUT</sub>. When the soft start function operation ends, the Power Good function is enabled.

#### Operation

#### 1. Overview of operation

This IC adopts the current mode control. By comparing the current feedback signal which has slope compensation added to the current flows through the high side power MOS FET with the output signal of error amplifier, the duty ratio of the SW pin is determined. Using the negative feedback loop configured, the error amplifier output signal is maintained at the value that internal reference voltage  $V_{\text{REF}}$  and the feedback voltage from the VOUT pin will be equalized.

#### 2. PWM control (S-19954 Series)

The S-19954 Series operates with the pulse width modulation method (PWM) regardless of the extent of load current and allows the switching frequency to stabilize.

#### 3. PWM / PFM switching control (S-19955 Series)

The S-19955 Series automatically switches between PWM and pulse frequency modulation method (PFM) according to the load current. PFM control is selected when under light load, and the pulse will skip according to the load current. This reduces self-current consumption and improves efficiency when under light load.

In addition, our distinctive PWM / PFM switching control technology enables constant voltage output without generating excessive ripple voltage in  $V_{OUT}$  during PFM control. For PFM control, the output current value to be switched is set to  $I_{OUT}$  = 120 mA typ.

#### 4. 100% duty cycle operation

The high side power MOS FET allows for 100% duty cycle operation. Even when the input voltage ( $V_{IN}$ ) is lowered up to the output voltage ( $V_{OUT(E)}$ ), the high side power MOS FET is kept on and current can be supplied to the load. The output voltage at this time is the input voltage from which the voltage drop due to the DC resistance of the inductor and the on-resistance of the high side power MOS FET are subtracted.

If set output voltage  $(V_{OUT(S)})$  is high and  $V_{IN}$  is low, the short-circuit protection function may operate.

#### 5. Under voltage lockout function (UVLO)

This IC has a built-in UVLO circuit to prevent the IC from malfunctioning due to a transient status at power-on or a momentary drop in the supply voltage. When UVLO status is detected, the high side power MOS FET and the low side power MOS FET will turn off and switching operation will stop. The soft-start function is reset if UVLO status is detected once and is restarted by releasing the UVLO status.

Note that the internal circuits operate when UVLO status is detected, and the status is different from the disabled status. Also, there is a hysteresis width of approximately 0.1 V typ. for detection and release voltages to avoid malfunctions due to generation of noise, etc. in the input voltage.

#### 6. EN pin

This pin controls IC operation or stop. When the EN pin is set to "L", the operation of all internal circuits, including the high side power MOS FET, is stopped, reducing current consumption. If the output discharging function is available, the discharging switch connected to the SW pin works.

When not using the EN pin, connect it to the VIN pin. If the EN pin is open, it is pulled down to "L" level depending on the built-in current source.

| Table 9 |                           |  |  |  |

|---------|---------------------------|--|--|--|

| EN Pin  | Internal Circuit          |  |  |  |

| "H"     | Enable (normal operation) |  |  |  |

| "L"     | Disable (power off)       |  |  |  |

#### 7. Thermal shutdown function

This IC has a built-in thermal shutdown circuit to limit overheating. When the junction temperature increases to 170°C typ., the thermal shutdown circuit becomes the detection status, and the switching operation is stopped. When the junction temperature decreases to 145°C typ., the thermal shutdown circuit becomes the release status, and the switching operation is restarted. The detection temperature and release temperature have a hysteresis width of 25°C typ.

If the thermal shutdown circuit becomes the detection status due to self-heating, the switching operation is stopped and output voltage ( $V_{OUT}$ ) decreases. For this reason, the self-heating is limited and the temperature of the IC decreases. The thermal shutdown circuit becomes release status when the temperature of the IC decreases, and the switching operation is restarted, thus the self-heating is generated again. Repeating this procedure makes the waveform of  $V_{OUT}$  into a pulse-like form. Note that the product may suffer physical damage such as deterioration if the above phenomenon occurs continuously. Consider usage conditions carefully. Switching operation stop and restart can be suppressed by either setting the EN pin to "L", lowering the output current ( $I_{OUT}$ ) to reduce internal power consumption, or decreasing the ambient temperature.

Since the thermal shutdown circuit is in detection state and the internal circuits are working, it is different from disable status.

If the junction temperature is not equal to or lower than the release temperature when the IC starts, switching operation stops until the junction temperature becomes equal to or lower than the release temperature.

| Thermal Shutdown Circuit | Vout                         | Output Discharge Switch |  |  |  |  |  |

|--------------------------|------------------------------|-------------------------|--|--|--|--|--|

| Release: 145°C typ.*1    | Constant value <sup>*2</sup> | OFF                     |  |  |  |  |  |

| Detection: 170°C typ.*1  | Pulled down to Vss*3         | ON                      |  |  |  |  |  |

Table 10

**\*1.** Junction temperature

**\*2.** A constant value is output due to regulating operation based on the internal resistance.

\*3.  $V_{OUT}$  is pulled down to  $V_{SS}$  due to the VOUT pin resistance and a load.

# Caution If the heat dissipation of the application is not good, self-heating cannot be restricted immediately, and the IC may be destroyed. The actual application should be evaluated carefully to verify that there is no problem.

#### 8. Overcurrent protection function

This IC has a built-in overcurrent protection circuit to prevent IC destruction due to overload or magnetic saturation of an inductor. The overcurrent protection circuit performs pulse-by-pulse overcurrent protection that monitors the current of the high-side power MOS FET for each cycle of switching operation.

When a current reaching or exceeding the limit current ( $I_{LIM}$ ) flows through the high side power MOS FET, the high side power MOS FET is turned off. When the next switching cycle starts, the high side power MOS FET is turned on. If the current value continues to remain at  $I_{LIM}$  or higher, the high side power MOS FET is turned off again, repeating this series of operation.

Meanwhile, when the current, which flows through the high side power MOS FET, falls to I<sub>LIM</sub> or lower, this IC will return to the normal operation.

When the slope of inductor current is large,  $I_{LIM}$  may appear to increase due to the delay time of overcurrent protection circuit. This phenomenon tends to occur when low-inductance inductor is used or when the voltage difference between  $V_{IN}$  and  $V_{OUT}$  is large.

#### 9. Frequency foldback function

The frequency foldback function reduces the oscillation frequency in proportion to  $V_{OUT}$  when VOUT pin voltage is  $V_{OUT(E)} \times 0.8$  V typ. or lower. Refer to "10. Short-circuit protection function" for details.

The frequency foldback function in this IC sets to invalid when the soft-start function is operating. If the VOUT pin voltage is equal to or greater than  $V_{OUT(E)} \times 0.84$  V typ., the IC works at the PWM operation oscillation frequency (f<sub>OSC</sub>). If the output current increases when there is a little difference between the input and output voltages, a voltage drop occurs due to ON resistance of the high-side power MOS FET, and the VOUT pin voltage may be equal to or less than the frequency foldback detection threshold.

#### 10. Short-circuit protection function

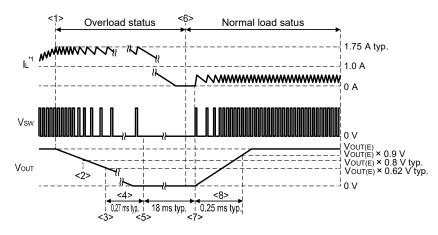

#### 10.1 Hiccup control

E, G type of this IC has a built-in short-circuit protection function for Hiccup control.

The hiccup control is a method for periodically carrying out automatic recovery when the IC detects overcurrent and stops the switching operation.

#### 10. 1. 1 When overload status is released

- <1> Overcurrent detection

- <2> After detection of the VOUT pin voltage (V<sub>OUT</sub>) < V<sub>OUT(E)</sub> × 0.8 V typ., frequency foldback function becomes valid.

- <3> Detection of  $V_{OUT} < V_{OUT(E)} \times 0.62$  V typ.

- <4> 0.27 ms elapse

- <5> Switching operation stop (for 18 ms typ.) (short-circuit protection detection status)

- <6> Overload status release

- <7> The IC restarts, soft-start function starts.

- In this case, it is unnecessary to input an external reset signal for restart.

- <8> V<sub>OUT</sub> reaches  $V_{OUT(E)} \times 0.9$  V typ. after 0.25 ms typ. elapses.

\*1. Inductor current

Figure 5

#### Rev.1.3\_00

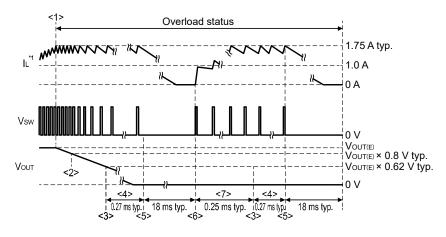

#### 10. 1. 2 When overload status continues

- <1> Overcurrent detection

- <2> After detection of V<sub>OUT</sub> < V<sub>OUT(E)</sub> × 0.8 V typ, frequency foldback function becomes valid.

- <3> Detection of V<sub>OUT</sub> < V<sub>OUT(E)</sub> × 0.62 V typ.

- <4> 0.27 ms elapse

- <5> Switching operation stop (for 18 ms typ.) (short-circuit protection detection status)

- <6> The IC restarts, soft-start function starts.

- <7> The status returns to <3> when overload status continues after 0.25 ms typ. elapses.

\*1. Inductor current

Figure 6

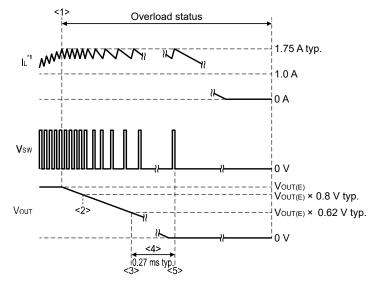

#### 10.2 Latch control

F, H type of this IC has a built-in short-circuit protection function for Latch control.

The latch control is a method for maintaining the Latch status when the IC detects overcurrent and stops the switching operation.

- <1> Overcurrent detection

- <2> After detection of V<sub>OUT</sub> < V<sub>OUT(E)</sub> × 0.8 V typ., frequency foldback function becomes valid.

- <3> Detection of  $V_{OUT} < V_{OUT(E)} \times 0.62$  V typ.

- <4> 0.27 ms elapse

- <5> Switching operation stop (short-circuit protection detection status)

\*1. Inductor current

In addition, Latch status is reset under the following conditions.

- At UVLO detection

- When the EN pin changes from "H" to "L".

#### 11. Pre-bias compatible soft-start function

This IC has a built-in pre-bias compatible soft-start circuit.

If the pre-bias compatible soft-start circuit starts when electrical charge remains in the output voltage ( $V_{OUT}$ ) because of power supply restart, etc., or when  $V_{OUT}$  is biased beforehand (pre-bias status), switching operation is stopped until the internal soft-start voltage exceeds the feedback voltage from VOUT pin, and then  $V_{OUT}$  is maintained. If the softstart voltage exceeds the feedback voltage from VOUT pin, switching operation will restart and  $V_{OUT}$  will rise to the output voltage setting value ( $V_{OUT(S)}$ ). This allows  $V_{OUT(S)}$  to be reached without lowering the pre-biased  $V_{OUT}$ . In soft-start circuits which are not pre-bias compatible, a large current flows as a result of the discharge of the residual electric charge in  $C_{OUT}$  through the low side power MOS FET when switching operation starts, which could cause damage to the IC, however in a pre-bias compatible soft-start circuit, the IC is protected from the large current when switching operation starts, and it makes power supply design for the application circuit simpler.

In this IC,  $V_{OUT}$  reaches  $V_{OUT(S)}$  gradually due to the soft-start circuit. In the following cases, rush current and  $V_{OUT}$  overshoot are reduced.

- When the EN pin changes from "L" to "H".

- When UVLO operation is released\*1.

- When thermal shutdown is released<sup>\*1</sup>.

- When recovering from Short-circuit protection detection status\*1.

\*1. In this case, the soft-start wait time is eliminated.

The soft-start circuit starts operating after "H" is input to the EN pin and the soft-start wait time ( $t_{SSW}$ ) = 0.08 ms typ. elapses. The time after V<sub>OUT</sub> starts rising until V<sub>OUT(S)</sub> × 90% is reached is set internally to 0.25 ms typ.

Figure 8

#### 12. Output discharge function

The ICs of type E and F have an output discharging function to discharge output capacitor  $C_{OUT}$ . When the EN pin = "L", the 95  $\Omega$  typ. output discharging switch connected to the SW pin turns on and discharges  $C_{OUT}$ .

#### 13. Power Good function

This IC has the Power Good function for Nch open drain output to monitor output voltage (Vout).

If  $V_{OUT}$  is within the Power Good detection threshold, the Nch transistor at the PG pin turns off and outputs "H". If  $V_{OUT}$  deviates from the Power Good release threshold, the Nch transistor at the PG pin turns on, the PG pin is pulled down, and outputs "L".

Also, the PG pin is pulled down and "L" is output in the following cases.

- The EN pin is at "L" level

- UVLO is detected

- Thermal shutdown is detected

- Soft start operates

If "L" is output, it is pulled down with 70  $\Omega$  typ., and when it is pulled up with a power supply, the pull-up resistance is about 3 k $\Omega$  to 100 k $\Omega$ . The detection threshold and the release threshold have a hysteresis width of 4% typ. The Power Good response time has a 10  $\mu$ s typ. response delay time for both detection and release.

The PG pin is pulled up with an external resistor, but the application voltage must not exceed the absolute maximum rating. If Power Good output is not used, connect it to open or GND.

Sequence operations can be performed by connecting the PG pin to the EN pin of other S-19952/19953 Series, S-19954/19955 Series.

| Table 11 |

|----------|

|----------|

|                                          | Power Good output                                                         |              |

|------------------------------------------|---------------------------------------------------------------------------|--------------|

|                                          | Vout ≥ Vout(E) × THPG_UF (114% typ.), Vout rising                         | "L"          |

| During operation ( $V_{EN} \ge V_{SH}$ ) | Vout ≤ Vout(E) × THPg_ur(110% typ.), Vout falling                         | "H" (High-Z) |

|                                          | $V_{OUT} \ge V_{OUT(E)} \times TH_{PG_{LR}}$ (90% typ.), $V_{OUT}$ rising | "H" (High-Z) |

|                                          | Vouт ≤ Vouт(E) × THPG_LF (86% typ.), Vou⊤ falling                         | "L"          |

| During shutdown operation                | V <sub>EN</sub> < V <sub>SL</sub>                                         | "L"          |

| During UVLO detection.                   | Vin < Vuvlo-                                                              | "L"          |

| During thermal shutdown detection        | $T_{SD} < T_j$                                                            | "L"          |

| During soft start operation              |                                                                           | "L"          |

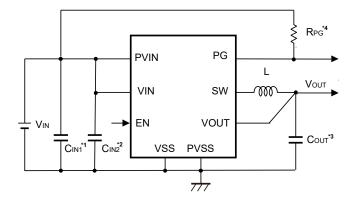

## Typical Circuit

\*1.  $C_{IN1}$  is a capacitor for stabilizing the input. If  $C_{IN2}$  is not used, connect  $C_{IN1}$  as close to the IC as possible.

- \*2.  $C_{IN2}$  is a capacitor for stabilizing the input. If the operation is unstable, connect the decoupling capacitor  $C_{IN2}$  close to the IC and connect  $C_{IN1}$  in parallel with  $C_{IN2}$ .

- \*3. COUT is a capacitor for stabilizing the output.

- \*4. R<sub>PG</sub> is a Power Good pull-up resistor. If the PG pin is unused, connect it to open or GND.

#### Figure 10

Caution The above connection diagram will not guarantee successful operation. Perform thorough evaluation using an actual application to set the constants.

#### External Parts Selection

The recommended values for each external part are shown in **Table 12**, and the recommended parts are shown in **Table 13** to **Table 16**.

When selecting an input capacitor  $(C_{IN1}, C_{IN2})$  and output capacitor  $(C_{OUT})$ , take into consideration the temperature range and DC current superposition characteristics to be used.

When selecting an inductor (L), take into consideration the temperature range, DC current superposition characteristics and the rated current value of the inductor to be used.

|                     |                | Table 12 |        |       |        |

|---------------------|----------------|----------|--------|-------|--------|

| Input voltage range | Vout           | CIN1     | CIN2   | Соит  | L      |

|                     | 0.8 V to 1.2 V | 10 μF    | 0.1 μF | 10 μF | 1.5 μH |

| 2.7 V to 5.5 V      | 0.8 V to 3.3 V | 10 μF    | 0.1 μF | 10 μF | 2.2 μH |

| 2.7 V to 3.6 V      | 0.8 V to 1.8 V | 10 μF    | 0.1 μF | 10 μF | 1.5 μH |

| Table 13 Recommended Capacitors (CIN1) List |                      |             |                         |                                                                |  |

|---------------------------------------------|----------------------|-------------|-------------------------|----------------------------------------------------------------|--|

| Manufacturer                                | Part Number          | Capacitance | Withstanding<br>Voltage | Dimensions (L $\times$ W $\times$ H)                           |  |

| TDK Corporation                             | CGA4J1X7S1C106K125AC | 10 μF       | 16 V                    | $2.0 \text{ mm} \times 1.25 \text{ mm} \times 1.25 \text{ mm}$ |  |

| TDK Corporation                             | CGA4J3X7S1A106K125AB | 10 μF       | 10 V                    | $2.0 \text{ mm} \times 1.25 \text{ mm} \times 1.25 \text{ mm}$ |  |

| Murata Manufacturing Co., Ltd.              | GCM21BC71C106KE36#   | 10 μF       | 16 V                    | $2.0~\text{mm}\times1.25~\text{mm}\times1.25~\text{mm}$        |  |

#### Table 14 Recommended Capacitors (CIN2) List

| Manufacturer    | Part Number          | Capacitance | Withstanding<br>Voltage | Dimensions (L $\times$ W $\times$ H)   |

|-----------------|----------------------|-------------|-------------------------|----------------------------------------|

| TDK Corporation | CGA2B1X7R1C104K050BC | 0.1 μF      | 16 V                    | 1.0 mm $\times$ 0.5 mm $\times$ 0.5 mm |

#### Table 15 Recommended Capacitors (Cout) List

| Manufacturer                   | Part Number          | Capacitance | Withstanding<br>Voltage | Dimensions (L $\times$ W $\times$ H)                           |

|--------------------------------|----------------------|-------------|-------------------------|----------------------------------------------------------------|

| TDK Corporation                | CGA4J1X7S1C106K125AC | 10 μF       | 16 V                    | $2.0~\text{mm}\times1.25~\text{mm}\times1.25~\text{mm}$        |

| TDK Corporation                | CGA4J3X7S1A106K125AB | 10 μF       | 10 V                    | $2.0 \text{ mm} \times 1.25 \text{ mm} \times 1.25 \text{ mm}$ |

| Murata Manufacturing Co., Ltd. | GCM21BC71C106KE36#   | 10 μF       | 16 V                    | 2.0 mm $\times$ 1.25 mm $\times$ 1.25 mm                       |

| TDK Corporation                | CGA3E1X7T0J106M080AC | 10 μF       | 6.3 V                   | 1.6 mm $\times$ 0.8 mm $\times$ 0.8 mm                         |

| Murata Manufacturing Co., Ltd. | GCM188D70J106ME36#   | 10 μF       | 6.3 V                   | 1.6 mm $\times$ 0.8 mm $\times$ 0.8 mm                         |

#### Table 16 Recommended Inductors (L) List

| Manufacturer                   | Part Number          | Inductance | Temperature<br>Range | Dimensions (L $\times$ W $\times$ H)                         |

|--------------------------------|----------------------|------------|----------------------|--------------------------------------------------------------|

| TDK Corporation                | TFM201610ALMA1R5MTAA | 1.5 μH     | –55°C to 150°C       | $2.0 \text{ mm} \times 1.6 \text{ mm} \times 1.0 \text{ mm}$ |

| TDK Corporation                | TFM252012ALMA1R5MTAA | 1.5 μH     | –55°C to 150°C       | $2.5 \text{ mm} \times 2.0 \text{ mm} \times 1.2 \text{ mm}$ |

| Murata Manufacturing Co., Ltd. | DFE2MCAH1R5MJ0#      | 1.5 μΗ     | –40°C to 150°C       | 2.5 mm $\times$ 2.0 mm $\times$ 1.2 mm                       |

| TDK Corporation                | TFM252012ALMA2R2MTAA | 2.2 μH     | –55°C to 150°C       | $2.5 \text{ mm} \times 2.0 \text{ mm} \times 1.2 \text{ mm}$ |

| TDK Corporation                | TFM201610ALMA2R2MTAA | 2.2 μH     | –55°C to 150°C       | $2.0 \text{ mm} \times 1.6 \text{ mm} \times 1.0 \text{ mm}$ |

#### 1. Input capacitor (C<sub>IN1</sub>, C<sub>IN2</sub>)

$C_{IN1}$  is a capacitor for stabilizing the input. It has an effect to suppress the ripple voltage and switching noise to be generated in the power supply line. Ceramic capacitor with 10  $\mu$ F or higher is recommended. Connecting a decoupling capacitor  $C_{IN2}$  close to the IC and connecting  $C_{IN1}$  in parallel with  $C_{IN2}$  is effective in stabilizing operation. If  $C_{IN2}$  is not used, connect  $C_{IN1}$  close to the IC. When selecting a capacitor, take into consideration the temperature range and DC current superposition characteristics.

#### 2. Output capacitor (COUT)

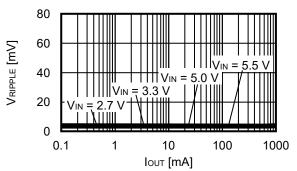

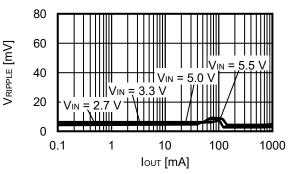

$C_{OUT}$  is used to smooth output voltage. The ripple voltage (V<sub>RIPPLE</sub>) to be generated in V<sub>OUT</sub> is inversely proportional to C<sub>OUT</sub>. When selecting a capacitor whose ESR is sufficiently small, V<sub>RIPPLE</sub> during current continuous mode is calculated by the following expression. When selecting a capacitor, take into consideration the temperature range and DC current superposition characteristics.

$$V_{\text{RIPPLE}} = \frac{\Delta I_{\text{L}}}{8 \times \text{fosc} \times \text{Cout}}$$

In addition, since  $C_{OUT}$  contributes to the stability of feedback loop, a ceramic capacitor with 10  $\mu$ F or higher is recommended. When selecting a capacitor whose capacitance is extremely large, the overcurrent protection function may start the operation and cause a start-up failure.

#### 3. Inductor (L)

To suppress the intrinsic subharmonic oscillation in current mode control, the optimal L value needs to be selected. Considering the slope compensation in the IC, select an inductor from the range of 1.5  $\mu$ H to 2.2  $\mu$ H depending on input voltage range and V<sub>OUT</sub>. When selecting a capacitor, take into consideration DC current superposition characteristics, and operating temperature range, including self rising in temperature.

When selecting L, note the rated current. If a current exceeding the rated current flows through the inductor, magnetic saturation may occur, and there may be risks which substantially lower efficiency and damage the IC as a result of large current.

The ripple current ( $\Delta I_L$ ) and peak current ( $I_{PK}$ ) flow through the inductor during current continuous mode are calculated by the following expressions respectively.  $\Delta I_L$  is generally set to approximately 30% of the maximum output current. Make sure  $I_{PK}$  will not exceed the rated current of inductor.

$$\Delta I_{L} = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{f_{OSC} \times L \times V_{IN}}$$

$$I_{PK} = I_{OUT} + \frac{\Delta I_L}{2}$$

To maintain the rated current of an inductor even in cases  $V_{OUT}$  shorts to  $V_{SS}$  or other fault conditions occur, the inductor with the rated current, the maximum value of limit current ( $I_{LIM}$ ) or higher, needs to be selected.

## Caution Switching regulators generally oscillate depending on selection of external parts. The characteristics of external parts, including temperature characteristics, should be evaluated carefully in actual applications to verify that they do not oscillate.

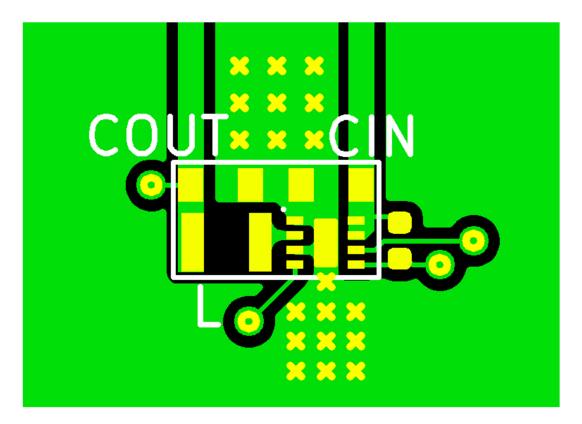

### Board Layout Guidelines

Note the following cautions when determining the board layout for this IC.

- Place C<sub>IN</sub> as close to the VIN pin and the VSS pin as possible. Prioritize the layout of C<sub>IN</sub>.

- Mount C<sub>IN</sub> on the same surface layer as the IC. If they are connected through thermal vias, the impedance of the thermal vias may influence the operation, resulting in unstable condition.

- Connecting a decoupling capacitor C<sub>IN2</sub> close to the IC and connecting C<sub>IN1</sub> in parallel with C<sub>IN2</sub> is effective in stabilizing operation. If C<sub>IN2</sub> is not used, connect C<sub>IN1</sub> close to the IC.

- Do not place the VOUT pin close to noise sources such as the wiring of SW pin to avoid unstable operations.

- The VOUT pin wire may be surrounded by a GND pattern.

- Connect PVSS and VSS pins with a GND pattern on the surface layer.

- Make the GND pattern as wide as possible.

- Place thermal vias in the GND pattern to ensure sufficient heat dissipation.

- Large current flows through the SW pin. Make the wiring area of the pattern to be connected to the SW pin small to minimize parasitic capacitance and emission noise.

- Make a short loop wiring of the SW pin  $\rightarrow$  L  $\rightarrow$  C<sub>OUT</sub>  $\rightarrow$  PVSS and VSS pins. This is effective to reduce emission noise.

- Do not wire the SW pin pattern under the IC.

- As much as possible, do not draw a pattern directly under the inductor (L), including the surface layer and the back layer.

Total size 5.5 mm  $\times$  3.1 mm = 17.05 mm<sup>2</sup>

#### Figure 11 Reference Board Pattern

Caution The above pattern diagram does not guarantee successful operation. Perform thorough evaluation using the actual application to determine the pattern.

**Remark** Power Good pull-up resistor (R<sub>PG</sub>) is optional.

#### Precautions

- Mount external capacitors and inductors as close as possible to the IC, and make single GND.

- Characteristic ripple voltage and spike noise occur in the IC containing switching regulators. Moreover rush current flows at the time of a power supply injection. Because these largely depend on the inductor, the capacitor and impedance of power supply to be used, fully check them using an actually mounted model.

- C<sub>IN</sub> connected between the PVIN (VIN) pin and the PVSS (VSS) pin is a bypass capacitor (refer to **"■ Typical Circuit**"). It stabilizes the power supply in the IC, and thus effectively works for stable switching regulator operation. Allocate the bypass capacitor as close to the IC as possible, prioritized over other parts.

- Connecting a decoupling capacitor C<sub>IN2</sub> close to the IC and connecting C<sub>IN1</sub> in parallel with C<sub>IN2</sub> is effective in stabilizing operation. If C<sub>IN2</sub> is not used, connect C<sub>IN1</sub> close to the IC.

- Although the IC contains a static electricity protection circuit, static electricity or voltage that exceeds the limit of the

protection circuit should not be applied.

- The power dissipation of the IC greatly varies depending on the size and material of the board to be connected. Perform sufficient evaluation using an actual application before designing.

- ABLIC Inc. assumes no responsibility for the way in which this IC is used on products created using this IC or for the specifications of that product, nor does ABLIC Inc. assume any responsibility for any infringement of patents or copyrights by products that include this IC either in Japan or in other countries.

#### Characteristics (Typical Data)

#### 1. Example of major power supply dependence characteristics (Ta = +25°C)

1.1 Current consumption during switching off (Iss) vs. Input voltage (VIN)

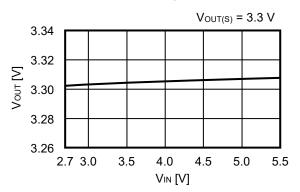

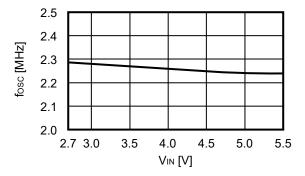

1. 3 VOUT detection voltage (Vout) vs. Input voltage (VIN)

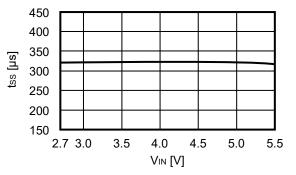

1. 5 Soft-start time (tss) vs. Input voltage (VIN)

ABLIC Inc.

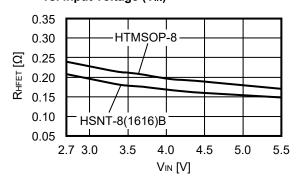

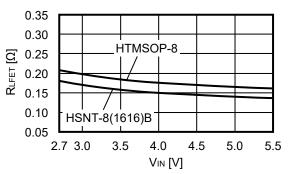

1. 6 High side power MOS FET on-resistance (R<sub>HFET</sub>) 1. 7 vs. Input voltage (V<sub>IN</sub>)

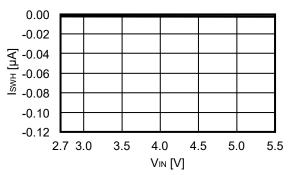

1.8 SW pin leakage current "H" (I<sub>SWH</sub>) vs. Input voltage (V<sub>IN</sub>)

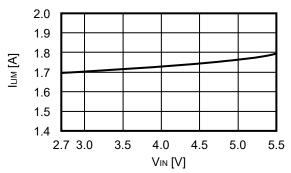

1. 10 Limit current (ILIM) vs. Input voltage (VIN)

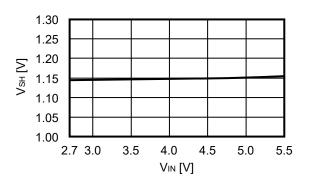

1. 11 High level input voltage (V<sub>SH</sub>) vs. Input voltage (V<sub>IN</sub>)

7 Low side power MOS FET on-resistance (R<sub>LFET</sub>) vs. Input voltage (V<sub>IN</sub>)

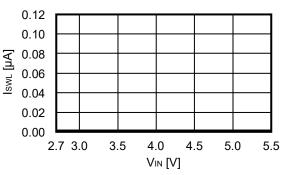

1.9 SW pin leakage current "L" (I<sub>SWL</sub>) vs. Input voltage (V<sub>IN</sub>)

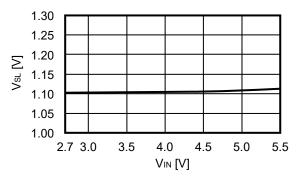

1. 12 Low level input voltage (VSL) vs. Input voltage (VIN)

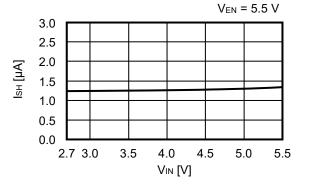

#### 1. 13 High level input current (IsH) vs Input voltage (VIN)

1. 15 Power Good threshold (TH<sub>PG</sub>) vs Input voltage (V<sub>IN</sub>)

1. 16 PG pin low level voltage (VPG) vs Input voltage (VIN)

1. 17 PG pin leakage current ( $I_{PG}$ ) vs Input voltage (V<sub>IN</sub>)

1. 14 Low level input current (IsL) vs Input voltage (VIN)

Rev.1.3\_00

#### 2. Example of major temperature characteristics (Ta = −40°C to +125°C, V<sub>IN</sub> = 5.0 V)

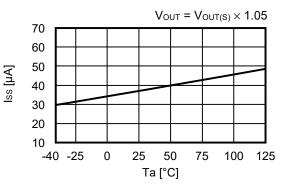

2.1 Current consumption during switching off (Iss) vs. Temperature (Ta)

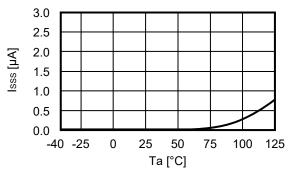

2. 3 VOUT detection voltage (Vout) vs. Temperature (Ta)

2. 6 High side power MOS FET on-resistance (R<sub>HFET</sub>) vs. Temperature (Ta)

2.8 High side power MOS FET leakage current (I<sub>SWH</sub>) vs. Temperature (Ta)

2. 10 Limit current (ILIM) vs. Temperature (Ta)

2. 11 High level input voltage (V<sub>SH</sub>) vs. Temperature (Ta)

2. 7 Low side power MOS FET on-resistance (R<sub>LFET</sub>) vs. Temperature (Ta)

2.9 Low side power MOS FET leakage current (I<sub>SWL</sub>) vs. Temperature (Ta)

2. 12 Low level input voltage (V<sub>SL</sub>) vs. Temperature (Ta)

#### 2. 13 High level input current (I<sub>SH</sub>) vs. Temperature (Ta)

2. 15 Power Good threshold (TH<sub>PG</sub>) vs. Temperature (Ta)

2. 16 PG pin low level voltage (V<sub>PG</sub>) vs. Temperature (Ta)

2. 17 PG pin leakage current (I<sub>PG</sub>) vs. Temperature (Ta)

#### 2. 19 UVLO detection voltage (VUVLO-) vs. Temperature (Ta)

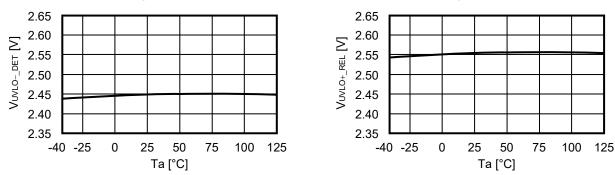

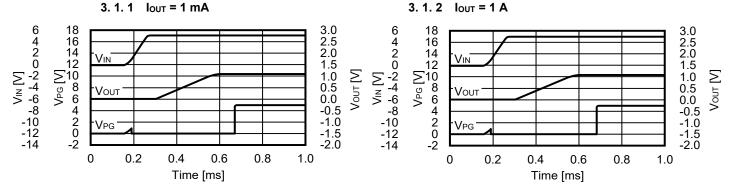

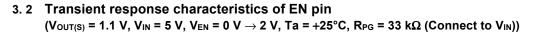

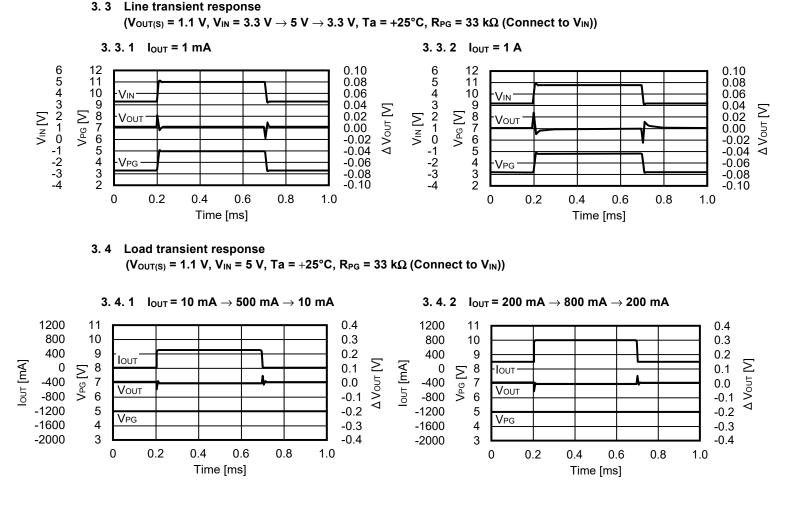

#### 3. Transient response characteristics (Ta = +25°C)

|                             |          | Table 17        |                      |

|-----------------------------|----------|-----------------|----------------------|

| Element Name                | Constant | Manufacturer    | Part Number          |

| Inductor                    | 1.5 μH   | TDK Corporation | TFM201610ALMA1R5MTAA |

| Input capacitor             | 10 μF    | TDK Corporation | CGA4J1X7S1C106K125AC |

| Output capacitor            | 10 μF    | TDK Corporation | CGA4J1X7S1C106K125AC |

| Power Good pull-up resistor | 33 kΩ    | _               | _                    |

3. 1 Power-on (V<sub>OUT(S)</sub> = 1.1 V, V<sub>IN</sub> = V<sub>EN</sub> = 0 V  $\rightarrow$  5 V, Ta = +25°C, R<sub>PG</sub> = 33 k $\Omega$  (Connect to V<sub>IN</sub>))

#### AUTOMOTIVE, 125°C OPERATION, 5.5 V INPUT, 1 A, POWER GOOD, SYNCHRONOUS STEP-DOWN SWITCHING REGULATOR S-19954/19955 Series

Rev.1.3\_00

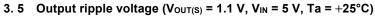

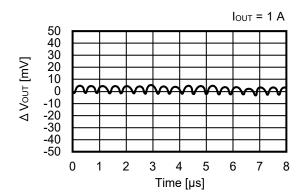

#### 3. 5. 1 S-19955 Series

3. 5. 2 S-19954/19955 Series

#### Reference Data

The external parts shown in Table 18 are used in "■ Reference Data".

|           |                               | Table 18                     |                              |

|-----------|-------------------------------|------------------------------|------------------------------|

| Condition | Inductor (L)                  | Input Capacitor (CIN)        | Output Capacitor (Cout)      |

| <1>       | TFM201610ALMA2R2MTAA (2.2 μH) | CGA4J1X7S1C106K125AC (10 μF) | CGA4J3X7S1A106K125AB (10 μF) |

|           | TDK Corporation               | TDK Corporation              | TDK Corporation              |

| <2>       | TFM201610ALMA1R5MTAA (1.5 μH) | CGA4J1X7S1C106K125AC (10 μF) | CGA4J3X7S1A106K125AB (10 μF) |

|           | TDK Corporation               | TDK Corporation              | TDK Corporation              |

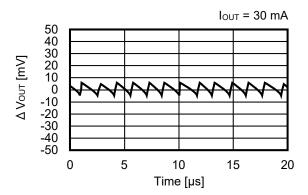

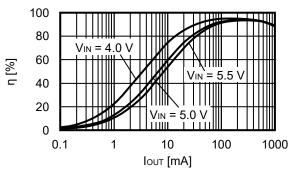

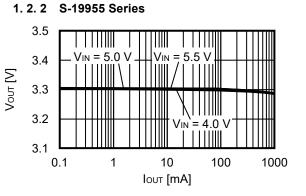

#### 1. V<sub>OUT</sub> = 3.3 V (External parts: Condition <1>)

1.1 Efficiency (η) vs. Output current (IOUT)

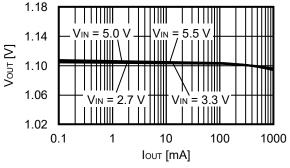

#### 1. 2 Output voltage (Vout) vs. Output current (lout)

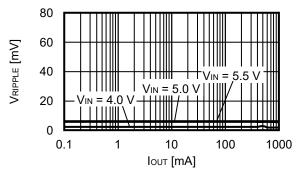

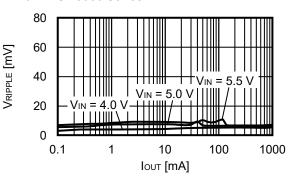

1. 3 Ripple voltage (VRIPPLE) vs. Output current (IOUT)

1.3.2 S-19955 Series

լ%] ր

1. 1. 2 S-19955 Series

100

#### Rev.1.3\_00

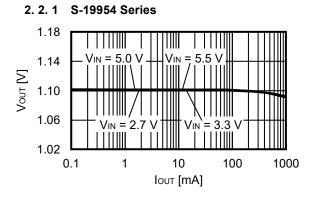

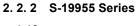

- 2. V<sub>OUT</sub> = 1.1 V (External parts: Condition <2>)

- 2. 1 Efficiency (η) vs. Output current (Iout)

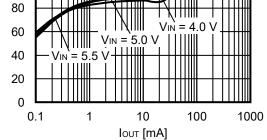

2. 2 Output voltage ( $V_{OUT}$ ) vs. Output current ( $I_{OUT}$ )

2. 3. 2 S-19955 Series

#### Power Dissipation

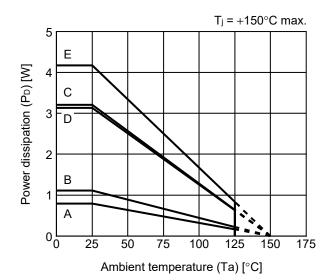

#### **HTMSOP-8**

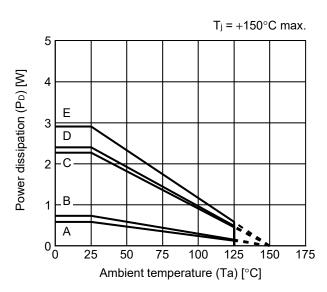

#### HSNT-8(1616)B

| Board | Power Dissipation (P <sub>D</sub> ) |

|-------|-------------------------------------|

| Α     | 0.79 W                              |

| В     | 1.11 W                              |

| С     | 3.21 W                              |

| D     | 3.13 W                              |

| E     | 4.17 W                              |

| Board | Power Dissipation (P <sub>D</sub> ) |

|-------|-------------------------------------|

| А     | 0.58 W                              |

| В     | 0.73 W                              |

| С     | 2.40 W                              |

| D     | 2.27 W                              |

| E     | 2.91 W                              |

## HTMSOP-8 Test Board

) IC Mount Area

## (1) Board A

|      | Specification                               |  |

|------|---------------------------------------------|--|

|      | 114.3 x 76.2 x t1.6                         |  |

|      | FR-4                                        |  |

| ayer | 2                                           |  |

| 1    | Land pattern and wiring for testing: t0.070 |  |

| 2    | -                                           |  |

| 3    | -                                           |  |

| 4    | 74.2 x 74.2 x t0.070                        |  |

|      | -                                           |  |

|      | 1<br>2<br>3                                 |  |

## (2) Board B

| Item                        |   | Specification                               |

|-----------------------------|---|---------------------------------------------|

| Size [mm]                   |   | 114.3 x 76.2 x t1.6                         |

| Material                    |   | FR-4                                        |

| Number of copper foil layer |   | 4                                           |

| Copper foil layer [mm]      | 1 | Land pattern and wiring for testing: t0.070 |

|                             | 2 | 74.2 x 74.2 x t0.035                        |

|                             | 3 | 74.2 x 74.2 x t0.035                        |

|                             | 4 | 74.2 x 74.2 x t0.070                        |

| Thermal via                 |   | -                                           |

## (3) Board C

| Item                        |   | Specification                               |

|-----------------------------|---|---------------------------------------------|

| Size [mm]                   |   | 114.3 x 76.2 x t1.6                         |

| Material                    |   | FR-4                                        |

| Number of copper foil layer |   | 4                                           |

| Copper foil layer [mm]      | 1 | Land pattern and wiring for testing: t0.070 |

|                             | 2 | 74.2 x 74.2 x t0.035                        |

|                             | 3 | 74.2 x 74.2 x t0.035                        |

|                             | 4 | 74.2 x 74.2 x t0.070                        |

| Thermal via                 |   | Number: 4<br>Diameter: 0.3 mm               |

≣∎≣

enlarged view

## No. HTMSOP8-A-Board-SD-1.0

## **HTMSOP-8** Test Board

Item

Size [mm]

## 🔵 IC Mount Area

Specification

## (4) Board D

114.3 x 76.2 x t1.6

enlarged view

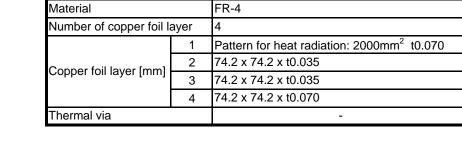

#### (5) Board E

| Item                        |   | Specification                                          |

|-----------------------------|---|--------------------------------------------------------|

| Size [mm]                   |   | 114.3 x 76.2 x t1.6                                    |

| Material                    |   | FR-4                                                   |

| Number of copper foil layer |   | 4                                                      |

| Copper foil layer [mm]      | 1 | Pattern for heat radiation: 2000mm <sup>2</sup> t0.070 |

|                             | 2 | 74.2 x 74.2 x t0.035                                   |

|                             | 3 | 74.2 x 74.2 x t0.035                                   |

|                             | 4 | 74.2 x 74.2 x t0.070                                   |

| Thermal via                 |   | Number: 4<br>Diameter: 0.3 mm                          |

enlarged view

#### No. HTMSOP8-A-Board-SD-1.0

## HSNT-8(1616)B Test Board

## ) IC Mount Are

## (1) Board A

| Item                        |   | Specification                               |

|-----------------------------|---|---------------------------------------------|

| Size [mm]                   |   | 114.3 x 76.2 x t1.6                         |

| Material                    |   | FR-4                                        |

| Number of copper foil layer |   | 2                                           |

|                             | 1 | Land pattern and wiring for testing: t0.070 |

| Copper foil layer [mm]      | 2 | -                                           |

| Copper foir layer [mm]      | 3 | -                                           |

|                             | 4 | 74.2 x 74.2 x t0.070                        |

| Thermal via                 |   | -                                           |

(2) Board B

| Item                        |   | Specification                               |

|-----------------------------|---|---------------------------------------------|

| Size [mm]                   |   | 114.3 x 76.2 x t1.6                         |

| Material                    |   | FR-4                                        |

| Number of copper foil layer |   | 4                                           |

| Copper foil layer [mm]      | 1 | Land pattern and wiring for testing: t0.070 |

|                             | 2 | 74.2 x 74.2 x t0.035                        |

|                             | 3 | 74.2 x 74.2 x t0.035                        |

|                             | 4 | 74.2 x 74.2 x t0.070                        |

| Thermal via                 |   | -                                           |

## (3) Board C

| Item                        |   | Specification                               |

|-----------------------------|---|---------------------------------------------|

| Size [mm]                   |   | 114.3 x 76.2 x t1.6                         |

| Material                    |   | FR-4                                        |

| Number of copper foil layer |   | 4                                           |

| Copper foil layer [mm]      | 1 | Land pattern and wiring for testing: t0.070 |

|                             | 2 | 74.2 x 74.2 x t0.035                        |

|                             | 3 | 74.2 x 74.2 x t0.035                        |

|                             | 4 | 74.2 x 74.2 x t0.070                        |

| Thermal via                 |   | Number: 4<br>Diameter: 0.3 mm               |

enlarged view

## No. HSNT8-C-Board-SD-1.0

## HSNT-8(1616)B Test Board

IC Mount Are

## (4) Board D

| Item                        |   | Specification                                          |

|-----------------------------|---|--------------------------------------------------------|

| Size [mm]                   |   | 114.3 x 76.2 x t1.6                                    |

| Material                    |   | FR-4                                                   |

| Number of copper foil layer |   | 4                                                      |

| Copper foil layer [mm]      | 1 | Pattern for heat radiation: 2000mm <sup>2</sup> t0.070 |

|                             | 2 | 74.2 x 74.2 x t0.035                                   |

|                             | 3 | 74.2 x 74.2 x t0.035                                   |

|                             | 4 | 74.2 x 74.2 x t0.070                                   |

| Thermal via                 |   | -                                                      |

enlarged view

#### (5) Board E

| Item                        |   | Specification                                          |

|-----------------------------|---|--------------------------------------------------------|

| Size [mm]                   |   | 114.3 x 76.2 x t1.6                                    |

| Material                    |   | FR-4                                                   |

| Number of copper foil layer |   | 4                                                      |

| Copper foil layer [mm]      | 1 | Pattern for heat radiation: 2000mm <sup>2</sup> t0.070 |

|                             | 2 | 74.2 x 74.2 x t0.035                                   |

|                             | 3 | 74.2 x 74.2 x t0.035                                   |

|                             | 4 | 74.2 x 74.2 x t0.070                                   |

| Thermal via                 |   | Number: 4<br>Diameter: 0.3 mm                          |

enlarged view

No. HSNT8-C-Board-SD-1.0

ABLIC Inc.

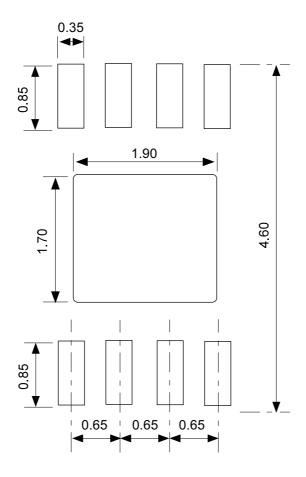

No. FP008-A-L-SD-2.0

| TITLE      | HTMSOP8-A<br>-Land Recommendation |  |

|------------|-----------------------------------|--|

| No.        | FP008-A-L-SD-2.0                  |  |

| ANGLE      |                                   |  |

| UNIT       | mm                                |  |

|            |                                   |  |

|            |                                   |  |

|            |                                   |  |

| ABLIC Inc. |                                   |  |

ABLIC Inc.

Feed direction

No. PY008-B-C-SD-1.0

| TITLE | HSNT-8-C-Carrier Tape |  |  |

|-------|-----------------------|--|--|

| No.   | PY008-B-C-SD-1.0      |  |  |

| ANGLE |                       |  |  |

| UNIT  | mm                    |  |  |

|       |                       |  |  |

|       |                       |  |  |

|       |                       |  |  |

|       | ABLIC Inc.            |  |  |

## **Disclaimers (Handling Precautions)**

- 1. All the information described herein (product data, specifications, figures, tables, programs, algorithms and application circuit examples, etc.) is current as of publishing date of this document and is subject to change without notice.

- The circuit examples and the usages described herein are for reference only, and do not guarantee the success of any specific mass-production design.

ABLIC Inc. is not liable for any losses, damages, claims or demands caused by the reasons other than the products described herein (hereinafter "the products") or infringement of third-party intellectual property right and any other right due to the use of the information described herein.

- 3. ABLIC Inc. is not liable for any losses, damages, claims or demands caused by the incorrect information described herein.

- 4. Be careful to use the products within their ranges described herein. Pay special attention for use to the absolute maximum ratings, operation voltage range and electrical characteristics, etc. ABLIC Inc. is not liable for any losses, damages, claims or demands caused by failures and / or accidents, etc. due to the use of the products outside their specified ranges.

- 5. Before using the products, confirm their applications, and the laws and regulations of the region or country where they are used and verify suitability, safety and other factors for the intended use.

- 6. When exporting the products, comply with the Foreign Exchange and Foreign Trade Act and all other export-related laws, and follow the required procedures.

- 7. The products are strictly prohibited from using, providing or exporting for the purposes of the development of weapons of mass destruction or military use. ABLIC Inc. is not liable for any losses, damages, claims or demands caused by any provision or export to the person or entity who intends to develop, manufacture, use or store nuclear, biological or chemical weapons or missiles, or use any other military purposes.

- 8. The products are not designed to be used as part of any device or equipment that may affect the human body, human life, or assets (such as medical equipment, disaster prevention systems, security systems, combustion control systems, infrastructure control systems, vehicle equipment, traffic systems, in-vehicle equipment, aviation equipment, aerospace equipment, and nuclear-related equipment), excluding when specified for in-vehicle use or other uses by ABLIC, Inc. Do not apply the products to the above listed devices and equipments. ABLIC Inc. is not liable for any losses, damages, claims or demands caused by unauthorized or unspecified use of the products.

- 9. In general, semiconductor products may fail or malfunction with some probability. The user of the products should therefore take responsibility to give thorough consideration to safety design including redundancy, fire spread prevention measures, and malfunction prevention to prevent accidents causing injury or death, fires and social damage, etc. that may ensue from the products' failure or malfunction.

The entire system in which the products are used must be sufficiently evaluated and judged whether the products are allowed to apply for the system on customer's own responsibility.

- 10. The products are not designed to be radiation-proof. The necessary radiation measures should be taken in the product design by the customer depending on the intended use.

- 11. The products do not affect human health under normal use. However, they contain chemical substances and heavy metals and should therefore not be put in the mouth. The fracture surfaces of wafers and chips may be sharp. Be careful when handling these with the bare hands to prevent injuries, etc.

- 12. When disposing of the products, comply with the laws and ordinances of the country or region where they are used.

- 13. The information described herein contains copyright information and know-how of ABLIC Inc. The information described herein does not convey any license under any intellectual property rights or any other rights belonging to ABLIC Inc. or a third party. Reproduction or copying of the information from this document or any part of this document described herein for the purpose of disclosing it to a third-party is strictly prohibited without the express permission of ABLIC Inc.

- 14. For more details on the information described herein or any other questions, please contact ABLIC Inc.'s sales representative.

- 15. This Disclaimers have been delivered in a text using the Japanese language, which text, despite any translations into the English language and the Chinese language, shall be controlling.

2.4-2019.07