# S-77100/77101系列

www.ablic.com 电源顺序控制器

© ABLIC Inc., 2015-2022 Rev.1.1\_00

S-77100/77101系列为电源顺序控制器。

S-77100系列可通过输出4通道的使能信号,来控制外部电源电路。通过切换ON端子的 "H" 和 "L",使能信号可按顺序 "开" 和 "关"。

S-77101系列可通过输出3通道的使能信号,来控制外部电源电路。通过将ON端子从 "L" 切换为 "H",使能信号可按顺序 "开",通过将OFF端子从 "H" 切换为 "L",使能信号可按顺序 "关"。

可通过外接电容器来设定各个使能信号的延迟时间。

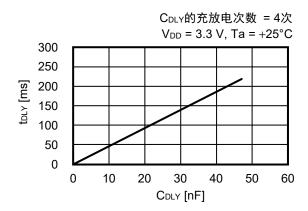

另外,因采用小型的8-Pin TSSOP或SNT-8A封装,故可高密度安装。

### ■ 特点

• 可简单地控制多个电源的顺序

- 可通过外接电容器设定延迟时间

- 可用1个输入信号来控制4通道的顺序 (S-77100系列)

- 可分别用不同的输入信号来控制上电顺序和断电顺序(S-77101系列)

- 可通过级联连接来增加使能输出信号

● 低消耗电流: 3.0 μA (典型值) (断电期间、电源安定期间、V<sub>DD</sub> = 3.3 V、Ta = +25°C)

• 宽工作电压范围: 2.2 V~5.5 V

● 工作温度范围: Ta = -40°C ~ +85°C

● 可选择输出方式: CMOS输出、N沟道开路漏极输出

● 可选择输出逻辑: 动态 "H"、动态 "L"

• 无铅 (Sn 100%)、无卤素

### ■ 用途

- 多台装置的电源顺序控制

- 微处理器、微控制器的顺序控制

- FPGA的电源顺序控制

- 电视机、照相机、打印机等的电源顺序控制

### ■ 封装

- 8-Pin TSSOP

- SNT-8A

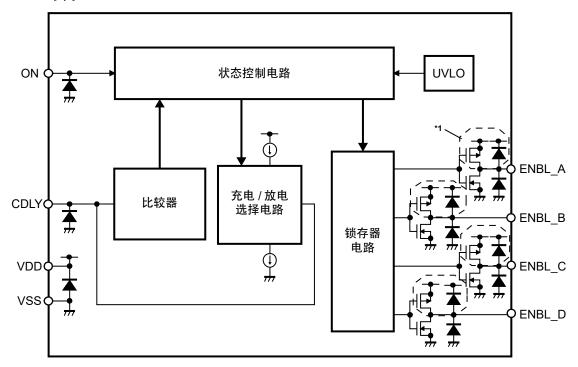

### ■ 框图

### 1. S-77100系列

\*1. 可以选项

图1

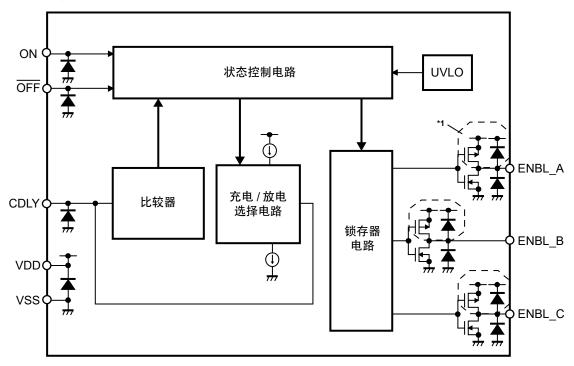

### 2. S-77101系列

\*1. 可以选项

图2

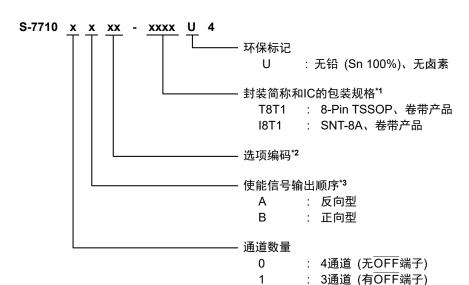

### ■ 产品型号的构成

### 1. 产品名

- \*1. 请参阅卷带图。

- \*2. 请参阅"2. 产品选项一览"。

- \*3. 可选择断电顺序期间的使能信号输出 (ENBL x端子) 翻转的顺序。

S-77100系列

A:按照ENBL\_D端子、ENBL\_C端子、ENBL\_B端子、ENBL\_A端子的顺序变为 "L"。 B:按照ENBL\_A端子、ENBL\_B端子、ENBL\_C端子、ENBL\_D端子的顺序变为 "L"。 S-77101系列

A:按照ENBL\_C端子、ENBL\_B端子、ENBL\_A端子的顺序变为 "L"。B:按照ENBL\_A端子、ENBL\_B端子、ENBL\_C端子的顺序变为 "L"。

### 2. 产品选项一览

表1

| 选项编码 | 外接电容器 (CDLY) 的充放电次数*1 | 输入电位*2  | 输出方式*3    | 输出逻辑*4 |

|------|-----------------------|---------|-----------|--------|

| 01   | 4                     | 施密特触发输入 | CMOS输出    | 动态 "H" |

| 02   | 4                     | 施密特触发输入 | N沟道开路漏极输出 | 动态 "H" |

| 11   | 4                     | 比较器输入   | CMOS输出    | 动态 "H" |

| 12   | 4                     | 比较器输入   | N沟道开路漏极输出 | 动态 "H" |

| 31   | 4                     | 比较器输入   | CMOS输出    | 动态 "L" |

\*1. 为了调整延迟时间 (t<sub>DLY</sub>) 的选项。可选择C<sub>DLY</sub>的充放电次数。

本数据表以选择4次时为例进行说明。

2次 / 4次

\*2. 可选择ON端子、OFF端子的输入电位。

施密特触发输入 / 比较器输入

\*3. 可选择ENBL\_x端子的输出方式。

CMOS输出 / N沟道开路漏极输出

\*4. 可选择ENBL x端子的输出逻辑。

本数据表以选择动态 "H" 时为例进行说明。

动态 "H": 电源安定期间为 "H" 的类型 / 动态 "L": 电源安定期间为 "L" 的类型

### 3. 封装

### 表2 封装图纸号码

| 封装名         | 外形尺寸图        | 卷带图          | 带卷图          | 焊盘图          |

|-------------|--------------|--------------|--------------|--------------|

| 8-Pin TSSOP | FT008-A-P-SD | FT008-E-C-SD | FT008-E-R-S1 | _            |

| SNT-8A      | PH008-A-P-SD | PH008-A-C-SD | PH008-A-R-SD | PH008-A-L-SD |

### 4. 产品名目录

### 4. 1 8-Pin TSSOP

### 表3

| 产品名               | 通道数量 | 使能信号输出顺序 | CDLY的充放电次数 | 输入电位    | 输出方式      | 输出逻辑   |

|-------------------|------|----------|------------|---------|-----------|--------|

| S-77100A01-T8T1U4 | 4    | 反向型      | 4          | 施密特触发输入 | CMOS输出    | 动态 "H" |

| S-77100A02-T8T1U4 | 4    | 反向型      | 4          | 施密特触发输入 | N沟道开路漏极输出 | 动态 "H" |

| S-77100A12-T8T1U4 | 4    | 反向型      | 4          | 比较器输入   | N沟道开路漏极输出 | 动态 "H" |

### 4. 2 SNT-8A

### 表4

| 产品名               | 通道数量 | 使能信号输出顺序 | CDLY的充放电次数 | 输入电位    | 输出方式      | 输出逻辑   |

|-------------------|------|----------|------------|---------|-----------|--------|

| S-77100A01-I8T1U4 | 4    | 反向型      | 4          | 施密特触发输入 | CMOS输出    | 动态 "H" |

| S-77100A02-I8T1U4 | 4    | 反向型      | 4          | 施密特触发输入 | N沟道开路漏极输出 | 动态 "H" |

| S-77100A31-I8T1U4 | 4    | 反向型      | 4          | 比较器输入   | CMOS输出    | 动态 "L" |

| S-77100B02-I8T1U4 | 4    | 正向型      | 4          | 施密特触发输入 | N沟道开路漏极输出 | 动态 "H" |

| S-77100A12-I8T1U4 | 4    | 反向型      | 4          | 比较器输入   | N沟道开路漏极输出 | 动态 "H" |

| S-77100B01-I8T1U4 | 4    | 正向型      | 4          | 施密特触发输入 | CMOS输出    | 动态 "H" |

| S-77100A11-I8T1U4 | 4    | 反向型      | 4          | 比较器输入   | CMOS输出    | 动态 "H" |

**备注** 用户需要上述以外的产品时,请向代理商咨询。

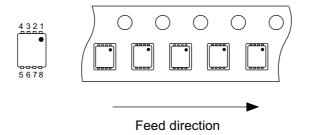

### ■ 引脚排列图

### 1. 8-Pin TSSOP

图3

|     | 表5       |                   |  |  |  |

|-----|----------|-------------------|--|--|--|

| 引脚号 | 符号       | 描述                |  |  |  |

| 1   | ENBL_A   | 使能信号输出端子          |  |  |  |

| 2   | ENBL_B   | 使能信号输出端子          |  |  |  |

| 3   | CDLY     | 外接电容器 (CDLY) 连接端子 |  |  |  |

| 4   | VSS      | 接地 (GND) 端子       |  |  |  |

| 5   | ON       | 使能信号有效的触发输入端子     |  |  |  |

| C   | ENBL_D*1 | 使能信号输出端子          |  |  |  |

| 6   | OFF*2    | 使能信号无效的触发输入端子     |  |  |  |

| 7   | ENBL_C   | 使能信号输出端子          |  |  |  |

| 8   | VDD      | 正电源端子             |  |  |  |

- \*1. 仅限S-77100系列

- \*2. 仅限S-77101系列

### 2. SNT-8A

图4

### 表6

|     |          | ***               |

|-----|----------|-------------------|

| 引脚号 | 符号       | 描述                |

| 1   | ENBL_A   | 使能信号输出端子          |

| 2   | ENBL_B   | 使能信号输出端子          |

| 3   | CDLY     | 外接电容器 (CDLY) 连接端子 |

| 4   | VSS      | 接地 (GND) 端子       |

| 5   | ON       | 使能信号有效的触发输入端子     |

| 6   | ENBL_D*1 | 使能信号输出端子          |

| 6   | OFF*2    | 使能信号无效的触发输入端子     |

| 7   | ENBL_C   | 使能信号输出端子          |

| 8   | VDD      | 正电源端子             |

- \*1. 仅限S-77100系列

- \*2. 仅限S-77101系列

### ■ 各端子的功能说明

### 1. ON端子

此端子是为了开始顺序控制工作的触发输入端子。

在S-77100系列,若检测到上升信号则进行上电顺序。若检测到下降信号则进行断电顺序。

在S-77101系列, 若检测到上升信号则进行上电顺序。

有关详情,请参阅 "■ 工作说明" 的 "1. 顺序控制工作"。

#### 2. OFF端子 (仅限S-77101系列)

此端子是为了开始断电顺序控制工作的触发输入端子。若检测到下降信号则进行断电顺序。有关详情,请参阅 "■ 工作说明" 的 "1. 顺序控制工作"。

### 3. ENBL\_A, ENBL\_B, ENBL\_C, ENBL\_D端子 (ENBL\_D端子仅限S-77100系列)

这些端子是为了将使能信号输出到外部电源电路的端子。

ENBL\_x端子的输出方式可以选择N沟道开路漏极输出 / CMOS输出的选项。另外,ENBL\_x端子的输出逻辑可以选择动态 "H" / 动态 "L" 的选项。

关于顺序控制工作,请参阅 "■ 工作说明" 的 "1. **顺序控制工作**"。关于选项,请参阅 "■ 产品型号的构成" 的 "2. 产品选项一览"。

#### 4. CDLY端子

此端子是为了生成上电顺序以及断电顺序的延迟时间 (toly),连接外接电容器 (Coly) 的端子。Coly可通过定电流电路被充放电。ON端子上升后充放电开始工作,从此时起到ENBL\_A端子上升结束为止的时间即为S-77100/77101系列生成的toly。

关于工作的时序,请参阅 "■ **工作说明**" 的 "1. **顺序控制工作**"。关于延迟时间,请参阅 "■ **延迟时间与外接电容器的 关系**"。

#### 5. VDD端子

请将此端子连接到正电源。有关施加电压值,请参阅 **"■ 电气特性**"。

### 6. VSS端子

请将此端子连接到接地 (GND) 端子。

### ■ 绝对最大额定值

表7

|           |                                                 | <b>~</b> .            |                       |                                       |    |

|-----------|-------------------------------------------------|-----------------------|-----------------------|---------------------------------------|----|

| 项目        | 符号                                              | 适用端子                  | 绝对                    | 付最大额定值                                | 单位 |

| 电源电压      | $V_{DD}$                                        | VDD                   | Vss -                 | 0.3 ~ V <sub>SS</sub> + 6.5           | V  |

| 输入电压      | V <sub>IN</sub>                                 | ON, OFF (仅限S-77101系列) | Vss - 0               | $0.3 \sim V_{DD} + 0.3^{*1}$          | V  |

| 输出电压 Vout | ENBL_A, ENBL_B, ENBL_C,<br>ENBL_D (仅限S-77100系列) | N沟道开路漏极<br>输出         | Vss - 0.3 ~ Vss + 6.5 | V                                     |    |

|           |                                                 | ENBL_D (汉成3-77 100余列) | CMOS输出                | $V_{SS} - 0.3 \sim V_{DD} + 0.3^{*1}$ | V  |

| 工作环境温度*2  | T <sub>opr</sub>                                | _                     | -                     | -40 ~ +85                             | °C |

| 保存温度      | T <sub>stg</sub>                                | _                     | _                     | 55 ~ +150                             | °C |

<sup>\*1.</sup> 请不要超过6.5 V。

注意 绝对最大额定值是指在任何条件下都不能超过的额定值。万一超过此额定值,有可能造成产品劣化等物理性的损伤。

<sup>\*2.</sup> 无结露或无霜的状态。因为结露或结霜会引起端子间发生短路,而导致错误工作。

### ■ 电气特性

表8

(除特殊注明以外: Ta = -40°C ~ +85°C, V<sub>DD</sub> = 2.2 V ~ 5.5 V, V<sub>SS</sub> = 0 V)

| 项目                           | 符号                 | 适用端子                                      | 条件                                                                                                                                        | 最小值                      | 典型值*1 | 最大值                   | 单位 |

|------------------------------|--------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------|-----------------------|----|

| 工作电源电压                       | $V_{DD}$           | VDD                                       | _                                                                                                                                         | 2.2                      | _     | 5.5                   | V  |

| 消耗电流1<br>(断电期间)              | I <sub>DD1</sub>   | VDD                                       | V <sub>DD</sub> = 3.3 V,<br>ON端子, OFF端子* <sup>2</sup> = V <sub>SS</sub> ,<br>ENBL_x端子 = 开路                                                | _                        | 3.0   | 6.0                   | μА |

| 消耗电流2<br>(电源安定期间)            | I <sub>DD2</sub>   | VDD                                       | V <sub>DD</sub> = 3.3 V,<br>ON端子, OFF端子* <sup>2</sup> = V <sub>DD</sub> ,<br>ENBL_x端子 = 开路                                                | -                        | 3.0   | 6.0                   | μΑ |

| 消耗电流3<br>(上电顺序期间、<br>断电顺序期间) | I <sub>DD3</sub>   | VDD                                       | V <sub>DD</sub> = 3.3 V,<br>ON端子, OFF端子* <sup>2</sup> = V <sub>DD</sub> or V <sub>SS</sub> ,<br>ENBL_x端子 = 开路                             | Ι                        | -     | 8.0                   | μА |

| 低电压检测电压                      | V <sub>UVLO</sub>  | VDD                                       | _                                                                                                                                         | 1.85                     | 2.0   | 2.13                  | V  |

| 高电位输入泄漏电流                    | I <sub>IZH</sub>   | ON, OFF*2                                 | $V_{IN} = V_{DD}$                                                                                                                         | -0.3                     | _     | 0.3                   | μΑ |

| 低电位输入泄漏电流                    | I <sub>IZL</sub>   | ON, OFF*2                                 | $V_{IN} = V_{SS}$                                                                                                                         | -0.3                     | _     | 0.3                   | μΑ |

| 输入电压                         | VIL                | ON, OFF*2                                 | -                                                                                                                                         | Vss -<br>0.3             | _     | $0.2 \times V_{DD}$   | V  |

| (选择施密特触发输入时)                 | V <sub>IH</sub>    | ON, OFF*2                                 | -                                                                                                                                         | $0.8 \times V_{DD}$      | -     | V <sub>DD</sub> + 0.3 | V  |

| 输入阈值电压<br>(选择比较器输入时)         | V <sub>IT_ON</sub> | ON, OFF*2                                 | -                                                                                                                                         | 0.3                      | 0.8   | 1.3                   | V  |

| 高电位输出泄漏电流*3                  | Гоzн               | ENBL_A,<br>ENBL_B,<br>ENBL_C,<br>ENBL_D*4 | $V_{OUT} = V_{DD}$                                                                                                                        | -0.3                     | -     | 0.3                   | μА |

| 低电位输出泄漏电流*3                  | lozL               | ENBL_A,<br>ENBL_B,<br>ENBL_C,<br>ENBL_D*4 | V <sub>OUT</sub> = V <sub>SS</sub>                                                                                                        | -0.3                     | -     | 0.3                   | μА |

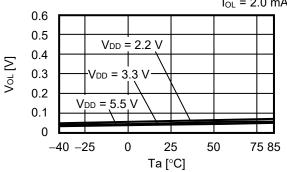

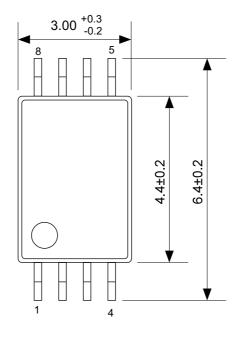

| 低电位输出电压                      | V <sub>OL</sub>    | ENBL_A,<br>ENBL_B,<br>ENBL_C,<br>ENBL_D*4 | I <sub>OL</sub> = 2.0 mA                                                                                                                  | -                        | _     | 0.4                   | V  |

| 高电位输出电压*5                    | V <sub>OH</sub>    | ENBL_A,<br>ENBL_B,<br>ENBL_C,<br>ENBL_D*4 | I <sub>OH</sub> = -0.4 mA                                                                                                                 | 0.8 ×<br>V <sub>DD</sub> | -     | _                     | V  |

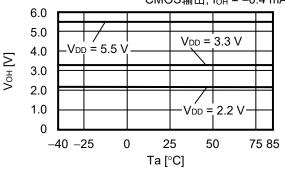

| 延迟时间*6                       | t <sub>DLY</sub>   | ENBL_A,<br>ENBL_B,<br>ENBL_C,<br>ENBL_D*4 | Ta = +25°C, V <sub>DD</sub> = 3.3 V,<br>在从ENBL_A端子的上升到ENBL_B<br>端子的上升为止的期间内,<br>C <sub>DLY</sub> = 10 nF,<br>C <sub>DLY</sub> 的充放电次数 = 4次 | 40                       | 45    | 50                    | ms |

<sup>\*1.</sup> 典型值为Ta = +25°C时的值。

<sup>\*2.</sup> 仅限S-77101系列

<sup>\*3.</sup> 在选择N沟道开路漏极输出的选项时。

<sup>\*4.</sup> 仅限S-77100系列

<sup>\*5.</sup> 在选择CMOS输出的选项时。

<sup>\*6.</sup> 延迟时间因使用环境的不同而发生变化。请在实际的应用电路上进行充分的实测后再设定参数。有关详情,请参阅 "■ 延迟时间与外接电容器的关系"。

### ■ 工作说明

### 1. 顺序控制工作

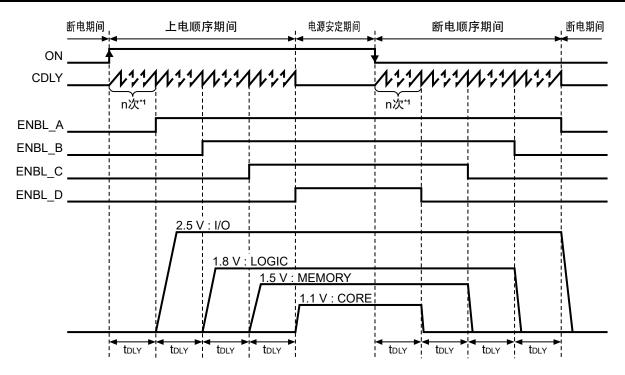

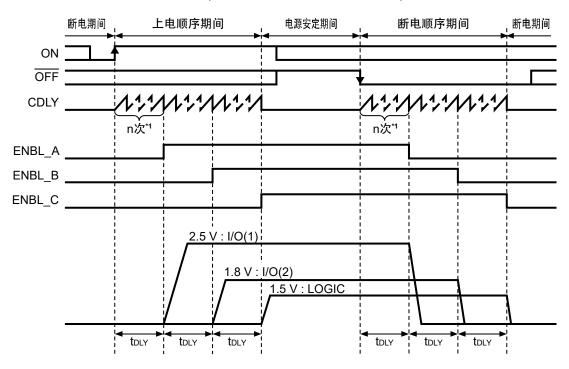

#### 1.1 S-77100A (反向型)、S-77100B (正向型)

S-77100系列备有4通道 (ENBL\_A端子、ENBL\_B端子、ENBL\_C端子、ENBL\_D端子) 的使能输出。反向型和正向型的断电顺序不同。

#### 1.1.1 顺序控制工作概要

#### (1) 上电顺序

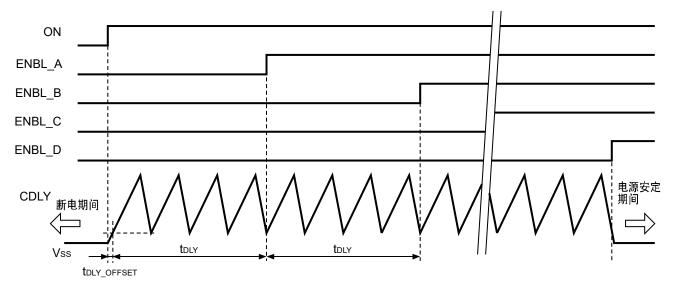

ON端子从 "L" 变为 "H" 后,外接电容器(C<sub>DLY</sub>)开始进行充电工作,充满电后开始进行放电工作。此操作经过n次重复的时间即为延迟时间(t<sub>DLY</sub>),此后,ENBL\_A端子变为 "H"。同样,每经过一次t<sub>DLY</sub>,按照ENBL\_B端子、ENBL\_C 端子、ENBL\_D端子的顺序依次变为 "H"。从ON端子由 "L" 变为 "H" 开始,到ENBL\_D端子变为 "H" 为止的期间称为 "上电顺序期间"。

### (2) 断电顺序

ON端子从 "H" 变为 "L" 后, CDLY开始进行充电工作,充满电后开始进行放电工作。此操作经过n次重复的时间即为tdLY,此后,S-77100A按照ENBL\_D端子、ENBL\_C端子、ENBL\_B端子、ENBL\_A端子的顺序依次变为 "L"。S-77100B按照ENBL\_A端子、ENBL\_B端子、ENBL\_C端子、ENBL\_D端子的顺序依次变为 "L"。从ON端子由 "H" 变为 "L" 开始,到S-77100A的ENBL\_A端子、S-77100B的ENBL\_D端子变为 "L" 为止的期间称为 "断电顺序期间"。

为了正常地进行顺序控制工作,在上电顺序期间以及断电顺序期间请不要让ON端子发生变化。

决定toLy的CoLy的充放电次数可在选项中选择2次/4次。

通过恒流电路对Cply进行充电工作和放电工作,生成tply。有关Cply与tply的关系,请参阅 **■ 延迟时间与外接电容器** 的关系"。

另外,从ENBL\_A端子、ENBL\_B端子、ENBL\_C端子、ENBL\_D端子全部变为 "H" 开始,到断电顺序为止的期间称为 "电源安定期间"、从ENBL\_A端子、ENBL\_B端子、ENBL\_C端子、ENBL\_D端子全部变为 "L" 开始,到上电顺序为止的期间称为 "断电期间"。

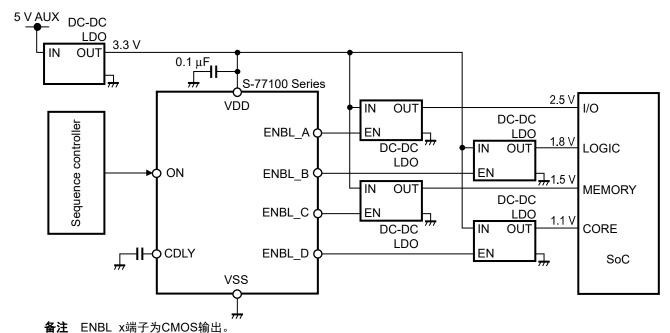

外围电路连接例请参阅图5。

S-77100A的时序图如图6所示、S-77100B的时序图如图7所示。

图5 外围电路连接例 (S-77100A: 反向型、S-77100B: 正向型)

#### 注意1. 请在对S-77100系列施加的电源电压稳定后再进行输入。

2. 上述连接图并不作为保证电路工作的依据。请在实际的应用电路上进行充分的实测后再设定参数。

\*1. 可以选项:2次/4次

图6 时序图 (S-77100A:反向型)

\*1. 可以选项:2次/4次

图7 时序图 (S-77100B:正向型)

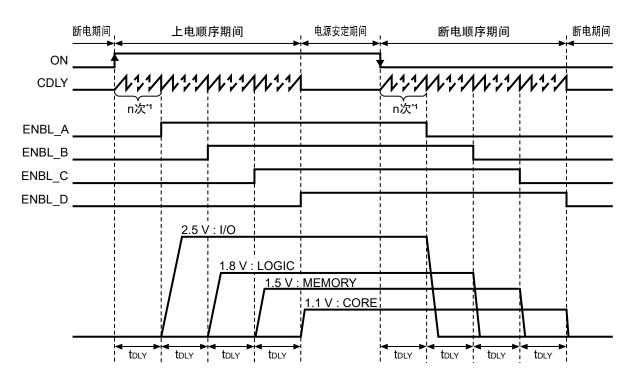

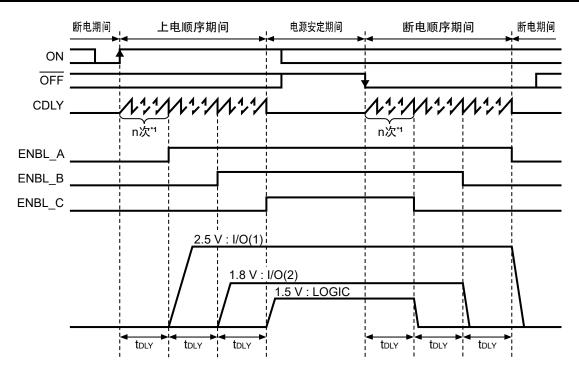

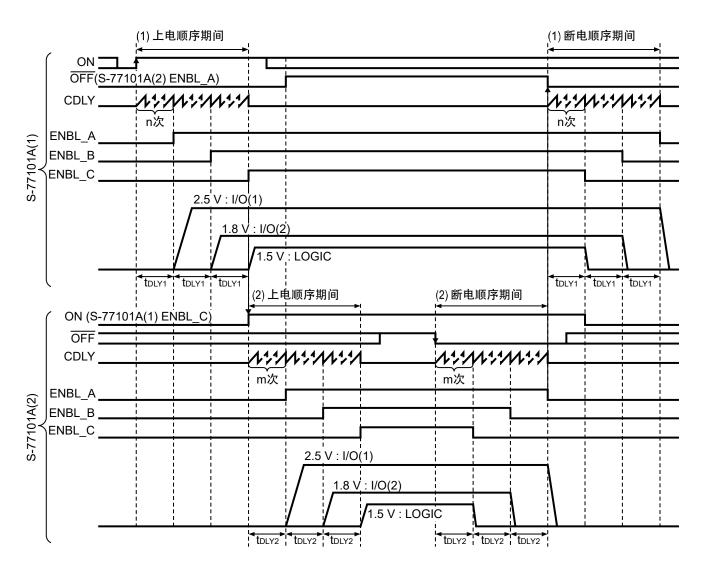

### 1. 2 S-77101A (反向型、备有OFF端子)、S-77101B (正向型、备有OFF端子)

S-77101系列备有3通道 (ENBL\_A端子、ENBL\_B端子、ENBL\_C端子) 的使能输出和OFF端子。反向型和正向型的断电顺序不同。

### 1.2.1 顺序控制工作概要

#### (1) 上电顺序

ON端子从 "L" 变为 "H" 后,外接电容器( $C_{DLY}$ )开始进行充电工作,充满电后开始进行放电工作。此操作经过n次重复的时间即为延迟时间( $t_{DLY}$ ),此后,ENBL\_A端子变为 "H"。同样,每经过一次 $t_{DLY}$ ,按照ENBL\_B端子、ENBL\_C端子的顺序依次变为 "H"。从ON端子由 "L" 变为 "H" 开始,到ENBL\_C端子变为 "H" 为止的期间称为 "上电顺序期间"。

#### (2) 断电顺序

OFF端子从 "H" 变为 "L" 后,C<sub>DLY</sub>开始进行充电工作,充满电后开始进行放电工作。此操作经过n次重复的时间即为t<sub>DLY</sub>,此后,S-77101A按照ENBL\_C端子、ENBL\_B端子、ENBL\_A端子的顺序依次变为 "L"。S-77101B按照ENBL\_A端子、ENBL\_B端子、ENBL\_C端子的顺序依次变为 "L"。从OFF端子由 "H" 变为 "L" 开始,到S-77101A的ENBL\_A端子、S-77101B的ENBL C端子变为 "L" 为止的期间称为 "断电顺序期间"。

为了正常地进行顺序控制工作,在上电顺序期间以及断电顺序期间请不要让ON端子和OFF端子发生变化。 决定toLy的CoLy的充放电次数可在选项中选择2次/4次。

通过恒流电路对C<sub>DLY</sub>进行充电工作和放电工作,生成t<sub>DLY</sub>。有关C<sub>DLY</sub>与t<sub>DLY</sub>的关系,请参阅 **"■ 延迟时间与外接电容器的关系"**。

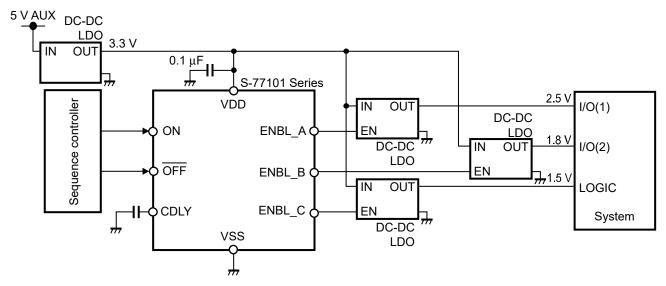

另外,从ENBL\_A端子、ENBL\_B端子、ENBL\_C端子全部变为 "H" 开始,到断电顺序为止的期间称为 "电源安定期间"、从ENBL\_A端子、ENBL\_B端子、ENBL\_C端子全部变为 "L" 开始,到上电顺序为止的期间称为 "断电期间"。即使在电源安定期间ON端子从 "H" 变为 "L"、或在断电期间OFF端子从 "L" 变为 "H",也不影响顺序控制工作。外围电路连接例请参阅图8。

S-77101A的时序图如图9所示、S-77101B的时序图如图10所示。

备注 ENBL\_x端子为CMOS输出。

图8 外围电路连接例 (S-77101A:反向型、备有OFF端子、S-77101B:正向型、备有OFF端子)

#### 注意1. 请在对S-77101系列施加的电源电压稳定后再进行输入。

2. 上述连接图并不作为保证电路工作的依据。请在实际的应用电路上进行充分的实测后再设定参数。

\*1. 可以选项:2次/4次

图9 时序图 (S-77101A: 反向型、备有OFF端子)

\*1. 可以选项:2次/4次

图10 时序图 (S-77101B:正向型、备有OFF端子)

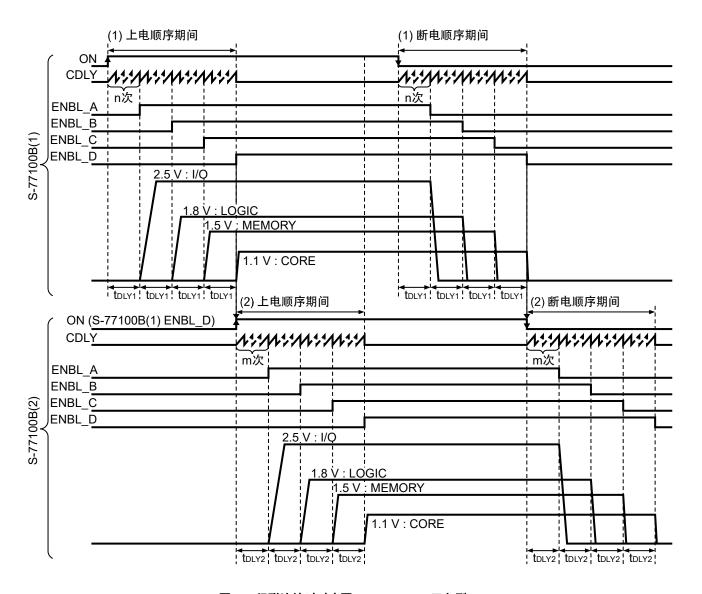

### 2. 级联连接

#### 2.1 S-77100B (正向型)

S-77100B可通过级联连接来增加使能输出信号。2个S-77100B级联连接后的外围电路连接例如**图11**所示。把S-77100B(1)的ENBL\_D端子与S-77100B(2)的ON端子相连接。时序图如**图12**所示。

#### 5 V AUX DC-DC LDO $0.1 \, \mu F$ IN OUT 3.3 V ጔ S-77100B(1) 2.5 V VĎD 1/0 IN OUT DC-DC LDO ENBL\_A Sequence controller 1.8 V DC-DC LDO LOGIC ΙN OUT ENBL\_B ON ΕN **MEMORY** ΙN OUT 1.5 √ DC-DC LDO ENBL C 1.1 V CORE DC-DC LDO ΙN OUT SoC1 ΕN **♦** CDLY ENBL\_D 🗘 ╢ VSS System 3.3 V **ι Ι**Ο.1 μF S-77100B(2) 2.5 V VĎD IN OUT I/O DC-DC LDO ENBL A 1.8 V DC-DC LDO ĪΝ LOGIC OUT ENBL\_B ΕN ио С **MEMORY** ΙN OUT 1.5 V DC-DC LDO ΕN ENBL C 1.1 V IN CORE DC-DC LDO OUT SoC2 ΕN ENBL\_D C VSS

备注 ENBL\_x端子为CMOS输出。

图11 外围电路连接例 (S-77100B:正向型)

- 注意 1. 请在对S-77100B施加的电源电压稳定后再进行输入。

- 2. 上述连接图并不作为保证电路工作的依据。请在实际的应用电路上进行充分的实测后再设定参数。

- 3. 不能共用连接在S-77100B(1)和S-77100B(2)的CDLY端子上的外接电容器 (CDLY)。

图12 级联连接时时序图 (S-77100B:正向型)

S-77100B(1)的ON端子从 "L" 变为 "H" 后,按照S-77100B(1)的ENBL\_A端子、ENBL\_B端子、ENBL\_C端子、ENBL\_D端子的顺序依次变为 "H"。

S-77100B(1)的ENBL\_D端子从 "L" 变为 "H" 后,按照S-77100B(2)的ENBL\_A端子、ENBL\_B端子、ENBL\_C端子、ENBL\_D端子的顺序依次变为 "H"。

S-77100B(1)的ON端子从 "H" 变为 "L" 后, 按照S-77100B(1)的ENBL\_A端子、ENBL\_B端子、ENBL\_C端子、ENBL\_D端子的顺序依次变为 "L"。

S-77100B(1)的ENBL\_D端子从 "H" 变为 "L" 后,按照S-77100B(2)的ENBL\_A端子、ENBL\_B端子、ENBL\_C端子、ENBL\_D端子的顺序依次变为 "L"。

为了正常地进行顺序控制工作,在上电顺序期间以及断电顺序期间,请不要让ON端子发生变化。

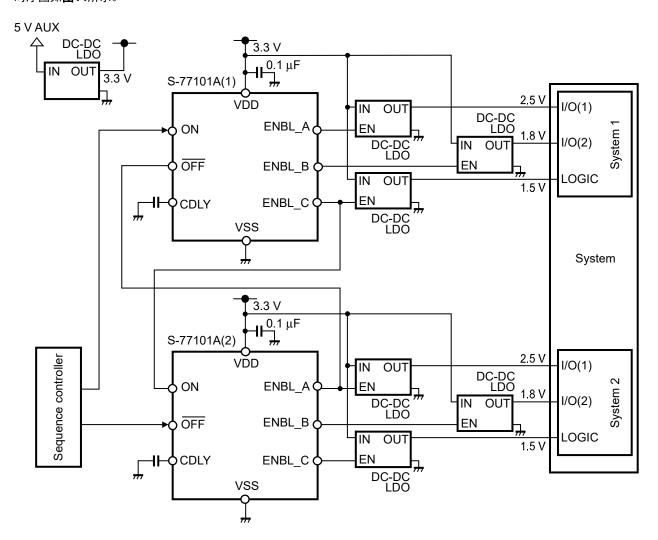

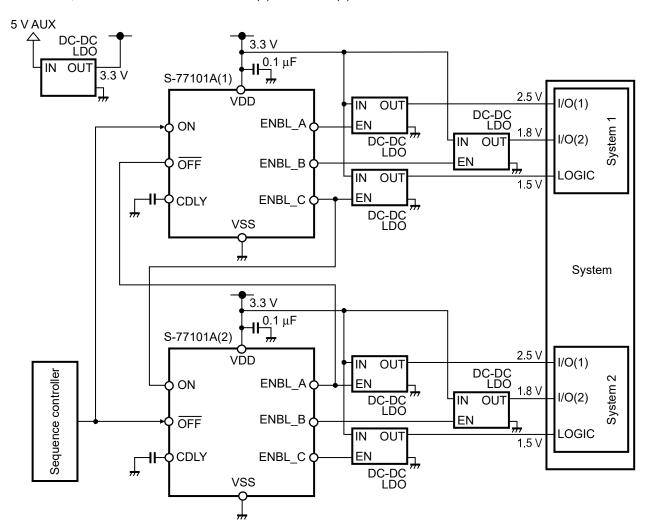

### 2. 2 S-77101A (反向型、备有OFF端子)

S-77101A可通过级联连接来增加使能输出信号。2个S-77101A级联连接后的外围电路连接例如**图13**所示。 把S-77101A(1)的ENBL\_C端子与S-77101A(2)的ON端子相连接,S-77101A(1)的OFF端子与S-77101A(2)的ENBL\_A端子相连接。

时序图如图14所示。

备注 ENBL\_x端子为CMOS输出。

图13 外围电路连接例 (S-77101A:反向型、备有OFF端子)

- 注意 1. 请在对S-77101A施加的电源电压稳定后再进行输入。

- 2. 上述连接图并不作为保证电路工作的依据。请在实际的应用电路上进行充分的实测后再设定参数。

- 3. 不能共用连接在S-77101A(1)和S-77101A(2)的CDLY端子上的外接电容器 (CDLY)。

图14 级联连接的时序图 (S-77101A: 反向型、备有OFF端子)

S-77101A(1)的ON端子从 "L" 变为 "H" 后,按照S-77101A(1)的ENBL\_A端子、ENBL\_B端子、ENBL\_C端子的顺序依次变为 "H"。

S-77101A(1)的ENBL\_C端子从 "L" 变为 "H" 后,按照S-77101A(2)的ENBL\_A端子、ENBL\_B端子、ENBL\_C端子的顺序依次变为 "H"。

S-77101A(2)的OFF端子从 "H" 变为 "L" 后,按照S-77101A(2)的ENBL\_C端子、ENBL\_B端子、ENBL\_A端子的顺序 依次变为 "L"。

S-77101A(2)的ENBL\_A端子从 "H" 变为 "L" 后,按照S-77101A(1)的ENBL\_C端子、ENBL\_B端子、ENBL\_A端子的顺序依次变为 "L"。

为了正常地进行顺序控制工作,在上电顺序期间以及断电顺序期间,请不要让ON端子和OFF端子发生变化。

如**图14**所示,S-77101A(1)的ON端子从 "L" 变为 "H" 后,不管S-77101A(2)的OFF端子处于 "H"、"L" 的任意一方,均可进行上电顺序。同样,S-77101A(2)的OFF端子从 "H" 变为 "L" 后,不管S-77101A(1)的ON端子处于 "H"、"L" 的任意一方,均可进行断电顺序。因此,通过把S-77101A(1)的ON端子和S-77101A(2)的OFF端子连接到顺序控制器的控制信号端子,可利用一个信号来控制S-77101A(1)和S-77101A(2)。连接例如**图15**所示。

备注 ENBL\_x端子为CMOS输出。

图15 级联连接例 (S-77101A: 反向型、备有OFF端子)

#### 3. 特殊工作

#### 3.1 S-77100系列的特殊工作

没有正常完成顺序控制工作时、电源电压急剧降低时及连接VDD端子与ON端子时的工作为特殊工作。

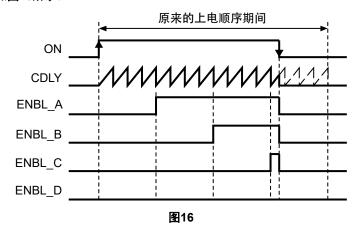

### 3.1.1 在上电顺序期间以及断电顺序期间的特殊工作

为了正常地进行顺序控制工作,在上电顺序期间以及断电顺序期间请不要让ON端子发生变化。

### (1) 在上电顺序期间ON端子从 "H" 变为 "L" 时

ENBL\_x端子会全部变为 "L", 此时不能保证断电顺序的时序。另外, CDLy的充电工作会被中止, 并开始进行深度放电工作。工作例如**图16**所示。

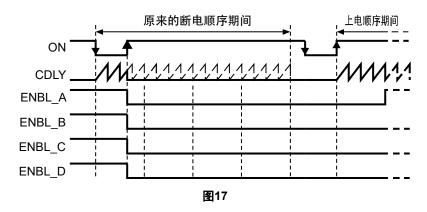

### (2) 在断电顺序期间ON端子从 "L" 变为 "H" 时

ENBL\_x端子会全部变为 "L",此时不能保证断电顺序的时序。另外,CDLy的充电工作会被中止,并开始进行深度放电工作。要想再次进行上电顺序,请将ON端子先设定为 "L" 后再使其变为 "H"。工作例如**图17**所示。

备注 有关深度放电工作,请参阅 "■ 延迟时间与外接电容器的关系"的 "3. 深度放电时间 (tосна) 的概略计算公式"。

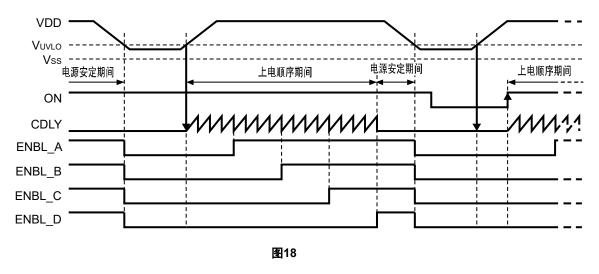

#### 3.1.2 检测出低电压时的工作

#### (1) 在电源安定期间检测出低电压时

当电源电压 (VDD) 小于或等于低电压检测电压 (VUVLO) 时,ENBL\_x端子会全部变为 "L",此时不能保证断电顺序的时序。此后,当VDD超过VUVLO时,若ON端子为 "H",则自动地进行上电顺序。当VDD超过VUVLO时,若ON端子为 "L",则不进行上电顺序。如需进行上电顺序,请再次将ON端子设定为 "H"。工作例如图18所示。

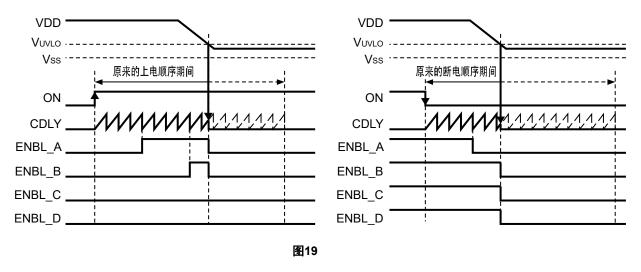

#### (2) 在上电顺序期间、断电顺序期间检测出低电压时

在上电顺序期间或断电顺序期间,当VDD小于或等于VUVLO时,ENBL\_x端子会全部变为 "L",此时不能保证断电顺序的时序。另外,CDLy的充电工作会被中止,并开始进行深度放电工作。工作例如**图19**所示。

备注 有关深度放电工作,请参阅 "■ 延迟时间与外接电容器的关系" 的 "3. 深度放电时间 (tochg) 的概略计算公式"。

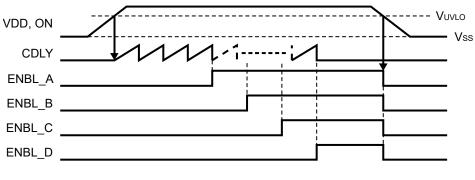

### 3. 1. 3 连接VDD端子与ON端子时的工作

连接VDD端子与ON端子,电源电压上升后,会自动地进行上电顺序。但是,在电源电压下降时,若 $V_{DD}$ 小于或等于 $V_{UVLO}$ ,ENBL\_x端子会全部变为 "L",此时不能保证断电顺序的时序。工作例如**图20**所示。

图20

#### 3.2 S-77101系列的特殊工作

没有正常完成顺序控制工作时、电源电压过低时及连接VDD端子、ON端子、OFF端子时的工作为特殊工作。

#### 3.2.1 在上电顺序期间以及断电顺序期间的特殊工作

为了正常地进行顺序控制工作,在上电顺序期间以及断电顺序期间,请不要让ON端子以及OFF端子发生变化。

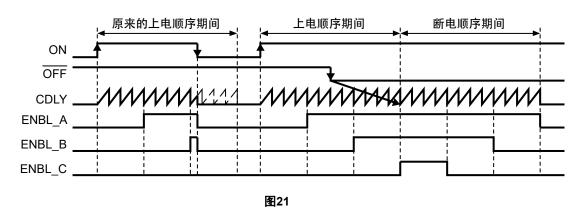

### (1) 在上电顺序期间ON端子或OFF端子从 "H" 变为 "L" 时

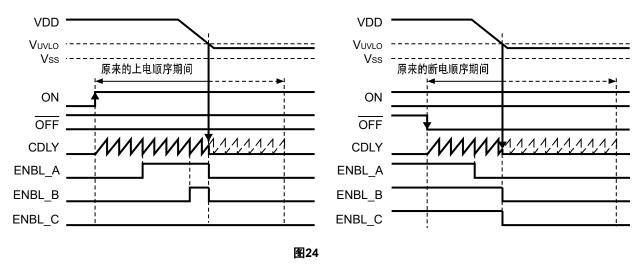

在上电顺序期间,若ON端子从 "H" 变为 "L", ENBL\_x端子会全部变为 "L", 此时不能保证断电顺序的时序。另外, Cply的充电工作会被中止,并开始进行深度放电工作。在上电顺序期间,若OFF端子从 "H" 变为 "L", 在上电顺序完成后会开始进行断电顺序。工作例如**图21**所示。

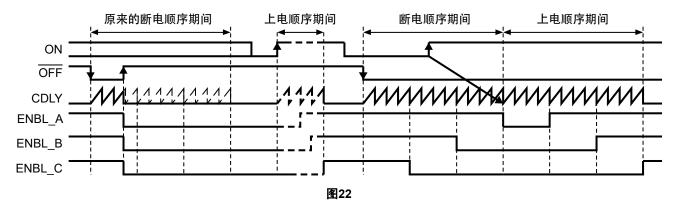

### (2) 在断电顺序期间OFF端子或ON端子从 "L" 变为 "H" 时

在断电顺序期间,若 $\overline{OFF}$ 端子从 "L" 变为 "H", $ENBL_x$ 端子会全部变为 "L",此时不能保证断电顺序的时序。另外, $C_{DLY}$ 的充电工作会被中止,并开始进行深度放电工作。在断电顺序期间,若ON端子从 "L" 变为 "H",在断电顺序完成后会开始进行上电顺序。工作例如**图22**所示。

备注 有关深度放电工作,请参阅 "■ 延迟时间与外接电容器的关系" 的 "3. 深度放电时间 (tochg) 的概略计算公式"。

#### 3.2.2 检测出低电压时的工作

### (1) 在电源安定期间检测出低电压时

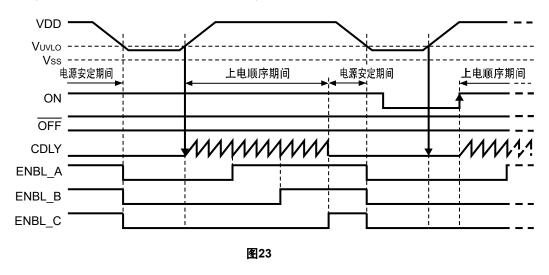

当电源电压 (V<sub>DD</sub>) 小于或等于低电压检测电压 (V<sub>UVLO</sub>) 时,ENBL\_x端子会全部变为 "L",此时不能保证断电顺序的时序。此后,当V<sub>DD</sub>超过V<sub>UVLO</sub>时,若ON端子为 "H",则自动地进行上电顺序。当V<sub>DD</sub>超过V<sub>UVLO</sub>时,若ON端子为 "L",则不进行上电顺序。为了进行上电顺序,请再次将ON端子设定为 "H"。工作例如**图23**所示。

### (2) 在上电顺序期间、断电顺序期间检测出低电压时

在上电顺序期间或断电顺序期间,若VDD小于或等于VUVLO,ENBL\_x端子会全部变为 "L",此时不能保证断电顺序的时序。另外,CDLY的充电工作会被中止,并开始进行深度放电工作。工作例如图24所示。

备注 有关深度放电工作,请参阅 "■ 延迟时间与外接电容器的关系"的 "3. 深度放电时间 (tdchg) 的概略计算公式"。

### 3. 2. 3 连接VDD端子、ON端子、OFF端子时的工作

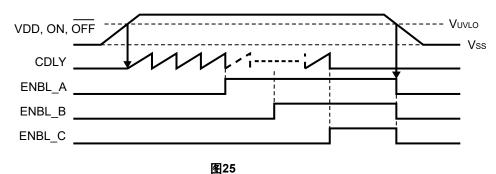

连接VDD端子、ON端子、OFF端子,电源电压上升后,会自动地进行上电顺序。但是,在电源电压下降时,若V<sub>DD</sub>小于或等于V<sub>UVLO</sub>,ENBL\_x端子会全部变为 "L",此时不能保证断电顺序的时序。工作例如**图25**所示。

23

### ■ ON端子、OFF端子的输入

### 1. 输入电位 (可以选项)

S-77100系列的ON端子、S-77101系列的ON端子和 $\overline{\text{OFF}}$ 端子的输入电位可选择下述2种选项。

#### 1.1 施密特触发输入

施密特触发输入的输入电平会受电源电压的影响。有关输入电压,请参阅 **"■ 电气特性"**。

#### 1.2 比较器输入

比较器输入的输入阈值几乎不受电源电压的影响。因此,也可通过低电压微控制器的I/O接口来进行顺序控制工作。有关比较器输入的输入阈值电压,请参阅 **"■ 电气特性"**。

### 2. 脉冲幅度

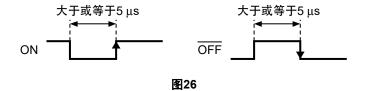

为了切实地对S-77100/77101系列输入信号,请对ON端子以及 $\overline{\text{OFF}}$ 端子输入大于或等于5  $\mu$ s的脉冲幅度。

### ■ 延迟时间与外接电容器的关系

S-77100/77101系列可使用外接电容器 ( $C_{DLY}$ ) 设定延迟时间 ( $t_{DLY}$ )。通过 $C_{DLY}$ 的充放电工作可生成 $t_{DLY}$ 。

图27

### 1. toly的概略计算公式

tDLY可通过下述概略计算公式算出。

C<sub>DLY</sub>≤1 nF时

t<sub>DLY</sub> [ms] = (1.206 × C<sub>DLY</sub> [nF] + 0.023) × 充放电次数

C<sub>DLY</sub>>1 nF时

t<sub>DLY</sub> [ms] = (1.155 × C<sub>DLY</sub> [nF] - 0.023) × 充放电次数

### 2. 延迟时间偏移量(tdly\_offset) 的概略计算公式

如**图27**所示,在断电期间和电源安定期间的CDLY端子被放电到Vss电位。因此,从断电期间进入到上电顺序期间、或从电源安定期间进入到断电顺序期间时,会有延迟时间偏移量( $t_{DLY\_OFFSET}$ )。

tdly\_offset因Cdly的容量值的不同而发生变化。tdly\_offset可按下述概略计算公式算出。

C<sub>DLY</sub>≤1 nF时

$t_{\text{DLY\_OFFSET}} \text{ [ms]} = 0.241 \times C_{\text{DLY}} \text{ [nF]} - 0.024$

C<sub>DLY</sub>>1 nF时

$t_{\text{DLY\_OFFSET}} \text{ [ms]} = 0.299 \times C_{\text{DLY}} \text{ [nF]} - 0.150$

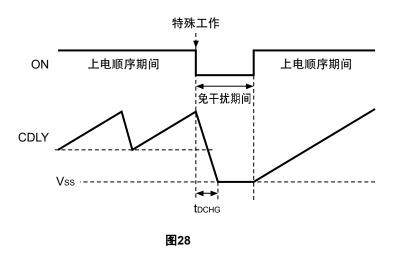

### 3. 深度放电时间 (tDCHG) 的概略计算公式

深度放电工作是指释放CDLY残留电荷的工作。 充放电工作完成后,通过定电流电路进行深度放电工作。

S-77100/77101系列的深度放电工作,在以下情况下进行。

- ・在上电顺序期间ON端子发生变化时 (请参阅图28)

- ·上电顺序期间结束时

- ・在断电顺序期间ON端子发生变化时 (仅限S-77100系列)

- ・在断电顺序期间OFF端子发生变化时 (仅限S-77101系列)

- ・断电顺序期间结束时

- ・在上电顺序期间或断电顺序期间VDD小于或等于VUVLO时

tDCHG因CDLY的容量值的不同而发生变化。tDCHG可按下述概略计算公式算出。

$t_{DCHG}$  [ms] =  $0.219 \times C_{DLY}$  [nF]

S-77100/77101系列从进行深度放电工作开始到上电顺序或断电顺序开始为止的期间称为 "免干扰期间"。免干扰期间应大于或等于tochg。为了Coly的电荷能够完全放电,并正常开始下一个的上电顺序或断电顺序,免干扰期间是必不可少的。另外,在顺序控制工作时,使电源安定期间以及断电期间大于或等于tochg,下一个的断电顺序期间以及上电顺序期间即可成为期待的时间长度。

- 注意 1. C<sub>DLY</sub>可使用100 pF ~ 47 nF的电容器。由于CDLY端子的内部阻抗高、容易受到外部的噪声等的影响,因此,请尽量将C<sub>DLY</sub>配置在靠近S-77100/77101系列之处。

- 2. 由于tdly、tdly\_offset、tdchg受到CDLY端子的寄生容量或IC的内部延迟的影响,有可能与计算公式的结果不符合。 使用时请在进行充分的实测后再决定Cdly的值。

**备注** 上述均为Ta = +25°C时的概略计算公式。

### ■ 接通电源

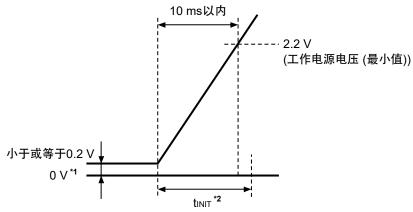

在电源电压上升时,S-77100/77101系列可通过上电复位电路进行初始化。如果没有正常地进行初始化则可能引发错误工作。为了使上电复位电路能够正常地工作,请按照以下方法提升电源电压。

### 1. 电源电压上升方法

如**图29**所示,请从小于或等于0.2 V电压值开始提升电源电压。另外,请将达到工作电源电压(最小值)为止的时间控制在10 ms以内。

- \*1. 0 V表示S-77100/77101系列的VDD端子与VSS端子之间没有电位差。

- \*2. 初始化的时间 (t<sub>INIT</sub>) 表示S-77100/77101系列在内部进行初始化的时间。在此期间内,S-77100/77101系列不能接受输入信号。详情请参阅 "2. 初始化时间"。

图29

若通过上电复位电路正常地结束初始化,S-77100/77101系列的ON端子为 "L" 时进入断电期间、ON端子为 "H" 时进入上电顺序期间。无法满足上电复位电路的工作条件时,由于S-77100/77101系列无法进行初始化,因此可能导致错误工作。工作不稳定时,请将电源电压降低到Vss电位来满足图29的条件,此后再提升电源电压。

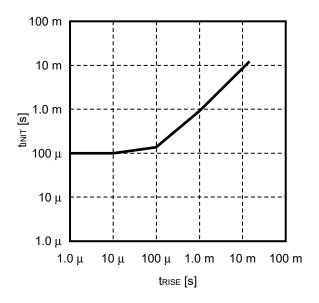

## 2. 初始化时间

在电源电压上升时,S-77100/77101系列进行初始化。在进行初始化期间,S-77100/77101系列的ON端子和 $\overline{OFF}$ 端子不能接受输入信号。S-77100/77101系列的初始化时间( $t_{INIT}$ )和电源电压上升( $0~V \rightarrow 2.2~V$ )时间( $t_{RISE}$ )的关系如**图30** 所示。

图30

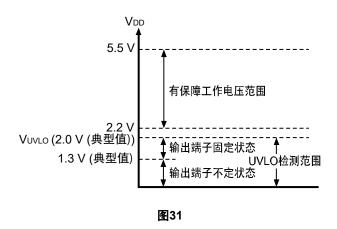

### ■ UVLO (欠压锁定) 工作

电源电压范围和输出端子的状态如图31所示。

S-77100/77101系列在电源电压  $(V_{DD})$  小于或等于1.3 V (典型值) 时,不能保证输出端子的状态。当 $V_{DD}$ 上升并超过1.3 V (典型值),输出端子的状态会被固定。

在 $V_{DD}$ 小于或等于 $V_{UVLO}$ 时,顺序控制工作变为无效。当 $V_{DD}$ 超过 $V_{UVLO}$ 后进入工作电压范围,但电源顺序控制器的有保障工作电压范围为2.2 V ~ 5.5 V。

### ■ 注意事项

- 本IC虽内置了防静电保护电路,但请不要对IC施加超过保护电路性能的过大静电。

- 使用本公司的IC生产产品时,如因其产品中对该IC的使用方法或产品的规格、或因进口国等原因,使包括本IC产品在内的制品发生专利纠纷时,本公司概不承担相应责任。

### ■ 各种特性数据 (典型数据)

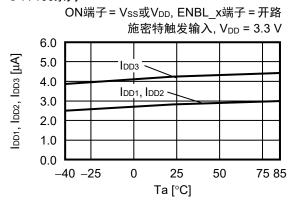

### 1. 消耗电流1, 消耗电流2, 消耗电流3

#### 1.1 消耗电流 - 电源电压

S-77100系列

ON端子= Vss或VDD, ENBL x端子=开路 施密特触发输入, Ta = +25°C 6.0 οσι, Ιοσ2, Ιοσ3 [μΑ] 5.0 IDD3 4.0 IDD1, IDD2~ 3.0 2.0 1.0 0.0 2 3 5 6 VDD [V]

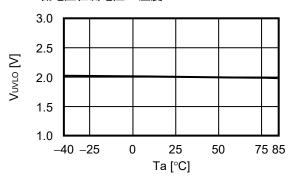

### 2. 低电压检测电压

### 2.1 低电压检测电压 - 温度

### 3. 高电位输入泄漏电流、低电位输入泄漏电流

### 3.1 输入泄漏电流 - 电源电压

ON端子, OFF端子\*1, VIN = VDD (IIZH), VIN = VSS (IIZL) Ta = +25°C 0.3 0.2 0.2 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | 0.1 | lizh, lizl -0.2-0.0 2 3 5 0 6 VDD [V]

### \*1. 仅限S-77101系列

#### 1.2 消耗电流 - 温度

S-77100系列

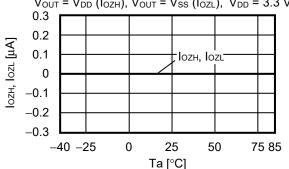

### 3.2 输入泄漏电流 - 温度

ON端子, OFF端子\*1, V<sub>IN</sub> = V<sub>DD</sub> (I<sub>IZH</sub>), V<sub>IN</sub> = V<sub>SS</sub> (I<sub>IZL</sub>)  $V_{DD} = 3.3 V$ 0.3 0.2 IZH, IIZL [µA] 0.1 JIZH, IIZL 0 -0.1-0.2-0.325 -40 -250 50 75 85 Ta [°C]

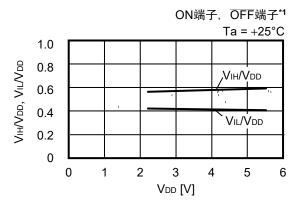

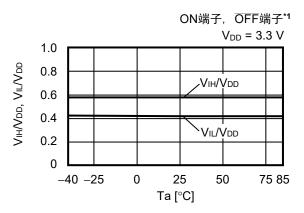

### 4. 输入电压 (选择施密特触发输入时)

### 4.1 输入电压 - 电源电压

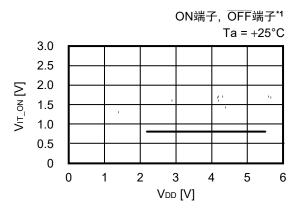

### 5. 输入阈值电压 (选择比较器输入时)

### 5.1 输入阈值电压 - 电源电压

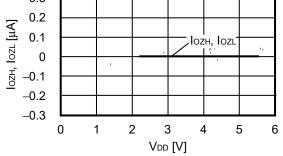

### 6. 高电位输出泄漏电流、低电位输出泄漏电流

### 6.1 输出泄漏电流 - 电源电压

ENBL A端子, ENBL B端子, ENBL C端子, ENBL D端子\*2  $V_{OUT} = V_{DD} (I_{OZH}), V_{OUT} = V_{SS} (I_{OZL}), Ta = +25^{\circ}C$ 0.3 0.2 0.1 .lozн, lozu

- 仅限S-77101系列 \*1.

- \*2. 仅限S-77100系列

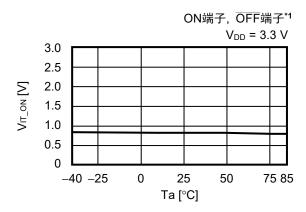

#### 4.2 输入电压 - 温度

### 5.2 输入阈值电压 - 温度

#### 6.2 输出泄漏电流 - 温度

ENBL A端子, ENBL B端子, ENBL C端子, ENBL D端子\*2  $V_{OUT} = V_{DD} (I_{OZH}), V_{OUT} = V_{SS} (I_{OZL}), V_{DD} = 3.3 \text{ V}$

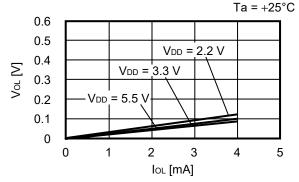

### 7. 低电位输出电压

#### 7.1 低电位输出电压 - 低电位输出电流

ENBL\_A端子, ENBL\_B端子, ENBL\_C端子, ENBL\_D端子\*1

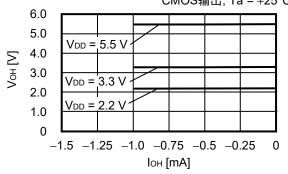

### 8. 高电位输出电压

### 8.1 高电位输出电压 - 高电位输出电流

ENBL\_A端子, ENBL\_B端子, ENBL\_C端子, ENBL\_D端子\*1 CMOS輸出, Ta = +25°C

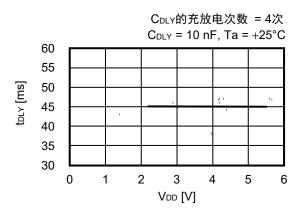

### 9. 延迟时间

#### 9.1 延迟时间 - 电源电压

### \*1. 仅限S-77100系列

#### 7.2 低电位输出电压 - 温度

ENBL\_A端子, ENBL\_B端子, ENBL\_C端子, ENBL\_D端子\*1 IoL = 2.0 mA

### 8.2 高电位输出电压 – 温度

ENBL\_A端子, ENBL\_B端子, ENBL\_C端子, ENBL\_D端子\*1 CMOS输出, I<sub>OH</sub> = -0.4 mA

#### 9.2 延迟时间 - CDLY

# No. FT008-A-P-SD-1.2

| TITLE      | TSSOP8-E-PKG Dimensions |  |

|------------|-------------------------|--|

| No.        | FT008-A-P-SD-1.2        |  |

| ANGLE      | <b>\$</b> \displaystart |  |

| UNIT       | mm                      |  |

|            |                         |  |

|            |                         |  |

|            |                         |  |

| ABLIC Inc. |                         |  |

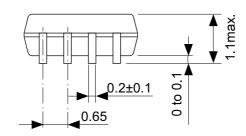

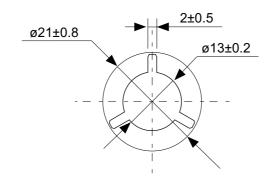

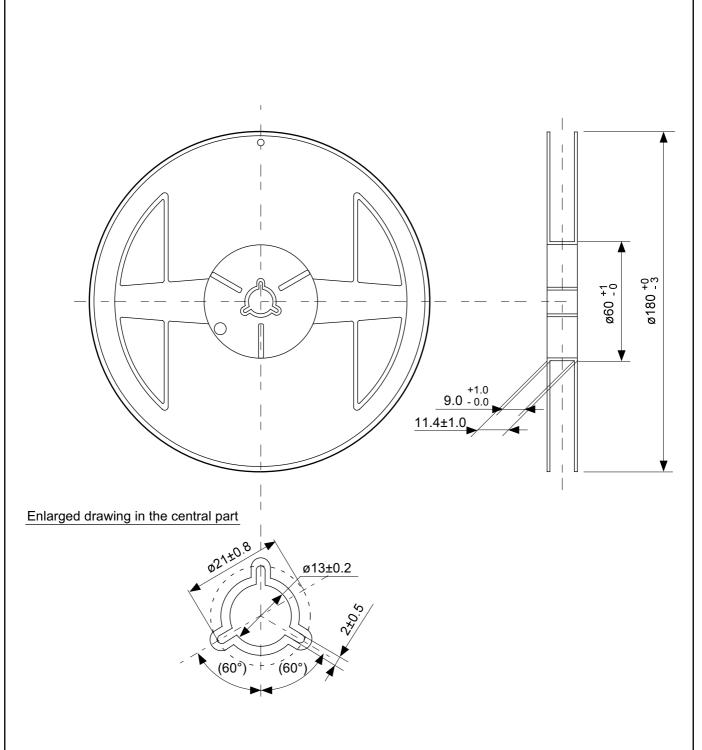

## No. FT008-E-C-SD-1.0

| TITLE      | TSSOP8-E-Carrier Tape |  |  |

|------------|-----------------------|--|--|

| No.        | FT008-E-C-SD-1.0      |  |  |

| ANGLE      |                       |  |  |

| UNIT       | mm                    |  |  |

|            |                       |  |  |

|            |                       |  |  |

|            |                       |  |  |

| ABLIC Inc. |                       |  |  |

# Enlarged drawing in the central part

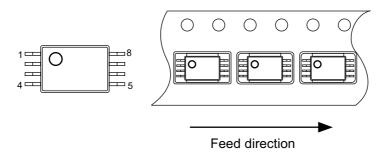

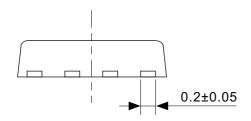

# No. FT008-E-R-S1-2.0

| TITLE      | TSSO  | P8-E-R           | eel   |  |  |

|------------|-------|------------------|-------|--|--|

| No.        | FT008 | FT008-E-R-S1-2.0 |       |  |  |

| ANGLE      |       | QTY.             | 4,000 |  |  |

| UNIT       | mm    |                  |       |  |  |

|            |       |                  |       |  |  |

|            |       |                  |       |  |  |

|            |       |                  |       |  |  |

| ABLIC Inc. |       |                  |       |  |  |

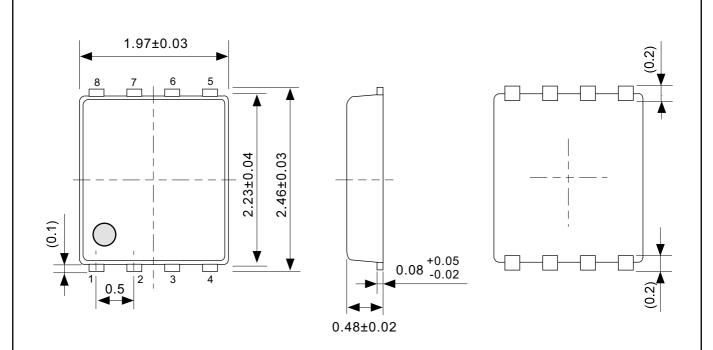

# No. PH008-A-P-SD-2.1

| TITLE      | SNT-8A-A-PKG Dimensions |  |

|------------|-------------------------|--|

| No.        | PH008-A-P-SD-2.1        |  |

| ANGLE      | <b>\$</b>               |  |

| UNIT       | mm                      |  |

|            |                         |  |

|            |                         |  |

|            |                         |  |

| ABLIC Inc. |                         |  |

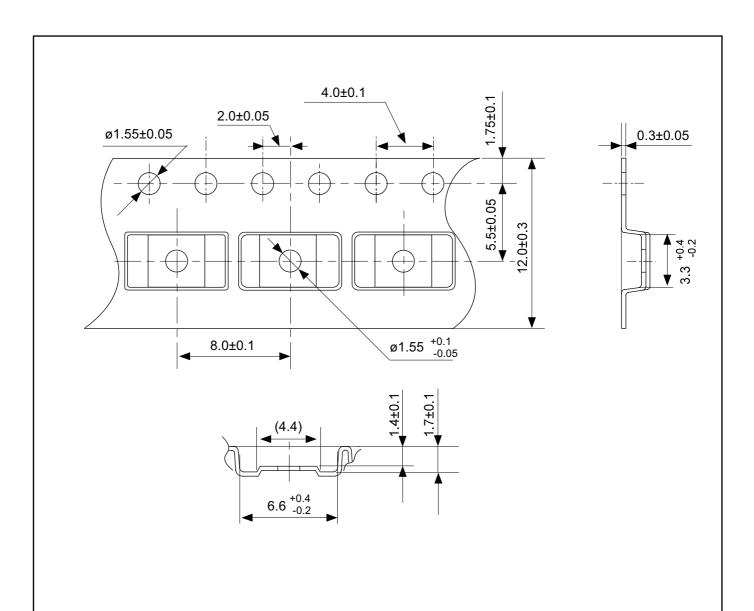

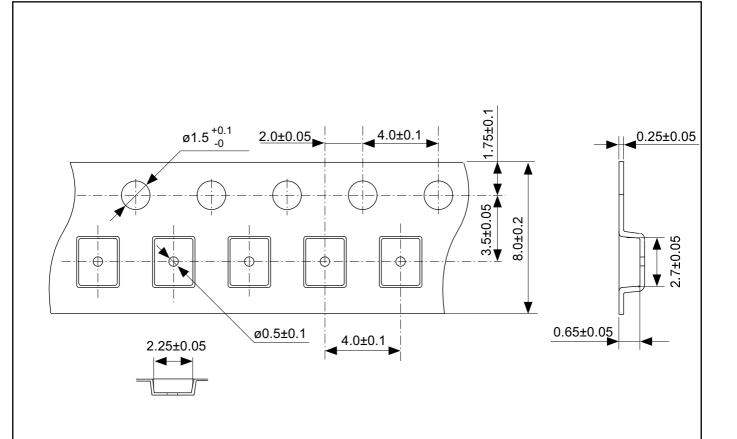

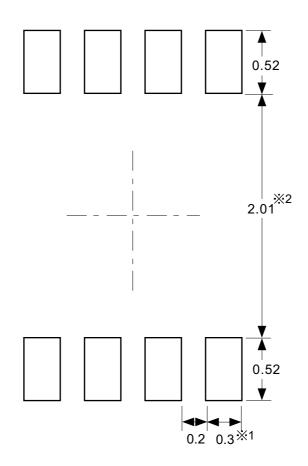

## No. PH008-A-C-SD-2.0

| TITLE      | SNT-8A-A-Carrier Tape |  |

|------------|-----------------------|--|

| No.        | PH008-A-C-SD-2.0      |  |

| ANGLE      |                       |  |

| UNIT       | mm                    |  |

|            |                       |  |

|            |                       |  |

|            |                       |  |

| ABLIC Inc. |                       |  |

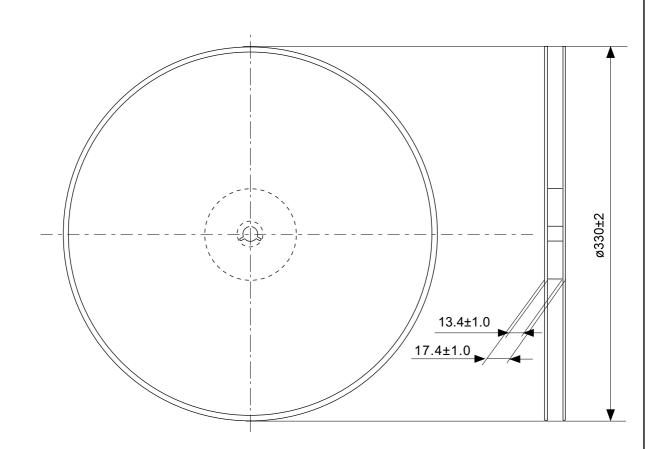

# No. PH008-A-R-SD-2.0

| TITLE      | SNT-8A-A-Reel    |      |       |

|------------|------------------|------|-------|

| No.        | PH008-A-R-SD-2.0 |      |       |

| ANGLE      |                  | QTY. | 5,000 |

| UNIT       | mm               |      |       |

|            |                  |      |       |

|            |                  |      |       |

|            |                  |      |       |

| ABLIC Inc. |                  |      |       |

- ※1. ランドパターンの幅に注意してください (0.25 mm min. / 0.30 mm typ.)。 ※2. パッケージ中央にランドパターンを広げないでください (1.96 mm ~ 2.06 mm)。

- 注意 1. パッケージのモールド樹脂下にシルク印刷やハンダ印刷などしないでください。

- 2. パッケージ下の配線上のソルダーレジストなどの厚みをランドパターン表面から0.03 mm 以下にしてください。

- 3. マスク開口サイズと開口位置はランドパターンと合わせてください。

- 4. 詳細は "SNTパッケージ活用の手引き"を参照してください。

- X1. Pay attention to the land pattern width (0.25 mm min. / 0.30 mm typ.).

- \*2. Do not widen the land pattern to the center of the package (1.96 mm to 2.06mm).

- Caution 1. Do not do silkscreen printing and solder printing under the mold resin of the package.

- 2. The thickness of the solder resist on the wire pattern under the package should be 0.03 mm or less from the land pattern surface.

- 3. Match the mask aperture size and aperture position with the land pattern.

- 4. Refer to "SNT Package User's Guide" for details.

- ※1. 请注意焊盘模式的宽度 (0.25 mm min. / 0.30 mm typ.)。

- ※2. 请勿向封装中间扩展焊盘模式 (1.96 mm~2.06 mm)。

- 注意 1. 请勿在树脂型封装的下面印刷丝网、焊锡。

- 2. 在封装下、布线上的阻焊膜厚度 (从焊盘模式表面起) 请控制在 0.03 mm 以下。

- 3. 钢网的开口尺寸和开口位置请与焊盘模式对齐。

- 4. 详细内容请参阅 "SNT 封装的应用指南"。

No. PH008-A-L-SD-4.1

| TITLE      | SNT-8A-A<br>-Land Recommendation |  |

|------------|----------------------------------|--|

| No.        | PH008-A-L-SD-4.1                 |  |

| ANGLE      |                                  |  |

| UNIT       | mm                               |  |

|            |                                  |  |

|            |                                  |  |

|            |                                  |  |

| ABLIC Inc. |                                  |  |

### 免责事项 (使用注意事项)

- 1. 本资料记载的所有信息 (产品数据、规格、图、表、程序、算法、应用电路示例等) 是本资料公开时的最新信息,有可能未经预告而更改。

- 2. 本资料记载的电路示例和使用方法仅供参考,并非保证批量生产的设计。使用本资料的信息后,发生并非因本资料记载的产品(以下称本产品)而造成的损害,或是发生对第三方知识产权等权利侵犯情况,本公司对此概不承担任何责任。

- 3. 因本资料记载错误而导致的损害,本公司对此概不承担任何责任。

- 4. 请注意在本资料记载的条件范围内使用产品,特别请注意绝对最大额定值、工作电压范围和电气特性等。 因在本资料记载的条件范围外使用产品而造成的故障和(或)事故等的损害,本公司对此概不承担任何责任。

- 5. 在使用本产品时,请确认使用国家、地区以及用途的法律、法规,测试产品用途的满足能力和安全性能。

- 6. 本产品出口海外时,请遵守外汇交易及外国贸易法等的出口法令,办理必要的相关手续。

- 7. 严禁将本产品用于以及提供(出口)于开发大规模杀伤性武器或军事用途。对于如提供(出口)给开发、制造、使用或储藏核武器、生物武器、化学武器及导弹,或有其他军事目的者的情况,本公司对此概不承担任何责任。

- 8. 本产品并非是设计用于可能对生命、人体造成影响的设备或装置的部件,也非是设计用于可能对财产造成损害的设备或装置的部件(医疗设备、防灾设备、安全防范设备、燃料控制设备、基础设施控制设备、车辆设备、交通设备、车载设备、航空设备、太空设备及核能设备等)。请勿将本产品用于上述设备或装置的部件。本公司事先明确标示的车载用途例外。作为上述设备或装置的部件使用本产品时,或本公司事先明确标示的用途以外使用本产品时,所导致的损害,本公司对此概不承担任何责任。

- 9. 半导体产品可能有一定的概率发生故障或误工作。为了防止因本产品的故障或误工作而导致的人身事故、火灾事故、社会性损害等,请客户自行负责进行冗长设计、防止火势蔓延措施、防止误工作等安全设计。并请对整个系统进行充分的评价,客户自行判断适用的可否。

- 10. 本产品非耐放射线设计产品。请客户根据用途,在产品设计的过程中采取放射线防护措施。

- 11. 本产品在一般的使用条件下,不会影响人体健康,但因含有化学物质和重金属,所以请不要将其放入口中。另外,晶元和芯片的破裂面可能比较尖锐,徒手接触时请注意防护,以免受伤等。

- 12. 废弃本产品时,请遵守使用国家和地区的法令,合理地处理。

- 13. 本资料中也包含了与本公司的著作权和专有知识有关的内容。本资料记载的内容并非是对本公司或第三方的知识产权、 其它权利的实施及使用的承诺或保证。严禁在未经本公司许可的情况下转载、复制或向第三方公开本资料的一部分或全 部。

- 14. 有关本资料的详细内容等如有不明之处,请向代理商咨询。

- 15. 本免责事项以日语版为正本。即使有英语版或中文版的翻译件, 仍以日语版的正本为准。

2.4-2019.07